一种RISCV中断跳转电路的制作方法

本技术涉及处理器中断处理,具体涉及一种riscv中断跳转电路。

背景技术:

1、中断机制是现代计算机系统中的基本机制之一,它在系统中起着通信网络的作用,以协调系统对各种外部事件的响应和处理。中断是实现多道程序设计的必要条件,它是cpu对系统某个时刻发生的某个事件做出的一种反应,即,处理器核在顺序执行程序指令流的过程中被突发请求打断而中止执行当前的程序,转而去处理别的程序,待其处理完了别的程序返回中断点继续执行此前的程序。引起中断的事件称为中断源,通常情况下,中断源主要来自外围硬件设备。

2、在现有技术中,如riscv处理器发生中断时,先比较中断向量寄存器的向量号和跳转地址,然后根据这些信息,确定处理器跳转到哪部分电路开始实现中断功能,至少需要使用3个32位寄存器(mie中断使能寄存器、mtvec中断向量寄存器和mcause中断原因寄存器),这个多开销了芯片面积。如申请号为201910198363.3,专利名称为《用于risc-v架构的中断系统》的发明申请,即采用了此类方案。

技术实现思路

1、本实用新型的目的在于提供一种不多开销寄存器,以利于缩小芯片面积的riscv中断跳转电路。

2、为实现上述目的,本实用新型采用以下技术方案:

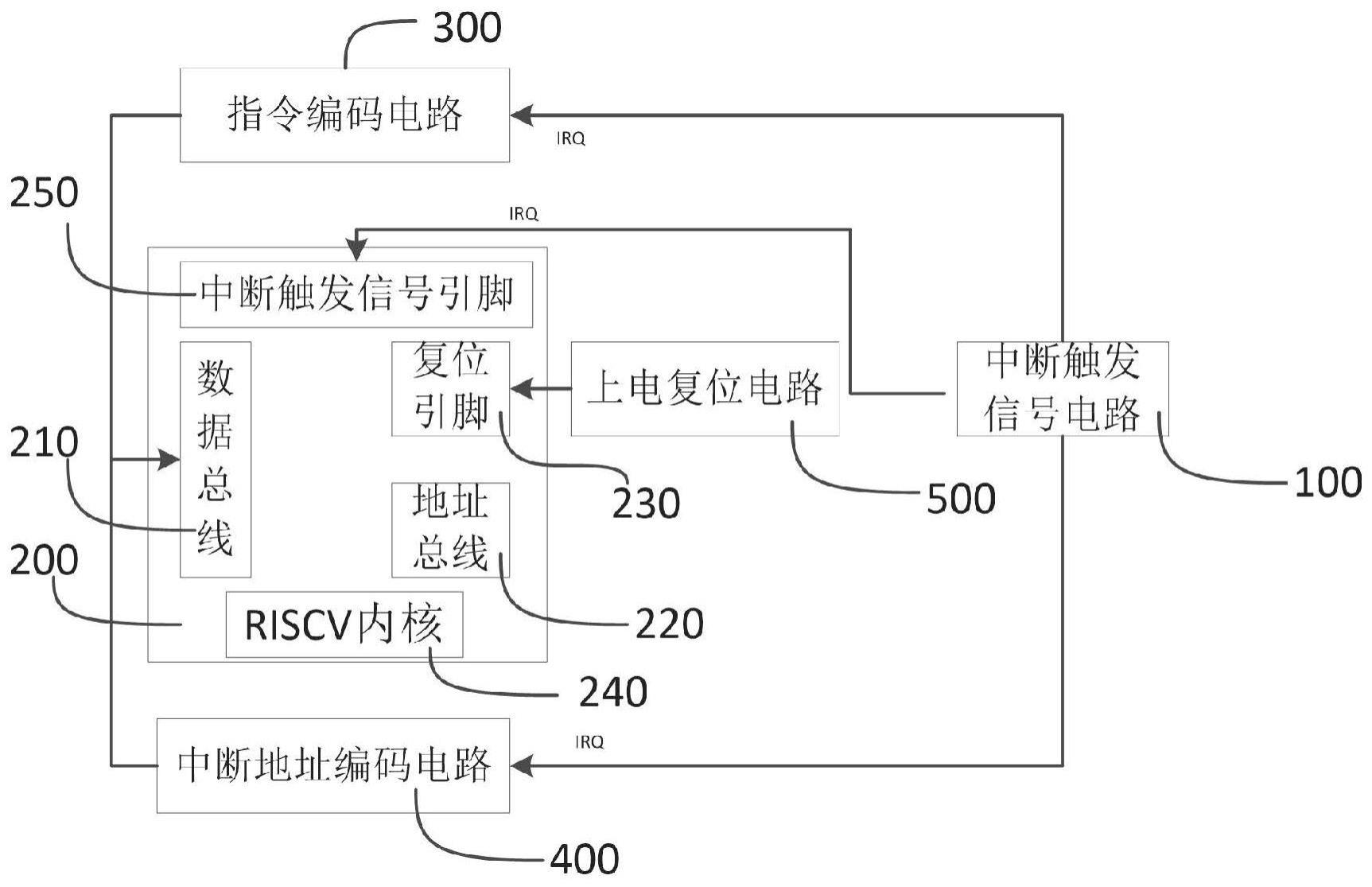

3、一种riscv处理器的中断跳转电路,其包括riscv处理器,所述riscv处理器包括riscv内核、地址总线、数据总线、中断触发信号引脚,其还包括:

4、jalr指令编码电路,所述jalr指令编码电路包括依次设置的5个指令编码传输门,各指令编码传输门的控制端同时连接所述中断触发信号引脚,各指令编码传输门的输入分别连接固定电平,以呈11001电平编码分布,各指令编码传输门的输出连接所述数据总线;

5、中断入口地址编码电路,所述中断入口地址编码电路包括依次设置的若干个地址编码传输门,各地址编码传输门的控制端同时连接所述中断触发信号引脚,各地址编码传输门的输入分别连接固定电平以呈唯一地址编码分布,各地址编码传输门的输出连接所述数据总线;

6、当所述riscv处理器接收所述jalr指令编码电路的指令时,将所述中断入口地址编码电路的地址编码赋给所述地址总线并跳转。

7、进一步地,各指令编码传输门连接所述数据总线的第6:2位,各地址编码传输门的输出连接所述数据总线的第30:22位。

8、进一步地,所述5个指令编码传输门包括第一指令编码传输门、第二指令编码传输门、第三指令编码传输门、第四指令编码传输门及第五指令编码传输门,所述第一指令编码传输门、第二指令编码传输门及第五指令编码传输门的输入分别接电源,所述第三指令编码传输门及第四指令编码传输门的输入接地,以呈11001电平编码分布。

9、进一步地,所述地址编码传输门的个数为9个,与所述riscv处理器程序空间的中断入口地址唯一对应。

10、采用上述技术方案后,本实用新型与背景技术相比,具有如下优点:

11、本实用新型充分利用riscv处理器的固有指令jalr和外围jalr指令编码电路及中断入口地址编码电路,从硬件上对jalr跳转指令和中断入口地址进行识别,从而实现中断功能。该电路方便集成到芯片中,不多开销寄存器,利于缩小芯片面积,而且实现处理器点对点精确执行中断功能。

技术特征:

1.一种riscv中断跳转电路,其包括riscv处理器,所述riscv处理器包括riscv内核、地址总线、数据总线、中断触发信号引脚,其特征在于,还包括:

2.如权利要求1所述的一种riscv中断跳转电路,其特征在于:各指令编码传输门连接所述数据总线的第6:2位,各地址编码传输门的输出连接所述数据总线的第30:22位。

3.如权利要求1所述的一种riscv中断跳转电路,其特征在于:所述5个指令编码传输门包括第一指令编码传输门、第二指令编码传输门、第三指令编码传输门、第四指令编码传输门及第五指令编码传输门,所述第一指令编码传输门、第二指令编码传输门及第五指令编码传输门的输入分别接电源,所述第三指令编码传输门及第四指令编码传输门的输入接地,以呈11001电平编码分布。

4.如权利要求1所述的一种riscv中断跳转电路,其特征在于:所述地址编码传输门的个数为9个,与所述riscv处理器的程序空间的中断入口地址唯一对应。

技术总结

本技术公开了一种RISCV中断跳转电路,包括RISCV处理器、JALR指令编码电路及中断入口地址编码电路。JALR指令编码电路包括依次设置的5个指令编码传输门,各指令编码传输门的控制端同时连接中断触发信号引脚,输入分别连接固定电平,以呈11001电平编码分布,输出连接数据总线;中断入口地址编码电路包括依次设置的若干个地址编码传输门,各地址编码传输门的控制端同时连接中断触发信号引脚,输入分别连接固定电平以呈唯一地址编码分布,输出连接数据总线;当RISCV处理器接收JALR指令编码电路的指令时,将中断入口地址编码电路的地址编码赋给地址总线并跳转。本技术方便集成到芯片中,不多开销寄存器,利于缩小芯片面积。

技术研发人员:柴智,韦剑,陈为斌,张云

受保护的技术使用者:厦门芯矽望集成电路技术有限公司

技术研发日:20230321

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!