一种基于RISC-V的芯片及包含该芯片的口袋实验室

本技术涉及数据处理设备领域,具体涉及一种基于risc-v的芯片及包含该芯片的口袋实验室。

背景技术:

1、示波器被称为是电子工程师的双眼,而示波器的采集速度决定了电子工程师能看多远,而为了采集更高速的模拟信号,adc(模拟数字转换器)与处理器之间需要巨大带宽进行通信,因而adc的通信接口不得不采用并口,但常见的处理器都是串行信号处理的结构,这就决定了它们无法高速地进行并口通信。

2、目前有两种解决串行通信处理器并口通信问题的技术,第一种方案采用特定转换芯片,先将处理器的串口转换成并口的仪器,但该方案只是实现了串行处理器的并行通信问题,并未解决高带宽的问题,因为处理器与转换芯片之间的通信也是需要极高的带宽,市场上这类仪器往往速率低,在模拟信号采集方面则体现在采样率低,且由于额外芯片的加入,导致成本增加;第二种方案为使用昂贵的fpga(现场可编程门阵列)进行数据的并行接收,不仅需要更高的硬件成本,同时软件也需要专门的人员来开发fpga,因此市场上这类仪器的售价较高,且由于fpga的加入,仪器笨重不便携带,功耗较高,基本无法通过电池供电,也无法随身携带使用。

技术实现思路

1、为了克服上述现有技术的缺点,本实用新型的目的在于提供一种基于risc-v的芯片及包含该芯片的口袋实验室,芯片通过在系统总线上添加高速并口,使芯片得以高速并口通信,口袋实验室通过添加高速并口后的芯片与高速adc与dac模块连接进行指令发送,本实用新型具有通信速度快,体积小巧,便于携带,采样率高,通信带宽高,成本低以及功耗低的优点。

2、为了实现上述目的,本实用新型采用的技术方案是:

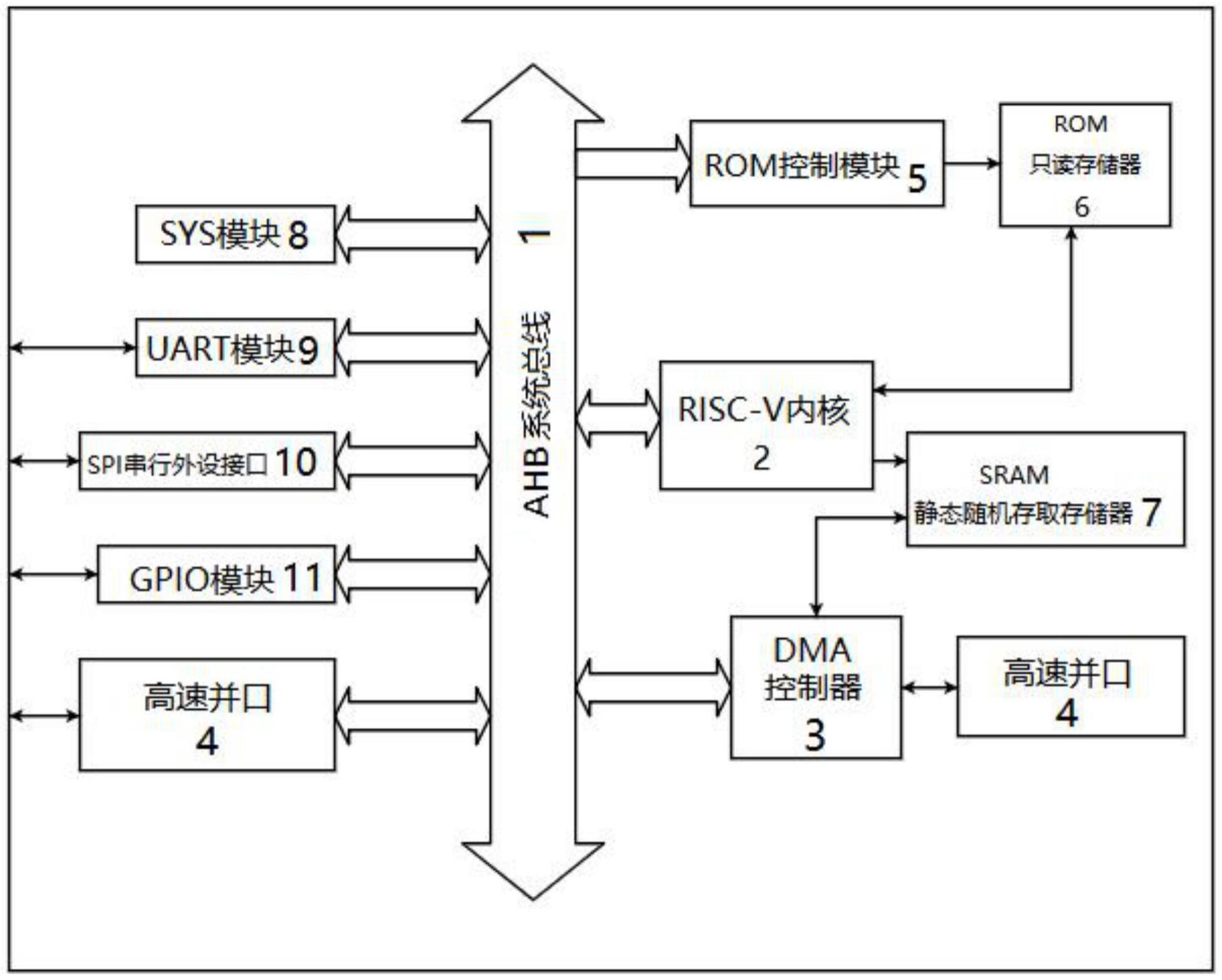

3、一种基于risc-v的芯片,包括ahb系统总线1,所述ahb系统总线1分别与risc-v内核2以及dma控制器3双向信号连接,所述ahb系统总线1与一侧的高速并口4双向信号连接,所述dma控制器3与另一侧的高速并口4双向信号连接,所述ahb系统总线1的信号输出端与rom控制模块5的信号输入端连接,所述rom控制模块5的信号输出端与rom只读存储器6的信号输入端连接,所述rom只读存储器6与risc-v内核2双向信号连接;所述risc-v内核2的信号输出端与sram静态随机存取存储器7的信号输入端连接,所述sram静态随机存取存储器7与dma控制器3双向信号连接。

4、所述ahb系统总线1分别与sys模块8、uart模块9、spi串行外设接口10以及gpio模块11双向信号连接。

5、一种包含基于risc-v的芯片的口袋实验室,包括基于risc-v的芯片12,所述基于risc-v的芯片12通过多个并行数据接口13分别与高速adc模块14与高速dac模块15双向信号连接,所述基于risc-v的芯片12通过spi串行外设接口10与eth模块16双向信号连接,所述eth模块16通过tcp传输控制协议17与服务器18双向信号连接,所述服务器18通过tcp传输控制协议17与pc端19双向信号连接。

6、相对于现有技术,本实用新型的有益效果在于:

7、1.通过在ahb系统总线1上设置多个高速并口4,以及在基于risc-v的芯片12上设置多个并行数据接口13,使得本实用新型的通信速度获得提升。

8、2.通过增加并行数据接口13,使得基于risc-v的芯片12无需增加外置的并口芯片,不但减少了开发外置并口芯片的成本,而且使得本实用新型体积小巧,便于携带。

9、3.通过在基于risc-v的芯片12增加高速并口4,减少了因增加外置并口芯片产生的电路功耗,且基于risc-v的芯片12可设置低功耗模式,可以进一步降低本实用新型的功耗。

10、4.通过设置高速并口4,使得本实用新型不仅能够驱动普通串行通信的adc模块,还能驱动高速并口adc模块,使得本实用新型具有采样率高的优点。

11、5.通过在基于risc-v的芯片12中增加高速并口4,使得基于risc-v的芯片12可以进行并口通信,使得本实用新型具有通信带宽高的优点。

技术特征:

1.一种基于risc-v的芯片,包括ahb系统总线(1),所述ahb系统总线(1)分别与risc-v内核(2)以及dma控制器(3)双向信号连接,其特征在于,所述ahb系统总线(1)与一侧的高速并口(4)双向信号连接,所述dma控制器(3)与另一侧的高速并口(4)双向信号连接,所述ahb系统总线(1)的信号输出端与rom控制模块(5)的信号输入端连接,所述rom控制模块(5)的信号输出端与rom只读存储器(6)的信号输入端连接,所述rom只读存储器(6)与risc-v内核(2)双向信号连接,所述risc-v内核(2)的信号输出端与sram静态随机存取存储器(7)的信号输入端连接,所述sram静态随机存取存储器(7)与dma控制器(3)双向信号连接。

2.根据权利要求1所述的一种基于risc-v的芯片,其特征在于,所述ahb系统总线(1)分别与sys模块(8)、uart模块(9)、spi串行外设接口(10)以及gpio模块(11)双向信号连接。

3.一种包含基于risc-v的芯片的口袋实验室,包括基于risc-v的芯片(12),其特征在于,所述基于risc-v的芯片(12)通过多个并行数据接口(13)分别与高速adc模块(14)与高速dac模块(15)双向信号连接,所述基于risc-v的芯片(12)通过spi串行外设接口(10)与eth模块(16)双向信号连接,所述eth模块(16)通过tcp传输控制协议(17)与服务器(18)双向信号连接,所述服务器(18)通过tcp传输控制协议(17)与pc端(19)双向信号连接。

技术总结

一种基于RISC‑V的芯片及包含该芯片的口袋实验室,基于RISC‑V的芯片包括AHB系统总线,分别与RISC‑V内核以及DMA控制器双向连接,AHB系统总线与DMA控制器分别和不同高速并口双向连接,AHB系统总线与ROM控制模块连接,ROM控制模块与ROM只读存储器连接,ROM只读存储器与RISC‑V内核双向连接,RISC‑V内核与SRAM静态随机存取存储器连接,SRAM静态随机存取存储器与DMA控制器连接;口袋实验室包括基于RISC‑V的芯片,通过并行数据接口分别与高速ADC模块与高速DAC模块双向连接,基于RISC‑V的芯片通过SPI串行外设接口与ETH模块双向连接,ETH模块通过TCP传输控制协议与服务器双向连接,服务器通过TCP传输控制协议与PC端连接。

技术研发人员:王洲行,魏仕荣,马航宇

受保护的技术使用者:西安电子科技大学

技术研发日:20230602

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!