PCIe多通道可编程测试治具的制作方法

本技术涉及编程测试治具,具体是pcie多通道可编程测试治具。

背景技术:

1、pcie(peripheral component interconnect express)是一种用于连接计算机内部各个组件的高速串行总线标准。pcie信号完整性测试是一项重要的过程,用于验证和确保pcie信号在系统中的传输质量和可靠性。随着计算机技术的快速发展,pcie信号完整性测试变得越来越重要。

2、pcie信号的完整性测试包括以下五个方面:一是提高带宽和速度:pcie标准不断演进,新的版本和规范发布,提供更高的带宽和数据传输速度;二是测试工具和设备:包括高频示波器、信号发生器、探头、测试治具等,其中,一些先进的设备还提供高级分析功能,如眼图分析、时钟恢复、串扰分析等;三是标准和规范:pci-sig(pcie special interestgroup)规范,包括物理层和传输层规范,这些规范为pcie信号完整性测试提供了指导和标准;四是仿真和建模:通过仿真和建模工具来辅助pcie信号完整性测试;五是数据分析和处理:pcie信号完整性测试生成大量的数据,需要进行有效的分析和处理,数据分析软件和算法的发展使工程师能够更好地理解信号特性、检测问题和改进设计。

3、然而,随着pcie信号完整性测试技术的不断进步,现有测试治具存在如下不足之处:当多通道测试时,各通道之间存在相互影响,导致多通道测试的传输损耗大,且存在信号传输串扰的问题。基于此,本实用新型设计了pcie多通道可编程测试治具,以解决上述问题。

技术实现思路

1、本实用新型的目的在于提供pcie多通道可编程测试治具,以解决上述提出的现有测试治具存在如下不足之处:当多通道测试时,各通道之间存在相互影响,导致多通道测试的传输损耗大,且存在信号传输串扰的问题。

2、为实现上述目的,本实用新型提供如下技术方案:

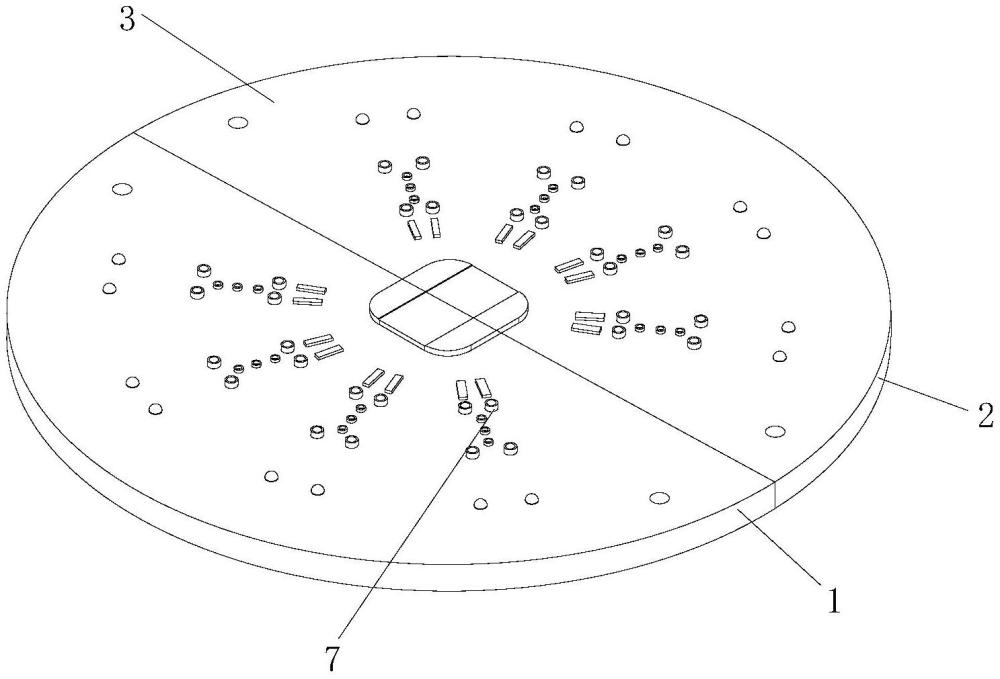

3、pcie多通道可编程测试治具,包括电路板,所述电路板包括接地层和屏蔽层,电路板的顶面连接有差分信号线路和控制信号线路,所述差分信号线路包括rx+线路、rx-线路、tx+线路和tx-线路,电路板还包括a板和b板,所述a板和b板通过扣紧件可拆卸连接组成,所述电路板的顶部设置有电路板a面,电路板的底部设置有电路板b面,所述电路板a面设置有若干对差分信号的sma接口公头,每对sma接口公头均包括两路接口,一路用于连接外部设备,另一路接地,电路板b面连接有两对sma接口母头,每个所述sma接口公头分别适配一个继电器,分别控制电路板b面的两对sma接口母头的通断,每个所述继电器的一端分别连接一个电阻r,待测物通过a面的差分信号tx+和tx-经过继电器输出到b面差分信号tx+和tx-信号再发送给测试仪,测试仪通过b面差分信号rx+和rx-经过继电器输出到a面的差分信号rx+和rx-再发送给待测物,形成一个待测物和测试仪的信号输入输出环回。

4、作为本实用新型进一步的方案:所述扣紧件包括开设在所述a板侧面的开口以及固定在所述b板侧面的卡块,卡块与所述开口适配卡接。

5、作为本实用新型进一步的方案:所述sma接口公头设置有八对,八对sma接口公头由四对rx和四对tx接口组构成,每对rx和每对tx接口分别组成一路环回信号,八对sma接口公头7共组成四路环回信号,且四路环回信号分别为lane0,lane1,lane2,lane3,每路回环信号分别由四个继电器来控制。

6、作为本实用新型进一步的方案:所述电阻r的阻值为50ω,电阻r为贴片式电阻。

7、作为本实用新型进一步的方案:所述差分信号和控制信号线路关于电路板的圆心呈圆周阵列排布,用于保证各线路的损耗和阻抗一致。

8、作为本实用新型进一步的方案:所述电路板的表面设置有屏蔽层和屏蔽孔,用于保护线路不受继电器的干扰,同时也限制线路与线路间的串扰。

9、作为本实用新型进一步的方案:所述继电器的上游连接有由两个32路串口控制的电源,通过外部连线整合成一个64路串口接入工控机,所述rx+线路、rx-线路、tx+线路和tx-线路的走线长度一致,用于确保信号的一致性和匹配性,所述每条差分信号线路分别与一个适配的屏蔽孔连接。

10、与现有技术相比,本实用新型的有益效果是:

11、1、本实用新型通过一块支持pcie多通道测试的可编程控制电路板,可降低pcie物理层接收端或发射端测试场景中的多通道测试耗时长,解决了测试治具易损坏的问题,同时降低了原有测试线路的传输损耗和串扰,通过50欧姆电阻的连接,可以确保差分信号的阻抗灵活匹配,减少信号损耗和反射,提高测试效率。

12、2、本实用新型通过支持pcie的4路差分信号通道的测试,测试过程中无需对这些线路进行插拔,提高测试效率,通过精确的差分信号配对和安装于测试治具上各个50欧姆电阻的匹配,保证了信号的完整性和一致性,提高了测试精度和可靠性,采用继电器控制差分信号通道的连通与否,可以通过控制继电器的开关状态灵活选择需要测试的通道,提供了更大的灵活性和定制化能力,电路板的设计和布局经过精心考虑,充分满足pcie多通道测试的需求,减少了不必要的功能和组件,降低了成本,采用贴片式高精度电阻,提高了制造效率和减少了装配成本,pcie的测试仪器昂贵,使用此种测试治具将大幅降低测试时间,节约测试费用。

技术特征:

1.pcie多通道可编程测试治具,包括电路板,电路板包括接地层和屏蔽层,电路板的顶面连接有差分信号线路和控制信号线路,其特征在于:所述差分信号线路包括rx+线路、rx-线路、tx+线路和tx-线路,电路板还包括a板(1)和b板(2),所述a板(1)和b板(2)通过扣紧件可拆卸连接组成,所述电路板的顶部设置有电路板a面(3),电路板的底部设置有电路板b面(4),所述电路板a面(3)设置有若干对差分信号的sma接口公头(7),电路板b面(4)连接有两对sma接口母头(8),每个所述sma接口公头(7)分别适配一个继电器,分别控制电路板b面(4)的两对sma接口母头(8)的通断,每个所述继电器的一端分别连接一个电阻r。

2.根据权利要求1所述的pcie多通道可编程测试治具,其特征在于:所述扣紧件包括开设在所述a板(1)侧面的开口(5)以及固定在所述b板(2)侧面的卡块(6),卡块(6)与所述开口(5)适配卡接。

3.根据权利要求1所述的pcie多通道可编程测试治具,其特征在于:所述sma接口公头(7)设置有八对,八对sma接口公头(7)由四对rx和四对tx接口组构成,每对rx和每对tx接口分别组成一路环回信号,八对sma接口公头(7)共组成四路环回信号,且四路环回信号分别为lane0,lane1,lane2,lane3,每路回环信号分别由四个继电器来控制。

4.根据权利要求1所述的pcie多通道可编程测试治具,其特征在于:所述电阻r的阻值为50ω,电阻r为贴片式电阻。

5.根据权利要求1所述的pcie多通道可编程测试治具,其特征在于:所述差分信号和控制信号线路关于电路板的圆心呈圆周阵列排布,用于保证各线路的损耗和阻抗一致。

6.根据权利要求3所述的pcie多通道可编程测试治具,其特征在于:所述电路板的表面设置有屏蔽层和屏蔽孔。

7.根据权利要求6所述的pcie多通道可编程测试治具,其特征在于:所述继电器的上游连接有由两个32路串口控制的电源,所述rx+线路、rx-线路、tx+线路和tx-线路的走线长度一致,所述每条差分信号线路分别与一个适配的屏蔽孔连接。

技术总结

本技术公开了编程测试治具技术领域的PCIe多通道可编程测试治具,包括电路板,所述电路板包括接地层和屏蔽层,电路板的顶面连接有差分信号线路和控制信号线路,所述差分信号线路包括Rx+线路、Rx‑线路、Tx+线路和Tx‑线路,电路板还包括A板和B板,所述A板和B板通过扣紧件可拆卸连接组成,所述电路板的顶部设置有电路板A面。本技术通过一块支持PCIe多通道测试的可编程控制电路板,可降低PCIe物理层接收端或发射端测试场景中的多通道测试耗时长,解决了测试治具易损坏的问题,同时降低了原有测试线路的传输损耗和串扰,通过50欧姆电阻的连接,可以确保差分信号的阻抗灵活匹配,减少信号损耗和反射,提高测试效率。

技术研发人员:丁立业,马春宇,倪哲明,包暘

受保护的技术使用者:上海灏谷集成电路技术有限公司

技术研发日:20230619

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!