随机数采集与测试系统的制作方法

本技术涉及随机数测试,尤其涉及一种随机数采集与测试系统。

背景技术:

1、随机数在科学研究和工程技术等方面有着非常广泛的应用,为了确保随机数设备生成的随机数是真随机数,通常需要对随机数进行专门的测试。

2、然而,相关技术中随机数测试系统通常是先采集随机数,然后将随机数存储后,将文件拷贝至随机数检测主机,随机数检测主机加载文件然后进场测试。如上所述的检测方法,采集过程和检测过程在分立的设备锁进行,无法实施检测,检测效率低下。

技术实现思路

1、本实用新型提供了一种随机数采集与测试系统,以提高随机数检测的效率。

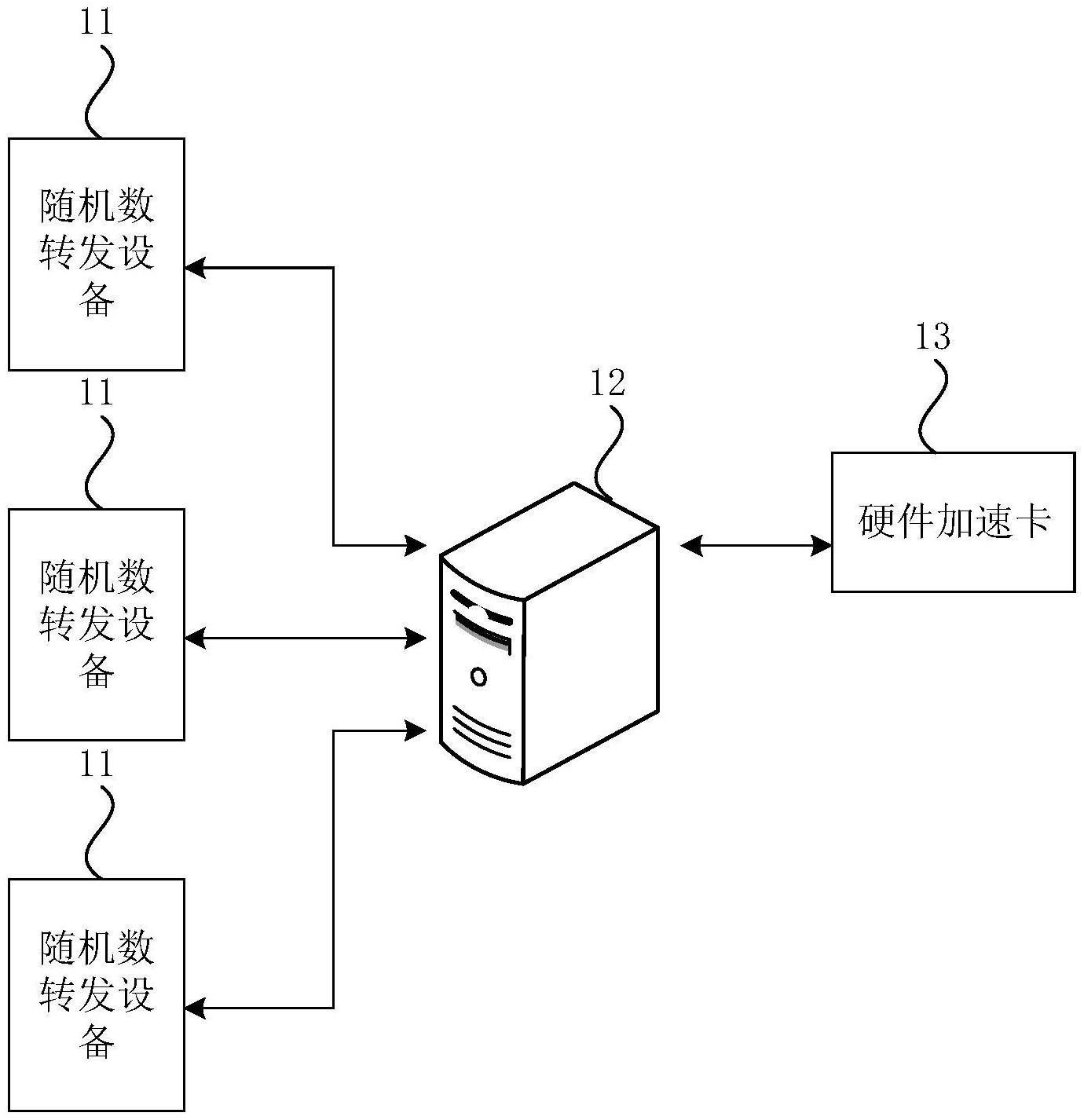

2、根据本实用新型的一方面,提供了一种随机数采集与测试系统,包括:至少一个随机数转发设备、服务器和至少一个硬件加速卡;所述随机数转发设备用于采集待测试随机数,并将所述待测试随机数转发至所述服务器;所述服务器与所述随机数转发设备及所述硬件加速卡通讯连接,所述服务器用于将所述待测试随机数实时转发至所述硬件加速卡,并接收所述硬件加速卡的处理结果,将所述处理结果转发至对应的所述随机数转发设备;所述硬件加速卡包括至少一个fpga芯片,每个所述fpga芯片包括随机性测试模块,所述随机性测试模块用于同时对多个所述待测试随机数进行并行测试。

3、可选地,所述fpga芯片还包括所述随机数采集模块,所述随机数采集模块与所述随机性测试模块通讯连接,所述随机数采集模块用于将串行的待测试随机数转换为并行数据。

4、可选地,所述fpga芯片还包括测试结果统计模块,所述测试结果统计模块与所述随机性测试模块通讯连接,所述测试结果统计模块用于记录所述待测试随机数的测试结果。

5、可选地,所述fpga芯片还包括:缓存模块,所述缓存模块与所述测试结果统计模块通讯连接,所述缓存模块用于存储通过随机性测试的待测试随机数。

6、可选地,所述fpga芯片还包括:

7、通讯协议处理模块,所述通讯协议处理模块与所述服务器、所述缓存模块及所述随机数采集模块通讯连接,所述通讯协议处理模块用于与所述服务器进行通讯协议匹配。

8、可选地,所述随机数转发设备包括:至少一个输入接口,所述输入接口用于输入所述待测试随机数;

9、处理芯片,所述处理芯片与所述输入接口通讯连接,所述处理芯片用于将所述待测试随机数转换为预设传输模式的待测试随机数;

10、输出接口,所述输出接口与所述处理芯片通讯连接,所述输出接口用于将所述预设传输模式的待测试随机数传输至所述服务器。

11、可选地,所述输入接口的类型为:spi类型、uart类型或usb类型。

12、可选地,所述输出接口为网线接口或无线信号发射器。

13、可选地,所述服务器为云端服务器。

14、本实用新型实施例的技术方案,采用的随机数采集与测试系统包括:至少一个随机数转发设备、服务器和至少一个硬件加速卡;随机数转发设备用于采集待测试随机数,并将待测试随机数转发至服务器;服务器与随机数转发设备及硬件加速卡通讯连接,服务器用于将待测试随机数实时转发至硬件加速卡,并接收硬件加速卡的处理结果,将处理结果转发至对应的随机数转发设备;硬件加速卡包括至少一个fpga芯片,每个fpga芯片包括随机性测试模块,随机性测试模块用于同时对多个待测试随机数进行并行测试。随机数采集与测试系统既能够采集待测试随机数,又能够对随机数的随机性进行实时转发及检测,也即集成采集与检测功能为一体,因而能够提高检测效率,节省检测时间。并且硬件加速卡通过硬件加速的方式,能够提高检测速度,同时,通过随机性测试模块对多个待测试随机数进行并行检测,可以同时对多个待测试随机数进行检测,可进一步提高检测效率。

15、应当理解,本部分所描述的内容并非旨在标识本实用新型的实施例的关键或重要特征,也不用于限制本实用新型的范围。本实用新型的其它特征将通过以下的说明书而变得容易理解。

技术特征:

1.一种随机数采集与测试系统,其特征在于,包括:至少一个随机数转发设备、服务器和至少一个硬件加速卡;所述随机数转发设备用于采集待测试随机数,并将所述待测试随机数转发至所述服务器;所述服务器与所述随机数转发设备及所述硬件加速卡通讯连接,所述服务器用于将所述待测试随机数实时转发至所述硬件加速卡,并接收所述硬件加速卡的处理结果,将所述处理结果转发至对应的所述随机数转发设备;所述硬件加速卡包括至少一个fpga芯片,每个所述fpga芯片包括随机性测试模块,所述随机性测试模块用于同时对多个所述待测试随机数进行并行测试。

2.根据权利要求1所述的随机数采集与测试系统,其特征在于,所述fpga芯片还包括随机数采集模块,所述随机数采集模块与所述随机性测试模块通讯连接,所述随机数采集模块用于将串行的待测试随机数转换为并行数据。

3.根据权利要求2所述的随机数采集与测试系统,其特征在于,所述fpga芯片还包括测试结果统计模块,所述测试结果统计模块与所述随机性测试模块通讯连接,所述测试结果统计模块用于记录所述待测试随机数的测试结果。

4.根据权利要求3所述的随机数采集与测试系统,其特征在于,所述fpga芯片还包括:缓存模块,所述缓存模块与所述测试结果统计模块通讯连接,所述缓存模块用于存储通过随机性测试的待测试随机数。

5.根据权利要求4所述的随机数采集与测试系统,其特征在于,所述fpga芯片还包括:

6.根据权利要求1所述的随机数采集与测试系统,其特征在于,所述随机数转发设备包括:至少一个输入接口,所述输入接口用于输入所述待测试随机数;

7.根据权利要求6所述的随机数采集与测试系统,其特征在于,所述输入接口的类型为:spi类型、uart类型或usb类型。

8.根据权利要求6所述的随机数采集与测试系统,其特征在于,所述输出接口为网线接口或无线信号发射器。

9.根据权利要求1所述的随机数采集与测试系统,其特征在于,所述服务器为云端服务器。

技术总结

本技术公开了一种随机数采集与测试系统,包括:至少一个随机数转发设备、服务器和至少一个硬件加速卡;所述随机数转发设备用于采集待测试随机数,并将所述待测试随机数转发至所述服务器;所述服务器与所述随机数转发设备及所述硬件加速卡通讯连接,所述服务器用于将所述待测试随机数实时转发至所述硬件加速卡,并接收所述硬件加速卡的处理结果,将所述处理结果转发至对应的所述随机数转发设备;所述硬件加速卡包括至少一个FPGA芯片,每个所述FPGA芯片包括随机性测试模块,所述随机性测试模块用于同时对多个所述待测试随机数进行并行测试。本技术能够提高随机数检测的效率。

技术研发人员:李泽忠,徐洪飞,胡小飞,毕超,姚顺

受保护的技术使用者:合肥硅臻芯片技术有限公司

技术研发日:20230724

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!