一种用于芯片的应力仿真方法、系统、设备和存储介质与流程

本发明涉及芯片仿真,特别是涉及一种用于芯片的应力仿真方法、系统、设备和存储介质。

背景技术:

1、随着芯片的封装工艺的发展,目前带有倒装芯片(fc)结构的封装、晶圆级封装(wlp)、系统级封装(sip)、2.5d/3d封装等均被认为属于先进封装范畴,其中,晶圆级封装是在芯片还在晶圆上的时候就对芯片进行封装,保护层可以黏接在晶圆的顶部或底部,然后连接电路,再将晶圆切成单个芯片,根据引线方式不同,晶圆级封装又可以分为扇入式(fan-in wlp/fi-wlp)、扇出式(fan-out wlp/fo-wlp)。扇出晶圆级封装(fo-wlp)是标准wlp的增强版,可以实现更多数量的i/o连接。它将芯片嵌入环氧树脂成型材料中,然后在晶圆表面建构高密度重分布层(rdl)并施加焊锡球,形成重构晶圆(reconstituted wafer)。

2、芯片的应力仿真是对芯片进行封装设计时必须做的评估,对于fanout芯片的单颗芯片应力仿真,为减少运算时间,降低仿真对硬件的要求,目前常用的仿真方式是将重布线层的结构进行简化,将重布线层的所有层用用单一的等效材料代替,省略rdl走线,从而减少网格数量和求解时间,这是这种方式存在的问题是芯片不含rdl分布时的翘曲仿真与实际翘曲结果偏差较大,造成仿真精度降低。

技术实现思路

1、为了解决上述技术问题,本发明提供了一种用于芯片的应力仿真方法、系统、计算机设备和存储介质,以能够解决现有仿真方法精度不高或仿真时间过长的问题,达到降低芯片应力仿真时间和提高芯片应力仿真精度的效果。

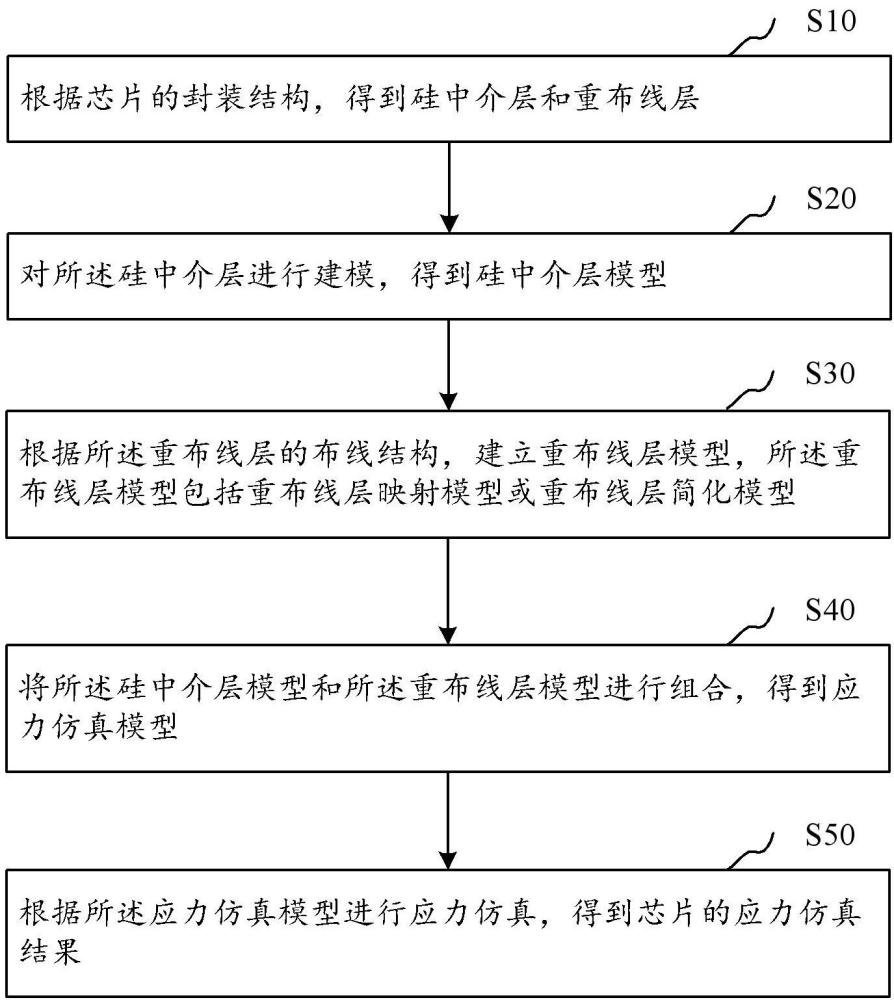

2、第一方面,本发明提供了一种用于芯片的应力仿真方法,所述方法包括:

3、根据芯片的封装结构,得到硅中介层和重布线层;

4、对所述硅中介层进行建模,得到硅中介层模型;

5、根据所述重布线层的布线结构,建立重布线层模型,所述重布线层模型包括重布线层映射模型或重布线层简化模型;

6、将所述硅中介层模型和所述重布线层模型进行组合,得到应力仿真模型;

7、根据所述应力仿真模型进行应力仿真,得到芯片的应力仿真结果。

8、进一步地,所述根据所述重布线层的布线结构,建立重布线层模型的步骤包括:

9、根据所述重布线层的布线结构,将所述重布线层划分为若干个重布线子层;

10、获取每个重布线子层的层参数,所述层参数包括材料属性参数、层厚度参数和布线占比参数;

11、根据所述层参数,对各个重布线子层进行映射,得到重布线层映射模型。

12、进一步地,所述根据所述重布线层的布线结构,建立重布线层模型的步骤包括:

13、根据所述重布线层的布线结构,将所述重布线层划分为若干个重布线子层;

14、获取每个重布线子层的布线图像,并对所述布线图像进行简化,得到简化布线图像;

15、根据所述简化布线图像,对所述重布线层的布线结构进行简化,得到简化重布线层;

16、对所述简化重布线层进行仿真建模,得到重布线层简化模型。

17、进一步地,所述并对所述布线图像进行简化,得到简化布线图像的步骤包括:

18、对所述布线图像进行有限元网格划分,并将每个有限元网格内的布线段转换为布线点,得到布线点图像;

19、将所述布线点图像划分为若干个布线点子图像,并对每个布线点子图像内的布线点进行聚类,得到聚类中心点;

20、根据连接条件,将各个聚类中心点相连接,得到第一布线图像;

21、判断所述第一布线图像是否满足迭代停止条件,若是,则将第一布线图像作为简化布线图像,反之,则继续执行当前迭代简化步骤,直至得到简化布线图像。

22、进一步地,所述根据连接条件,将各个聚类中心点相连接,得到第一布线图像的步骤包括:

23、计算各个聚类中心点与相邻的聚类中心点之间的距离,按照距离约束条件和边连接条件,将各个聚类中心点相连接,得到第一布线图像;其中,所述距离约束条件为每个聚类中心点的第一距离小于等于第二距离,所述第一距离为所述聚类中心点与邻接的聚类中心点之间的距离,所述第二距离为所述聚类中心点与相邻且非相连的聚类中心点之间的距离;所述边接连条件为所述聚类中心点至少有一条边且至多有两条边,且每条边的宽度与经过的布线点子图像中的点密度相一致。

24、进一步地,所述判断所述第一布线图像是否满足迭代停止条件的步骤包括:

25、判断每个聚类中心点的第一距离是否等于第二距离,若是,则将所述聚类中心点作为第一中心点;

26、获取所述第一中心点的点数量,并判断所述点数量是否小于阈值,若是,则判定所述第一布线图像满足迭代停止条件。

27、进一步地,在所述根据各个重布线子层对应的简化布线图像,对所述重布线层的布线结构进行简化的步骤之前,所述方法还包括:

28、计算重布线子层的布线图像与简化布线图像之间的图像相似度,并根据所述图像相似度,判断所述简化布线图像是否为最优简化布线图像;

29、若是,则根据各个最优简化布线图像,对所述重布线层的布线结构进行简化,反之,则对迭代简化进行回滚,得到前次简化布线图像,并判断前次简化布线图像是否为最优简化布线图像,直至得到最优简化布线图像。

30、第二方面,本发明提供了一种用于芯片的应力仿真系统,所述系统包括:

31、数据获取模块,用于根据芯片的封装结构,得到硅中介层和重布线层;

32、第一建模模块,用于对所述硅中介层进行建模,得到硅中介层模型;

33、第二建模模块,用于根据所述重布线层的布线结构,建立重布线层模型,所述重布线层模型包括重布线层映射模型或重布线层简化模型;

34、第三建模模块,用于将所述硅中介层模型和所述重布线层模型进行组合,得到应力仿真模型;

35、应力仿真模块,用于根据所述应力仿真模型进行应力仿真,得到芯片的应力仿真结果。

36、第三方面,本发明实施例还提供了一种计算机设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,所述处理器执行所述计算机程序时实现上述方法的步骤。

37、第四方面,本发明实施例还提供一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时实现上述方法的步骤。

38、本发明提供了一种用于芯片的应力仿真方法、系统、设备和存储介质。通过所述方法,对硅中介层和重布线层分别建模,并通过映射和简化的方式对重布线层进行建模,能够降低模型的复杂度,从而在降低芯片应力仿真的仿真时间的同时还有效提高了芯片应力仿真的仿真精度。

技术特征:

1.一种用于芯片的应力仿真方法,其特征在于,所述方法包括:

2.根据权利要求1所述的用于芯片的应力仿真方法,其特征在于,所述根据所述重布线层的布线结构,建立重布线层模型的步骤包括:

3.根据权利要求1所述的用于芯片的应力仿真方法,其特征在于,所述根据所述重布线层的布线结构,建立重布线层模型的步骤包括:

4.根据权利要求3所述的用于芯片的应力仿真方法,其特征在于,所述并对所述布线图像进行简化,得到简化布线图像的步骤包括:

5.根据权利要求4所述的用于芯片的应力仿真方法,其特征在于,所述根据连接条件,将各个聚类中心点相连接,得到第一布线图像的步骤包括:

6.根据权利要求4所述的用于芯片的应力仿真方法,其特征在于,所述判断所述第一布线图像是否满足迭代停止条件的步骤包括:

7.根据权利要求4所述的用于芯片的应力仿真方法,其特征在于,在所述根据各个重布线子层对应的简化布线图像,对所述重布线层的布线结构进行简化的步骤之前,所述方法还包括:

8.一种用于芯片的应力仿真系统,其特征在于,所述系统包括:

9.一种计算机设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,其特征在于,所述处理器执行所述计算机程序时实现权利要求1至7中任一项所述方法的步骤。

10.一种计算机可读存储介质,其上存储有计算机程序,其特征在于,所述计算机程序被处理器执行时实现权利要求1至7中任一项所述的方法的步骤。

技术总结

本发明涉及芯片仿真技术领域,公开了一种用于芯片的应力仿真方法、系统、设备和存储介质,包括根据芯片的封装结构,得到硅中介层和重布线层;对所述硅中介层进行建模,得到硅中介层模型;根据所述重布线层的布线结构,建立重布线层模型;将硅中介层模型和重布线层模型进行组合,得到应力仿真模型;根据应力仿真模型进行应力仿真,得到芯片的应力仿真结果。本发明通过映射或简化的方式对重布线层进行建模,不仅能够准确反映重布线层中金属布线的分布情况,并且有效降低了应力仿真模型的复杂度,通过验证和迭代回滚的方式降低了布线简化的简化程度对仿真精度的影响,在降低芯片应力仿真的仿真时间和硬件需求的同时保证了芯片应力仿真的仿真效果。

技术研发人员:李更,姚大平

受保护的技术使用者:江苏中科智芯集成科技有限公司

技术研发日:

技术公布日:2024/2/21

- 还没有人留言评论。精彩留言会获得点赞!