一种可拓展芯粒的实现及拓展方法与流程

本发明属于可拓展芯片设计,具体涉及一种可拓展芯粒的实现及拓展方法。

背景技术:

1、随着人工智能技术不断在各个行业应用,对芯片算力的需求越来越高,尤其是ai大模型的快速发展,使得现有单芯片的算力越难越难以满足实际计算需求,当前提升算力的途径除了增加芯片数量形成算力集群之外,常规的做法多是采用扩大芯片面积及增加晶体管数量的方式来提升单芯片性能。

2、然而,受先进工艺制程的限制和设计复杂度的限制,当芯片的工艺尺寸微缩到物理极限,继续通过芯片增加面积来提高算力的途径将变得困难,并且,更大的芯片面积也意味着更高的设计复杂度,可能会引入更多的设计和制造错误,导致芯片的可靠性降低。

技术实现思路

1、为了解决上述背景技术中提到的至少一个问题,本发明提出了提出了一种可拓展芯粒的实现及拓展方法。

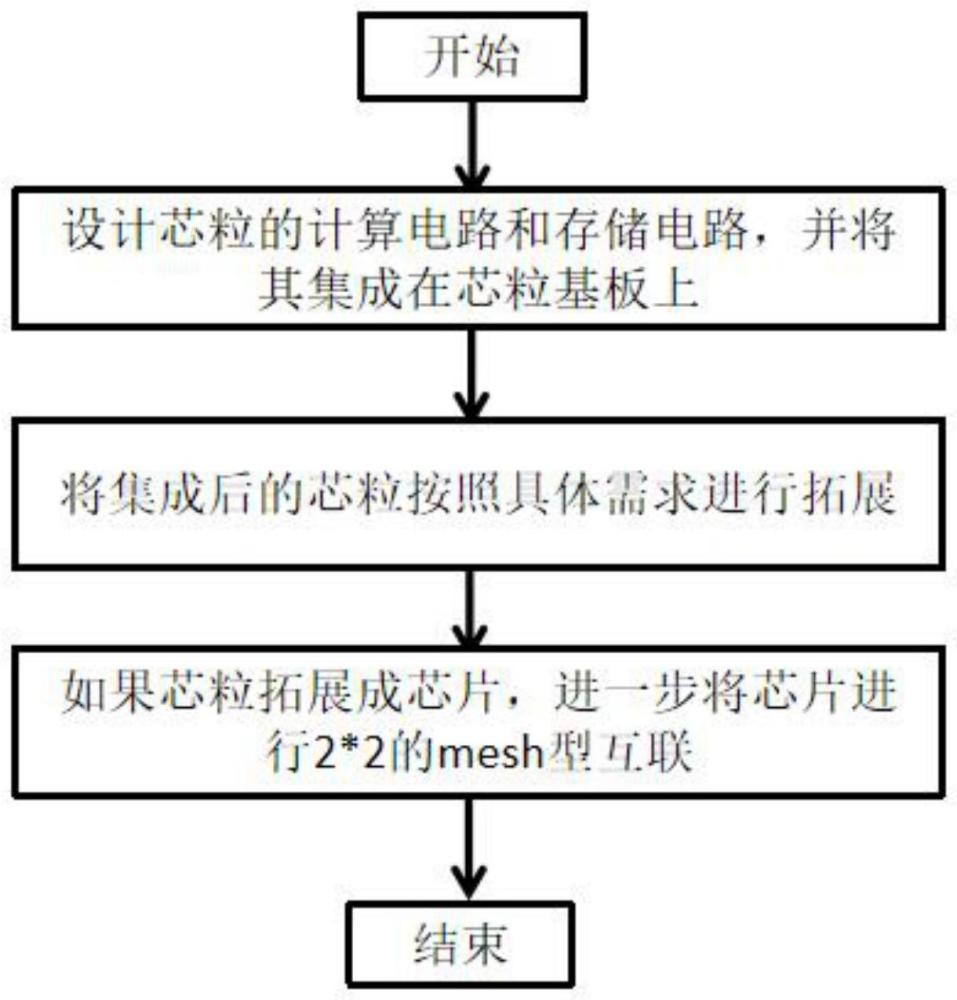

2、一种可拓展芯粒的实现及拓展方法,包括步骤:

3、步骤s1,设计芯粒的计算电路和存储电路,并将计算电路和存储电路集成在芯粒基板上,具体地,设计的计算电路和存储电路包含tr接口、pcie接口、lpddr接口和c2c接口;其中,c2c接口用于芯片之间的相互连接;pcie接口用于芯片和主机的连接;lpddr接口用于连接芯片外dram颗粒;tr接口用于可拓展芯粒之间的相互连接;

4、将计算电路和存储电路集成在芯粒基板上,具体步骤为:

5、首先,在芯粒基板上,将芯粒基板标记为四条边端,具体标记方式为:当芯粒基板水平放置时,按照顺时针的方向,以芯粒基板的边缘北端为起点,四条边缘端分别为芯粒边缘a端、芯粒边缘b端、芯粒边缘c端和芯粒边缘d端;然后,在芯粒边缘a端布局2个tr接口;在芯粒边缘b端布局1个c2c接口,1个pcie接口和1个lpddr接口;这三个接口的具体排列方式为:以芯粒边缘a端为上,芯粒边缘c端为下,从上到下依次为:pcie接口、c2c接口、lpddr接口;并且c2c接口与lpddr接口相邻,pcie接口与c2c接口相邻;接着,在芯粒边缘c端布局1个lpddr接口和1个c2c接口;最后,在芯粒边缘d端布局2个tr接口。

6、受先进工艺制程的限制和设计复杂度的限制,当芯片的工艺尺寸微缩到物理极限,传统采用继续通过增加芯片面积来提高算力的途径将变得困难,本发明提出将芯粒进行模块化的设计,这不仅可以有效降低芯片的设计难度,还能够有效改善良率,同时降低因为不良率而导致的芯片设计成本增加。

7、步骤s2,将集成后的芯粒按照具体需求进行拓展,具体拓展方式包括芯粒配合io芯片使用,以及将芯粒封装成芯片,其中,将芯粒封装成芯片,具体步骤为:

8、首先,在一块基板上,放置四个芯粒,具体放置方式为:按照顺时针的方向,以左下的芯粒为起点,分别标记为芯粒一、芯粒二、芯粒三、芯粒四;

9、然后,将芯粒二按照顺时针的方向旋转90度,旋转后的芯粒二通过边缘a端的tr接口与芯粒一的边缘d端的tr接口相连接;将芯粒三按照顺时针的方向旋转180度,旋转后的芯粒三通过边缘a端的tr接口与芯粒二的边缘d端的tr接口相连接;

10、接着,将芯粒四按照顺时针的方向旋转270度,旋转后的芯粒四通过边缘a端的tr接口与芯粒三的边缘d端的tr接口相连接;将旋转后的芯粒四通过边缘d端的tr接口与芯粒一的边缘a端的tr接口相连接。

11、传统的芯片拓展一般是通过外接交换机进行多芯片拓展,本发明设计的可拓展芯粒可直接通过连接芯片上的c2c接口进行拓展,不仅赋予了芯片设计更多的灵活性和扩展性,还能够以合理的成本实现芯片快速集成以达到更高的算力的目的。

12、步骤s3,如果芯粒拓展成芯片,进一步将芯片进行2*2的mesh型互联;还可以将封装后的芯片根据算力需求进行其他规格的mesh型互联,进行mesh互联芯片的数量满足n*n,其中,n≥2,n为水平方向上的芯片数量和竖直方向上的芯片数量,即水平方向上的芯片数量和竖直方向上的芯片数量要相等;

13、其中,将芯片进行2*2的mesh型互联,具体步骤为:

14、首先,将封装后的芯片标记为四条边端,具体标记方式为:当芯片水平放置时,按照顺时针的方向,以芯片基板的边缘北端为起点,四条边缘端分别为芯片边缘a端、芯片边缘b端、芯片边缘c端和芯片边缘d端;然后,在一块基板上,放置四个芯片,按照顺时针的方向,以左下的芯片为起点,分别标记为芯片一、芯片二、芯片三、芯片四;

15、接着,通过连接芯片一中芯片边缘d端的c2c接口与芯片二中芯片边缘b端的的c2c接口,完成芯片一与芯片二的互联;通过连接芯片二中芯片边缘a端的c2c接口与芯片三中芯片边缘c端的的c2c接口,完成芯片二与芯片三的互联;通过连接芯片三中芯片边缘b端的c2c接口与芯片四中芯片边缘d端的的c2c接口,完成芯片三与芯片四的互联;通过连接芯片四中芯片边缘c端的c2c接口与芯片一中芯片边缘a端的的c2c接口,完成芯片四与芯片一的互联。

16、传统的芯片以单颗芯粒为主,设计的局限导致后期难以支持进行dram存储扩容,本发明设计的可拓展芯粒可以通过d2d接口与另一颗io芯片互联实现dram扩容,解决了芯片设计定型后难以进行存储扩容的难题。

17、本发明提出了一种可拓展芯粒的实现及拓展方法,与现有的技术相比,具有以下有益效果:

18、本发明提出将芯粒进行模块化的设计,这不仅可以有效降低芯片的设计难度,还能够有效改善良率,同时降低因为不良率而导致的芯片设计成本增加;

19、本发明设计的可拓展芯粒可直接通过连接芯片上的c2c接口进行拓展,不仅赋予了芯片设计更多的灵活性和扩展性,还能够以合理的成本实现芯片快速集成以达到更高的算力的目的;

20、本发明设计的可拓展芯粒可以通过d2d接口与另一颗io芯片互联实现dram扩容,解决了芯片设计定型后难以进行存储扩容的难题。

技术特征:

1.一种可拓展芯粒的实现及拓展方法,其特征在于,包括步骤:

2.根据权利要求1所述的一种可拓展芯粒的实现及拓展方法,其特征在于,步骤s1中所述的设计芯粒的计算电路和存储电路,具体包含tr接口、pcie接口、lpddr接口和c2c接口;

3.根据权利要求1所述的一种可拓展芯粒的实现及拓展方法,其特征在于,步骤s1中所述的将计算电路和存储电路集成在芯粒基板上,包括步骤:

4.根据权利要求3所述的一种可拓展芯粒的实现及拓展方法,其特征在于,步骤s103中所述的在芯粒边缘b端布局1个c2c接口,1个pcie接口和1个lpddr接口,具体排列方式为:

5.根据权利要求1所述的一种可拓展芯粒的实现及拓展方法,其特征在于,步骤s2中所述的将集成后的芯粒按照具体需求进行拓展,具体拓展方式包括芯粒配合io芯片使用,以及将芯粒封装成芯片。

6.根据权利要求5所述的一种可拓展芯粒的实现及拓展方法,其特征在于,所述将芯粒封装成芯片,包括步骤:

7.根据权利要求1所述的一种可拓展芯粒的实现及拓展方法,其特征在于,步骤s3中所述的将芯片进行2*2的mesh型互联,包括步骤:

8.根据权利要求1所述的一种可拓展芯粒的实现及拓展方法,其特征在于,在步骤s3中,如果芯粒拓展成芯片,除了步骤s3中所述的进一步将芯片进行2*2的mesh型互联,还可以将封装后的芯片根据算力需求进行其他规格的mesh型互联,进行mesh互联芯片的数量满足n*n,

技术总结

本发明属于可拓展芯片设计技术领域,具体公开了一种可拓展芯粒的实现及拓展方法。本发明提出将芯粒进行模块化的设计,不仅可以有效降低芯片的设计难度,还能够有效降低因为不良率而导致的芯片设计成本增加;并且,本发明设计的可拓展芯粒可直接通过连接芯片上的C2C接口进行拓展,不仅赋予了芯片设计更多的灵活性和扩展性,还能够以合理的成本实现芯片快速集成以达到更高的算力的目的;此外,本发明设计的可拓展芯粒可以通过D2D接口与另一颗IO芯片互联实现DRAM扩容,解决了芯片设计定型后难以进行存储扩容的难题。

技术研发人员:于义,欧阳鹏

受保护的技术使用者:北京清微智能科技有限公司

技术研发日:

技术公布日:2024/5/10

- 还没有人留言评论。精彩留言会获得点赞!