用于访问存储器的方法和数据存储架构及计算设备与流程

本发明涉及ai芯片,具体涉及一种用于访问存储器的方法及计算设备。

背景技术:

1、随着大模型人工智能的飞速发展,对人工智能芯片处理数据的能力与效率要求越来越高。人工智能芯片中片上存储已经难以满足大模型数据量的需求。如何提高数据存储量的同时,又满足数据读取的高效率,是数据流架构芯片中的关键技术之一。

2、为提高数据存储量,一般采用片外存储,如ddr sdram,甚至hbm,其容量比片上存储(如ram)更大,且成本更低。其中,ddr存储控制器作为计算机存储系统的重要组成部分,对于整个系统的性能和稳定性具有举足轻重的作用。

3、ddr sdram容量大,但读写效率直接受到读写地址的影响。根据ddr sdram的物理特性,其芯片内部分为不同的rank,每个rank内又分为不同的bank,每个bank内再分为不同的row,每个row内又分为不同的column,每个column上是最小的存储单元。而人工智能芯片中的模块对ddr sdram读取数据时,一般不会直接操作rank/bank/row/column这些物理地址,而是使用系统地址,如axi、ahb等协议的地址。系统地址与物理地址的映射关系一般通过大量的数据读写场景测试来统计,最终选取一种较高效率的映射方法。例如,一种物理地址rank/bank/row/column从高位到低在系统地址中的分布为:2位rank地址,16位row地址,3位bank地址以及10位column地址,分别映射到系统地址的bit33~bit3。在上述地址映射方案中,能够保证顺序读写的效率比较高,即地址依次递增时读写效率较高,但其他场景的读写(如地址跳跃时)效率得不到保证。

4、在ddr sdram读写前,需要将待操作存储单元所在的rank、bank与row地址一起限定的某一行进行激活(activate)后,才能进行读或写,该行被激活后,其内部不同的列(column)单元上的存储单元可以连续读写。当某一行读写操作完成后,需要切换到另一行继续读写时,需要将当前行进行预充电(precharge)关闭,再通过activate指令激活另一行。由于激活与预充电需要一定的时间,在此期间不允许对该行进行读写操作,因而为了提高整体的读写效率,需要尽量减少物理行地址的切换操作。但在数据流架构芯片中,经常会遇到地址不连续的读写,如果统一按照上述的地址映射方案,会导致ddr sdram频繁地切换bank/row地址,激活与关闭行单元的时间占比会很大,从而将ddr sdram的读写带宽利用率大幅度地降低。

5、为此,需要一种技术方案,能够提高存储器读写效率。

技术实现思路

1、本申请旨在提供一种用于访问存储器的方法及计算设备,能够根据数据存储地址变化类型来动态调整系统地址与物理地址映射的方法,提高存储器读写效率。

2、根据本申请的一方面,提供一种用于访问存储器的方法,包括:

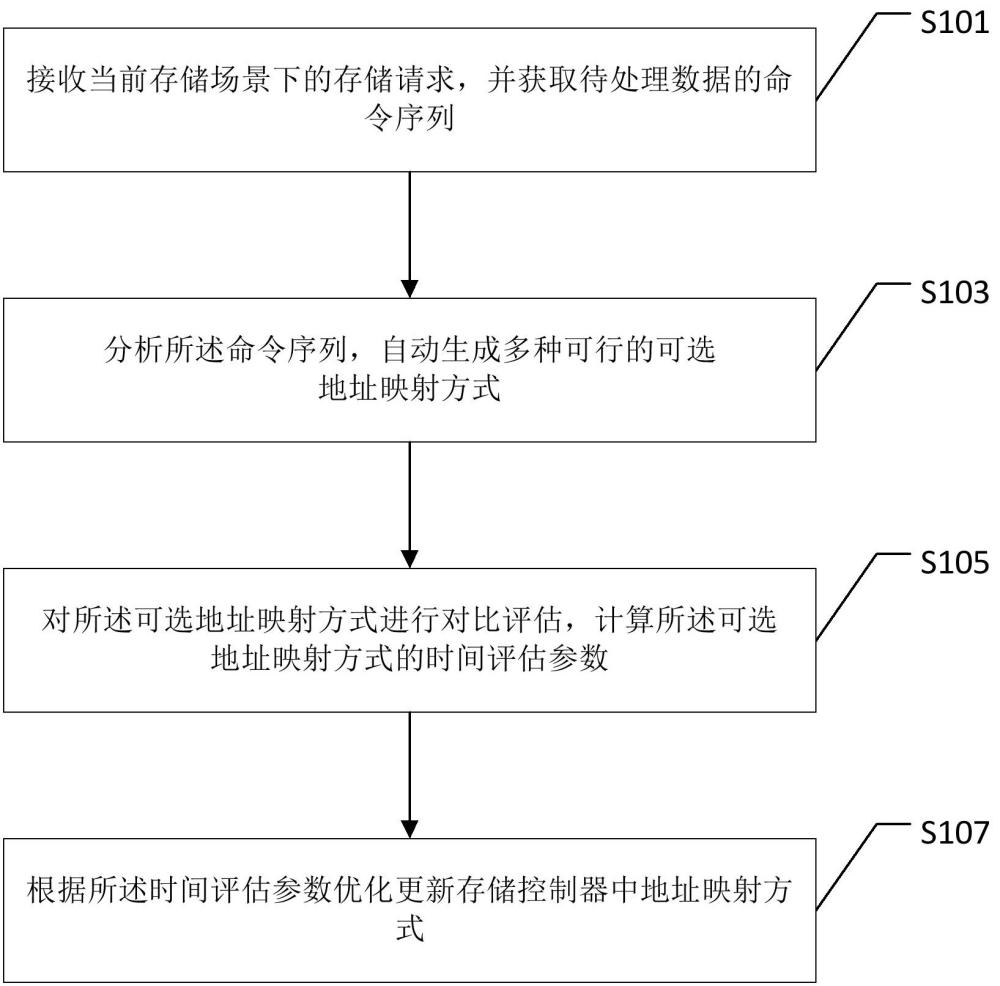

3、接收当前存储场景下的存储请求,并获取待处理数据的命令序列;

4、分析所述命令序列,自动生成多种可行的可选地址映射方式;

5、对所述可选地址映射方式进行对比评估,计算所述可选地址映射方式的时间评估参数;

6、根据所述时间评估参数优化更新存储控制器中地址映射方式。

7、根据一些实施例,对所述可选地址映射方式进行对比评估,计算所述可选地址映射方式的时间评估参数,包括:

8、预估当前地址映射下的所述可选地址映射方式的数据读写访问节省时间以及更新映射配置所需时间;

9、计算相对当前地址映射的各个可选地址映射的时间评估参数。

10、根据一些实施例,所述时间评估参数为当前地址映射下的所述可选地址映射方式的数据读写访问节省时间减去更新配置所需时间之差。

11、根据一些实施例,所述可选地址映射方式的数据读写访问节省时间为预估当前配置的总行地址切换时间减去预估所述可选地址映射方式总行地址切换时间。

12、根据一些实施例,所述更新配置所需时间为需要更新的寄存器个数与更新单个寄存器的软件消耗时间的乘积。

13、根据一些实施例,根据所述时间评估参数优化更新存储控制器中地址映射方式,包括:

14、若所述时间评估参数中存在正值,则选取时间评估参数最大值相应的映射方式作为该场景下的最优地址映射方式;

15、若所述时间评估参数中不存在正值,则维持原配置作为该场景下的最优地址映射方式。

16、根据一些实施例,所述方法还包括:

17、利用所述最优地址映射方式更新存储控制器中地址映射方式。

18、根据本申请的另一方面,提供一种数据存储架构,包括访存主设备、调度控制单元、存储控制器及存储器,其中:

19、所述访存主设备向所述调度控制单元发出第一访问请求;

20、所述调度控制单元根据所述第一访问请求更新所述存储控制器中地址映射配置并向所述存储控制器发出第二访问请求;

21、所述存储控制器根据所述第二访问请求向所述存储器发出第三访问请求,接收来自所述存储器的访问响应,并将所述访问响应返回给所述访存主设备。

22、根据一些实施例,所述调度控制单元配置为:

23、接收当前存储场景下的存储请求,并获取待处理数据的命令序列;

24、分析所述命令序列,自动生成多种可行的可选地址映射方式;

25、对所述可选地址映射方式进行对比评估,计算所述可选地址映射方式的时间评估参数;

26、根据所述时间评估参数优化更新存储控制器中地址映射方式。

27、根据本申请的另一方面,提供一种计算设备,包括:

28、处理器;以及

29、存储器,存储有计算机程序,当所述计算机程序被所述处理器执行时,使得所述处理器执行如上任一项所述的方法。

30、根据本申请的另一方面,提供一种非瞬时性计算机可读存储介质,其上存储有计算机可读指令,当所述指令被处理器执行时,使得所述处理器执行如上任一项所述的方法。

31、根据本申请的实施例,通过对当前存储场景下的所述命令序列的分析,自动生成可行的多种地址映射方式,评估各个地址映射方式,选用最优的地址映射方式更新存储控制器中的地址映射方式,相比于传统的应用统一预设的地址映射访问存储器的方法,本发明的申请能够按照不同存储场景采用当前场景下的最优地址映射访问存储器,进行权衡决策,以达到带宽收益最大化,提高了存储器读写效率。

32、应当理解的是,以上的一般描述和后文的细节描述仅是示例性的,并不能限制本申请。

技术特征:

1.一种用于访问存储器的方法,其特征在于,包括:

2.根据权利要求1所述的方法,其特征在于,对所述可选地址映射方式进行对比评估,计算所述可选地址映射方式的时间评估参数,包括:

3.根据权利要求2所述的方法,其特征在于,所述时间评估参数为当前地址映射下的所述可选地址映射方式的数据读写访问节省时间减去更新配置所需时间之差。

4.根据权利要求3所述的方法,其特征在于,所述可选地址映射方式的数据读写访问节省时间为预估当前配置的总行地址切换时间减去预估所述可选地址映射方式总行地址切换时间。

5.根据权利要求2所述的方法,其特征在于,所述更新映射配置所需时间为需要更新的寄存器个数与更新单个寄存器的软件消耗时间的乘积。

6.根据权利要求1所述的方法,其特征在于,根据所述时间评估参数优化更新存储控制器中地址映射方式,包括:

7.根据权利要求6所述的方法,其特征在于,还包括:

8.一种数据存储架构,其特征在于,包括访存主设备、调度控制单元、存储控制器及存储器,其中:

9.根据权利要求8所述的数据存储架构,其特征在于,所述调度控制单元配置为:

10.一种计算设备,其特征在于,包括:

技术总结

本申请提供一种用于访问存储器的方法和数据存储架构及计算设备,包括:接收当前存储场景下的存储请求,并获取待处理数据的命令序列;分析所述命令序列,自动生成多种可行的可选地址映射方式;对所述可选地址映射方式进行对比评估,计算所述可选地址映射方式的时间评估参数;根据所述时间评估参数优化更新存储控制器中地址映射方式。根据本申请的技术方案能够根据数据存储地址变化类型来动态调整系统地址与物理地址映射的方法,提高数据流架构存储器读写效率。

技术研发人员:梁监天,蔡权雄,牛昕宇

受保护的技术使用者:深圳鲲云信息科技有限公司

技术研发日:

技术公布日:2024/3/21

- 还没有人留言评论。精彩留言会获得点赞!