一种系统级芯片的片外系统和应用程序固化方法

本申请属于系统级芯片,具体涉及一种系统级芯片的片外系统和应用程序固化方法。

背景技术:

1、随着我国卫星技术的发展,微纳卫星作为一种新兴的小型航天器, 具有低成本、功能密度高、研制周期短、搭载发射方式灵活等特点,在低轨道空间探测和对地观测领域得到了广泛应用。

2、系统级芯片(soc,system on chip)常被应用于微纳卫星的星载仪器上,而宇航级(高可靠)非易失性存储器(norflash)具有抗辐射的性能,适合在外太空使用。需要说明的是,宇航级非易失性存储器包括多个基片。

3、然而,系统级芯片和宇航级非易失性存储器并不兼容。

技术实现思路

1、本申请旨在提供一种系统级芯片的片外系统和应用程序固化方法,至少解决在先技术中系统级芯片和宇航级非易失性存储器不兼容的问题。

2、为了解决上述技术问题,本申请是这样实现的:

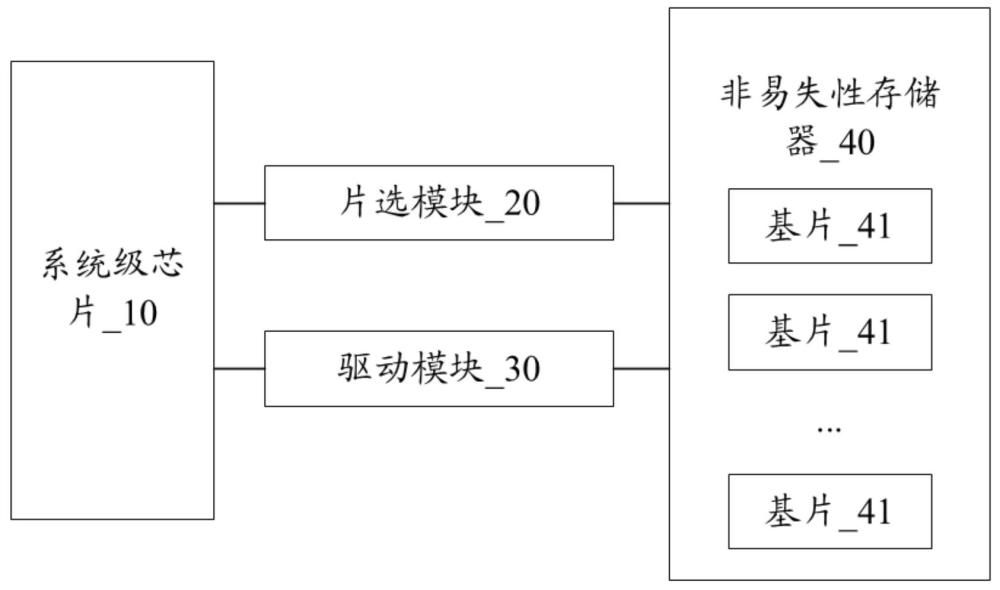

3、第一方面,本申请实施例提供了一种系统级芯片的片外系统,包括系统级芯片、片选模块、驱动模块、抗辐射的非易失性存储器,所述非易失性存储器包括多个基片;

4、所述系统级芯片分别与所述片选模块、所述驱动模块电连接,所述非易失性存储器分别与所述片选模块、所述驱动模块电连接;

5、所述片选模块用于根据所述系统级芯片的输出信号,生成选择信号,以供所述非易失性存储器根据所述选择信号,确定所述非易失性存储器的基片中,与所述驱动模块进行信号交互的目标基片;

6、所述驱动模块用于转发所述系统级芯片向所述非易失性存储器发送的第一信号,并将所述第一信号的第一电流值,转化为适配所述非易失性存储器的第二电流值;还用于转发所述非易失性存储器向所述系统级芯片发送的第二信号,并将所述第二信号的第二电流值,转化为适配所述系统级芯片的第一电流值。

7、第二方面,本申请实施例还提供了一种应用程序固化方法,应用于第一方面所述的系统级芯片的片外系统,所述系统级芯片的片外系统还包括双倍速率同步动态随机存储器,所述双倍速率同步动态随机存储器与所述系统级芯片电连接;所述方法包括:

8、获取所述非易失性存储器在所述系统级芯片映射的第一基地址;

9、根据所述第一基地址以及预设字节参量当前的参量值,获取当前待传输的一字节的程序数据在所述基片中的数据写入地址;所述程序数据为所述双倍速率同步动态随机存储器中预先存储的应用程序的数据,所述应用程序为向所述非易失性存储器烧录的应用程序;

10、通过所述系统级芯片,从所述双倍速率同步动态随机存储器中,获取所述当前待传输的一字节的程序数据,并根据所述数据写入地址,在所述基片中写入所述当前待传输的一字节的程序数据;

11、其中,每次在所述基片中写入当前待传输的一字节的程序数据的情况下,将所述预设字节参量当前的参量值加一字节,获取所述预设字节参量的新参量值。

12、第三方面,本申请实施例还提供了一种电子设备,该电子设备包括处理器,存储器及存储在所述存储器上并可在所述处理器上运行的程序或指令,所述程序或指令被所述处理器执行时实现如第二方面所述的方法的步骤。

13、第四方面,本申请实施例还提供了一种可读存储介质,所述可读存储介质上存储程序或指令,所述程序或指令被处理器执行时实现如第二方面所述的方法的步骤。

14、在本申请实施例中,非易失性存储器抗辐射,且非易失性存储器包括多个基片,即非易失性存储器为宇航级非易失性存储器,通过片选模块根据系统级芯片的输出信号,生成选择信号,以供非易失性存储器根据选择信号,确定非易失性存储器的基片中,与驱动模块进行信号交互的目标基片,通过驱动模块转发系统级芯片向非易失性存储器发送的第一信号,并将第一信号的第一电流值,转化为适配非易失性存储器的第二电流值,以及转发非易失性存储器向系统级芯片发送的第二信号,并将第二信号的第二电流值,转化为适配系统级芯片的第一电流值,因此,通过片选模块和驱动模块可以实现系统级芯片和非易失性存储器的兼容性连接,从而解决了在先技术中系统级芯片和宇航级非易失性存储器不兼容的问题。

技术特征:

1.一种系统级芯片的片外系统,其特征在于,包括系统级芯片、片选模块、驱动模块、抗辐射的非易失性存储器,所述非易失性存储器包括多个基片;

2.根据权利要求1所述的系统级芯片的片外系统,其特征在于,所述片选模块具体用于根据所述系统级芯片的输出信号,生成多路控制信号,所述控制信号与所述基片一一对应,以供所述非易失性存储器根据所述控制信号,控制所述控制信号对应的基片与所述驱动模块的连通或断开。

3.根据权利要求2所述的系统级芯片的片外系统,其特征在于,所述系统级芯片具有一个第一控制引脚和多个第一地址引脚,所述非易失性存储器具有多个第二控制引脚;所述片选模块包括译码芯片和多个第一电阻,所述译码芯片具有多个第一输入引脚和多个第一输出引脚;

4.根据权利要求3所述的系统级芯片的片外系统,其特征在于,所述第一输出引脚与所述基片一一对应;所述第一输出引脚用于输出所述第一输出引脚对应的基片的控制信号。

5.根据权利要求1所述的系统级芯片的片外系统,其特征在于,所述系统级芯片具有多个第二地址引脚,所述非易失性存储器具有多个第三地址引脚;

6.根据权利要求5所述的系统级芯片的片外系统,其特征在于,所述第一驱动芯片用于转发所述系统级芯片向所述非易失性存储器发送的地址信号,并将所述地址信号的第一电流值,转化为所述第二电流值。

7.根据权利要求5所述的系统级芯片的片外系统,其特征在于,所述系统级芯片还具有一个第一读使能引脚、一个第一写使能引脚以及一个第一复位引脚,所述非易失性存储器还具有一个第二读使能引脚、一个第二写使能引脚以及一个第二复位引脚;

8.根据权利要求7所述的系统级芯片的片外系统,其特征在于,

9.根据权利要求1所述的系统级芯片的片外系统,其特征在于,所述系统级芯片具有一个第一写使能引脚、一个第一控制引脚以及多个第一数据引脚,所述非易失性存储器具有多个第二数据引脚;

10.根据权利要求9所述的系统级芯片的片外系统,其特征在于,所述第一写使能引脚与所述第一写使能引脚对应的第三电阻的第一引脚电连接,所述第一写使能引脚对应的第三电阻的第二引脚与所述第一写使能引脚对应的反应控制引脚电连接;

11.根据权利要求10所述的系统级芯片的片外系统,其特征在于,在所述第一控制引脚为低电平,且所述第一写使能引脚为低电平的情况下,所述第二驱动芯片用于通过所述第一传输引脚接收电流值为第一电流值的第一数据信号,并通过所述第二传输引脚输出电流值为第二电流值的第一数据信号;

12.根据权利要求1所述的系统级芯片的片外系统,其特征在于,所述系统级芯片具有一个第一读使能引脚、一个第一控制引脚以及多个第一数据引脚,所述非易失性存储器具有多个第二数据引脚;

13.根据权利要求12所述的系统级芯片的片外系统,其特征在于,所述第一读使能引脚与所述第一读使能引脚对应的第三电阻的第一引脚电连接,所述第一读使能引脚对应的第三电阻的第二引脚与所述第一读使能引脚对应的反应控制引脚电连接;

14.根据权利要求13所述的系统级芯片的片外系统,其特征在于,在所述第一控制引脚为低电平,且所述第一读使能引脚为高电平的情况下,所述第二驱动芯片用于通过所述第一传输引脚接收电流值为第一电流值的第一数据信号,并通过所述第二传输引脚输出电流值为第二电流值的第一数据信号;

15.根据权利要求9或12所述的系统级芯片的片外系统,其特征在于,所述第二驱动芯片用于转发所述系统级芯片向所述非易失性存储器发送的第一数据信号,并将所述第一数据信号的第一电流值,转化为适配所述非易失性存储器的第二电流值;还用于转发所述非易失性存储器向所述系统级芯片发送的第二数据信号,并将所述第二数据信号的第二电流值,转化为适配所述系统级芯片的第一电流值。

16.一种应用程序固化方法,其特征在于,应用于如权利要求1至15中任一项所述的系统级芯片的片外系统,所述系统级芯片的片外系统还包括双倍速率同步动态随机存储器,所述双倍速率同步动态随机存储器与所述系统级芯片电连接;所述方法包括:

17.根据权利要求16所述的方法,其特征在于,所述方法还包括:

18.根据权利要求17所述的方法,其特征在于,所述指令包括数据写入指令、数据擦除指令。

19.根据权利要求16所述的方法,其特征在于,所述方法还包括:

20.根据权利要求16所述的方法,其特征在于,所述方法还包括:

21.根据权利要求16所述的方法,其特征在于,所述方法还包括:

22.一种电子设备,其特征在于,包括处理器,存储器及存储在所述存储器上并可在所述处理器上运行的程序或指令,所述程序或指令被所述处理器执行时实现如权利要求16至21中任一项所述的应用程序固化方法的步骤。

23.一种可读存储介质,其特征在于,所述可读存储介质上存储程序或指令,所述程序或指令被处理器执行时实现如权利要求16至21中任一项所述的应用程序固化方法的步骤。

技术总结

本申请提供了一种系统级芯片的片外系统和应用程序固化方法,涉及系统级芯片技术领域,系统级芯片的片外系统包括系统级芯片、片选模块、驱动模块、抗辐射的非易失性存储器,非易失性存储器抗辐射,且非易失性存储器包括多个基片,即非易失性存储器为宇航级非易失性存储器,通过片选模块和驱动模块可以实现系统级芯片和非易失性存储器的兼容性连接,从而解决了在先技术中系统级芯片和宇航级非易失性存储器不兼容的问题。

技术研发人员:乔颢,孙越强,杜起飞,蔡跃荣,王先毅,白伟华,王冬伟,李伟,曹光伟,刘成,李福,张浩,程双双,张璐璐,张鹏举,王卓炎,仇通胜,田羽森,夏俊明,柳聪亮,孟祥广,胡鹏,黄飞雄,谭广远,吴汝晗,尹聪

受保护的技术使用者:中国科学院国家空间科学中心

技术研发日:

技术公布日:2024/4/29

- 还没有人留言评论。精彩留言会获得点赞!