电流驱动的磁畴壁逻辑的制作方法

电流驱动的磁畴壁逻辑

1.本发明涉及用于存储和/或处理数据的设备。此外,本发明涉及包括多个上述设备的逻辑门。

2.zhaochu luo等人在chirally coupled nanomagnets,science 363,1435页至1439页(2019年)公开了在非易失性存储器、逻辑门和传感器中具有多种应用的磁耦合纳米磁体。使用界面dzyaloshinskii-moriya相互作用可以实现横向相邻纳米磁体的强耦合。这种耦合由平面外和平面内磁区之间的手性畴壁介导,并支配低于临界尺寸的纳米磁体的行为。该概念用于实现横向交换偏置、多状态磁配置之间的无场电流感应切换以及覆盖宽范围的长度尺度和拓扑的合成反铁磁体、斯格明子和人造自旋冰。该文献提供了设计相关纳米磁体阵列并实现平面逻辑门和存储设备的全电控制的平台。

3.一般来说,基于自旋的逻辑架构提供非易失性数据保持、近零泄漏和可扩展性,将技术路线图扩展至互补金属氧化物半导体(cmos)逻辑之外。基于磁畴壁的架构利用快速畴壁运动、高密度、非易失性和灵活的设计来处理和存储信息。然而,这种方案依赖于使用外部磁场的畴壁操控和时钟计时(clocking),这限制了它们在密集的大规模芯片中的实现。

4.因此,本发明的目的是提供一种用于存储和/或处理数据的设备,该设备为可扩展的全电磁逻辑提供了可行的平台,为逻辑存储器(memory-in-logic)的应用铺平了道路。

5.根据本发明,该目的是通过一种用于使用由自旋轨道矩(spin-orbit torques)引起的磁畴壁运动的概念来存储和/或处理数据的设备来实现的,所述设备包括:

6.a)由导电材料制成的支撑层;

7.b)设置在所述支撑层上的铁磁或亚铁磁层,铁磁或亚铁磁层能够表现出可调谐磁各向异性并提供磁跑道;

8.c)设置在所述铁磁或亚铁磁层上的在可调谐磁各向异性方面的功能层,所述功能层具有第一功能部分和第二功能部分以及在第一功能部分和第二功能部分之间的第三功能部分,其中,功能层的第一部分和第二部分使得铁磁或亚铁磁层能够具有垂直于层的平面的oop(平面外)磁化,并且功能层的第三部分使得铁磁或亚铁磁层能够具有仅平行于层的平面的ip(平面内)磁化;其中:

9.d)垂直且向上取向的oop磁化表示逻辑“0”并且向下取向的表示逻辑“1”,或者反之亦然,或者在一个方向上的ip磁化表示逻辑“0”并且在另一方向上的表示逻辑“1”,或者反之亦然;

10.e)响应于将由第一部分覆盖的铁磁或亚铁磁层的第一区域中的畴壁沿着磁跑道(rt)朝向在第一部分至第三部分的过渡处给出的界面移动,所述逻辑“1”或逻辑“0”能够被编码在由第二部分覆盖的铁磁或亚铁磁层的第二区域中,或者被编码在由第三部分覆盖的铁磁或亚铁磁层的第三区域中,以及/或者反之亦然;以及

11.f)向支撑层的电流供应,其中,施加至支撑层的受控电流脉冲使磁畴壁可确定地沿磁跑道移动。

12.因此,本发明公开了在磁畴壁跑道中执行全电逻辑操作和级联的概念。本发明利用由界面dzyaloshinskii-moriya相互作用引起的相邻磁畴之间的手性耦合来实现畴壁反

转器(domain-wall inverter),布尔逻辑的所有实现中的基本构建块。

13.当功能层的第一部分、第二部分和第三部分中的至少一个的功能通过以下中至少之一来实现时,本发明的优选实施方式可以关于铁磁或亚铁磁层中的可调谐磁各向异性的实现来实现:

14.a)第一部分和第二部分的功能层是金属氧化物层,而第三部分是金属层;b)第三部分是绝缘层,绝缘层包括电极,该电极使得能够在铁磁或亚铁磁层上在该oop方向上施加电场;

15.c)功能层的第三部分是被固态质子泵和/或离子辐射穿透的金属氧化物层;和/或

16.d)功能层的第三部分是被氦和/或镓聚焦离子束穿透的金属氧化物层。

17.在本发明的另一优选实施方式中,第一功能部分以及均在第一功能部分下面的铁磁或亚铁磁层和支撑层的宽度——在垂直于磁跑道方向的方向上所看到的——大于第二功能部分以及均在第二功能部分下面的铁磁或亚铁磁层和支撑层的宽度,或者反之亦然。在第三部分(第一部分与第二部分之间的界面部分)的两侧的跑道形状的这种不对称性还导致在从较小宽度至较大宽度的方向上与相反方向相比抑制畴成核的可能性的不对称性。因此,难以在具有较大宽度的ip区域一侧使反向畴(reverse domain)成核(nucleate)。当dw从较小侧到达v形ip区域时,它们被钉扎并且不能通过反转器。相反,由于“v”的顶点内侧上的成核中心不受影响,所以从较宽侧入射的dw可以朝向具有较小宽度的一侧传输。针对和dw两者都观察到这种表现。因此,反向畴的成核(nucleation)针对正电流和负电流是高度不对称的,但与dw极性无关。

18.优选地,在该示例中,沿磁跑道(rt)看到的宽度的路线(course)可以具有阶跃函数的形状。因此,具有较大宽度的一侧的宽度w1大于ip部分(第三部分)另一侧的宽度w2。

19.设备的其他优选实施方式由其他从属权利要求限定。

20.关于逻辑门的实现的目的根据本发明通过包括多个根据前述权利要求中任一项所述的设备的逻辑门来实现,其中,表示逻辑门的逻辑输入的两个磁跑道基本上是径向地优选地呈v形或y形地设置,以共享铁磁或亚铁磁层的公共第二区域——所述第二区域由此表示逻辑门的逻辑输出——并且共享功能层的第二功能部分,其中,两个磁跑道的第一区域由可确定磁化的磁偏置区域分开,并且其中,功能层的第三区域被布置成与两个磁跑道的径向布置(优选地v形或y形布置)对齐的环形段形状的形式。

21.因此,本发明还公开了可重新配置的nand(与非)和nor(或非)逻辑门,并通过电流引起的畴壁运动来执行操作。因此,可以级联若干个nand门来构建xor(异或)门和全加器门(full adder gates),从而示范逻辑电路中的磁数据和设备互连的电控制。本发明为可扩展的全电磁逻辑提供了一种可行的平台,为逻辑存储器的应用铺平了道路。

22.逻辑门的优选实施方式由其他从属权利要求给出。

23.在下文中,将参照附图更详细地描述本发明的优选实施方式,这些附图描绘在以下图中:

24.图1相邻纳米磁体之间的手性耦合和电流驱动的dw反转;

25.图2示意性地示出了电流驱动的dw反转器;

26.图3示意性地示出了可重新配置的nand/nor逻辑门;

27.图4示意性地示出了数据流和级联的dw逻辑电路的电控制;

28.图5示意性地示出了oop-ip-oop结构中的电流驱动的dw反转的简单模型;

29.图6具有直ip区域的dw反转的微磁模拟;

30.图7窄线(narrow wire)中针对电流驱动的dw反转的dmi-oop各向异性相图;

31.图8用于操作可靠性测量的(a)nand门和(b)nor门的时间序列的moke图像;

32.图9示意性地示出了针对mtj/跑道混合结构的建议;

33.图10各种级联dw逻辑电路;

34.图11示意性地示出了磁dw逻辑元件的示例;

35.图12根据电流密度的、跑道的均匀oop区域中的dw速度和not(非)门中的有效dw速度;

36.图13操作期间nand门的时间序列的moke图像和对应示意图;

37.图14示意性地示出了dw逻辑的传播延迟时间的概念;

38.图15nand门中逻辑操作的霍尔(hall)测量;

39.图16示意性地示出了设备构造和磁性表征;

40.图17具有直ip区域的dw反转器中的dw反转;

41.图18示意性地示出了非对称dw反转器的非互易操作;

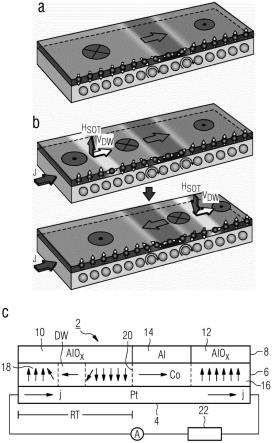

42.图19对称和非对称dw反转器两者中的电流驱动的dw反转的微磁模拟;以及

43.图20示意性地示出了通过级联一个非对称dw反转器和一个对称dw反转器而获得的正确工作的dw二极管。

44.用于存储和/或处理数据的手性磁畴壁(dw)逻辑的本发明利用了由自旋轨道矩(spin-orbit torque,sot)h

sot

引起的磁dw运动的效率和速度,并且利用了具有竞争磁各向异性和界面dzyaloshinskii-moriya相互作用(dzyaloshinskii-moriya interactaion,dmi)的相邻磁体之间的手性耦合(图1a)。基于该耦合,可以使用电流来反转dw,即将上/下dw转换成下/上dw,或者反之亦然。此处,跑道中和

⊙

的磁化方向分别表示布尔逻辑“1”和“0”。

45.在图1b中,示出了dw反转器的设计,其包括嵌入在具有平面外(out-of-plane,oop)磁化的跑道中的平面内(in-plane,ip)磁化区域。由于在ip区的任一侧的两个oop区通过dmi耦合,一个oop区的反转引起另一个oop区的反转,导致相当于not门的、沿跑道行进的dw的反转。

46.图1c示意性地示出了如针对图1a和图1b所描述的设备2的截面图。设备2包括由导电材料诸如pt制成的支撑层4。设置在所述支撑层4上的铁磁或亚铁磁层6(共层(co-layer))能够显示出磁自旋各向异性并提供磁跑道rt。此外,功能层8设置在所述铁磁或亚铁磁层6上,在该示例中,所述功能层8具有第一金属氧化物部分10和第二金属氧化物部分12以及在第一金属氧化物部分10和第二金属氧化物部分12之间的金属部分14,其中,功能层的材料使得在其金属氧化物形式下铁磁或亚铁磁层6能够具有垂直于层4、6、8的平面的oop磁化(oop=平面外),并且使得在其金属形式下铁磁或亚铁磁层6能够具有仅平行于层的平面的ip磁化(ip=平面内)。

47.因此,垂直且向上取向的oop磁化可以表示逻辑“0”,而向下取向的oop磁化可以表示逻辑“1”,或者反之亦然。响应于将由第一金属氧化物部分10覆盖的铁磁或亚铁磁层6的第一区域18中的畴壁dw沿着磁跑道rt朝向在功能层8的第一金属氧化物部分10至金属部分

14的过渡处给出的界面20移动,所述布尔逻辑“1”或逻辑“0”能够被编码在由第二金属氧化物部分12覆盖的铁磁或亚铁磁层6的第二区域16中。向支撑层4提供电流密度j的电流源22能够使用施加至支撑层4的受控电流脉冲来使磁畴壁dw可确定地沿着磁跑道rt来回移动。

48.在该实施方式中,通过覆盖铁磁或亚铁磁层的金属氧化物层和金属层来实现磁自旋各向异性。当然,还存在其他控制磁自旋各向异性的可能性,例如:

49.a)根据aik jun tan等人的离子控制各向异性,“magneto-ionic control of magnetism using a solid-state proton pump”,nature materials,第18卷,2019年1月,35页至41页以及fanny ummelen等人,"racetrack memory based on in-plane-field controlled domain-wall pinning",scientific reports,7:833,doi:10.1038/s41598-017-00837-x;

50.b)根据d.chiba等人的铁磁相变的电控制,“electrical control of the ferromagnetic phase transition in cobalt at room temperature”,nature materials,第10卷,2011年11月,853页至856页,以及根据t.maruyama等人“large voltage-induced magnetic anisotropy change in a few atomic layers of iron”,nature nanotechnology,第4卷,158页至161页(2009年);

51.c)根据j.h.franken等人的畴壁注入和钉扎(pining),“precise control of domain wall injection and pinning using helium and gallium focused ion beams”,j.appl.phys.109,07d504(2011年)。

52.为了说明dw反转器的操作,如图2所示,制造了一组具有50nm宽的v形ip区域的pt/co/alo

x

的oop磁性纳米线,其使用选择性氧化工艺图案化(图2a)。在该oop磁性纳米线中,pt表示支撑层,co表示铁磁层/磁性跑道,alo

x

表示功能层(alo

x

=金属氧化物形式)。

53.dw运动由电流驱动(图2b)并使用极向磁光克尔效应(magneto-optic kerr effect,moke)显微镜跟踪。从oop-ip-oop结构的初始下-右-上磁化配置开始,从左侧oop区域注入dw(图2c)。

54.通过施加电流脉冲序列,dw沿电流方向朝向ip区域(由功能层的金属部分覆盖的区域)移动,如左手手性n

é

eldw所期望的。当dw遇到ip区域时,ip磁化从

→

切换至

←

,伴随着在ip区域左侧的dw的消灭和在ip区域右侧的具有相反极性的新dw的成核。通过扫描透射x射线显微镜(stxm)和微磁模拟的组合来提供对dw反转的微观机制的了解(图2d)。当入射的dw接近ip区域时,它被自旋轨道矩sot压向ip区域,这又增加了静磁和交换能量。

55.所得到的紧凑的高能量自旋结构只能通过借助于sot消灭入射的dw并切换ip磁化而展开。当ip磁化从

→

切换至

←

时,由于手性耦合,畴在ip区域的右侧成核。由于来自v形区域两侧的手性耦合的附加贡献,在v形反转器的尖端处促进了该过程。因此,窄v形ip区域(v形金属区域14)的优化设计便于ip磁化的切换和新畴的成核。结果,dw被有效地传输通过ip区域并被转换成dw。

56.针对入射的dw发生类似的反转过程,使得反转器有效地反向了跨越ip区域

行进的磁畴的磁化,如图2e所示。不仅可以使用电流反转单个dw,而且可以反转dw的序列,从而反转沿着磁跑道rt传播的磁畴的序列。这是手性耦合的纳米磁性结构的独特特征。

57.在用于构建not门的原理的基础上,阐述了如何实现可重新配置的nand/nor门。该门使得电流驱动的dw逻辑的概念在功能上完整,因为可以使用nand门或nor门的组合来实施任何布尔函数。该门的核心结构(图3a)由铁磁层中的四个oop区域组成,这四个oop区域形成两个逻辑输入(input)(输入a、输入b)、一个偏置(bias)和一个逻辑输出(output),它们经由ip区(由功能层8的金属部分14覆盖的铁磁或亚铁磁层的区域)连接。参照针对图1c使用的符号,逻辑门(nand或nor)包括表示逻辑门的逻辑输入的两个磁跑道rt。磁跑道rt基本上径向取向,优选为v形或y形取向,以便共享铁磁或亚铁磁层6的公共第二区域16,所述第二区域16由此表示逻辑门的逻辑输出。在该区域中,它们还共享功能层8的第二金属氧化物部分12和支撑层4的对应部分,其中,两个磁跑道rt的第一区域18由可确定的oop磁化的磁偏置区域分开。当然,该磁偏置区域也可以被设计为磁跑道rt,从而允许在偏置区域中向上或向下切换磁化的oop取向。功能层8的金属区域14被相应地布置成与两个磁跑道(rt)的径向布置(优选地v形或y形布置)对准的环形段形状的形式(a ring segment shaped form)。

58.为了说明nand门的功能,制造了具有相同核心结构和不同逻辑输入配置的四个设备。针对每个设备,两个dw储存器通过磁跑道rt连接至输入。四个逻辑输入配置“11”、“10”、“01”和“00”通过在一些dw储存器之后放置反转器来实现。通过施加1koe的oop磁场将两个dw储存器和偏置设置为逻辑“0”。施加电流脉冲,(

⊙

)磁畴从具有(不具有)反转器的dw储存器传播,将逻辑输入定义为“1”(“0”)。作为手性耦合的结果,输出磁化取决于输入和偏置的相对对准(图3b和图3c),这类似于多数门(majority gate)。因此,针对

⊙

偏置,只有当两个输入磁化都为时,输出磁化切换至

⊙

。否则,输出磁化为

59.如磁力显微镜(mfm)图像(图3d)所示,逻辑输出的磁化方向针对逻辑输入“11”是

⊙

(“0”),针对逻辑输入“10”、“01”和“00”是(“1”)。逻辑输入和输出之间的这种关系对应于针对nand门所需的逻辑操作(图3c)。通过将偏置的方向改变为如图3e所示,nand门可以被重新配置成nor门。在后一种情况下,只有当两个输入磁化都为

⊙

时,输出磁化才为因此,可以通过切换偏置端子来在nand和nor之间重新配置当前逻辑门,从而允许在运行时间期间进行快速逻辑重新配置。

60.使用电流驱动的dw运动随着时间向同一门提供一系列不同的逻辑输入来演示单个nand门的操作(图3f)。在该设备中,在左侧跑道中放置三个dw反转器,在右侧跑道中放置两个dw反转器。这意味着电流脉冲序列将生成从“00”至“11”至“01”至“11”至“10”的逻辑输入序列。对应的逻辑输出将随时间分别从“1”至“0”至“1”至“0”至“1”变化。针对每个操作,给出这两个输入的dw可能不同时到达门。这通过引入足够的传播延迟时间来减轻(见方法)。在实际设备中,这可以通过对电流进行时钟计时来实现。此外,可以使用在磁跑道上制造的磁隧道结(mtj)来控制逻辑输入和偏置端子,这也可以用于输出的电读出(见方法)。

61.除了形成完整的逻辑集合之外,手性dw跑道满足逻辑电路中实际实现的三个附加要求,即输入选择性、数据交叉、和不同逻辑门的级联。通过图4a中的经过y形结构的电流驱动的dw传播,可以电选择逻辑输入。简单的交叉结构使得dw能够在正交跑道中传播(图4b),

这简化了交叉的设计,避免了在传统的基于电荷的电路中使用的金属桥的复杂性。

62.此外,由于当前的逻辑输入和输出是基于相同的物理现象,可以直接级联几个逻辑门,而不需要在磁信号与电信号之间的附加转换器。作为示例,在图4c中示出了通过级联四个nand门以形成xor门而创建的二进制半加法器,并且在图4d中还示出了通过级联15个nand门的全加器操作。该电路还说明了可以用于驱动下一个逻辑门的输入的单个输出的扇出的可能性。

63.甚至可以创建具有反馈回路的磁逻辑电路。这通过使用外部电路来读取输出并使用mtj将其写回至输入来实现,或者通过使用具有反转的电流方向的附加跑道来将dw从输出驱动回输入来实现。

64.针对设备应用,也可以解决磁dw逻辑电路的可扩展性和效率。因为由dmi引起的手性耦合在磁矩的尺度上是有效的,所以可以使用先进的光刻技术将逻辑门的尺寸缩小至几nm。逻辑操作的速度与dw速度有关,针对由sot驱动的手性dw,dw速度可以达到几百m/s。操作时间可以从dw跨越门传输所需的时间来估计,针对按比例缩小至10

×

10nm2的反转器,该时间可以快到几十ps(见方法)。在0.8

×

1nm2跑道中单个not操作的能量消耗为约20pj,其在具有10

×

10nm2占用面积的结构中将按比例缩小至20aj以下(参见方法)。

65.磁输入和输出的非易失性进一步节省了能量,因为磁dw逻辑电路在空闲时不消耗功率并且在断电后不需要重新加载数据。这些特征使得全电磁dw逻辑针对在现代电子设备中普遍存在的低功率、“即时启动”微电子处理器中使用具有吸引力。

66.在下面进一步说明附图:

67.图1示出了相邻纳米磁体之间的手性耦合和电流驱动的dw反转。图1a示意性地示出了由dmi引起的磁性手性耦合。在选择性氧化之后,相邻oop(氧化的,深灰色阴影的)和ip(未氧化的,浅灰色阴影的)区域的磁化与pt/co/alo

x

中的左旋手性对齐。图1b示意性地示出了电流驱动的dw反转,其在dw跨越ip区域传输时发生。白色阴影区域是dw,并且由sot引起的有效场hsot的方向和dw速度vdw用箭头表示。在pt/co/alo

x

中,和dw两者在与电流j相同的方向上移动。

68.图2示出了电流驱动的dw反转器。图2a示意性地描绘了not门和电流驱动的dw反转器。深灰色和浅灰色阴影区域分别指示具有oop和ip各向异性的区域。图2b示出了dw测量设置的3d透视图中的七个并行dw反转器的sem图像。指示了电流脉冲的方向。图2c示出了具有配置的针对从左边入射的dw的dw反转的moke图像序列。磁跑道的边缘由深灰色虚线表示,反转器的位置由白线表示。moke图像中的跑道中的亮和暗对比分别对应于

⊙

和磁化。

69.图2d示出了通过stxm测量的针对具有配置的入射dw的dw反转的xmcd图像序列。在施加一个电流脉冲之后捕获每个图像。xmcd图像中的亮和暗对比分别对应于

⊙

和磁化。反转过程的微磁模拟显示在每个图像的右侧,磁化方向由色环表示。

70.图2e描绘moke图像,其示出了使用电流脉冲进行的跨越ip区域驱动的畴的反转。在图2c和图2e中施加的脉冲的电流密度和持续时间是7.5

×

10

11

a/m2和50ns,而针对图2d,它们是1.1

×

10

12

a/m2和1ns。比例尺在moke图像中为3μm,针对xmcd和模拟图像为500nm。

71.图3示意性地示出了可重新配置的nand/nor逻辑门。图3a示出了可重新配置的nand/nor逻辑门的彩色sem图像和对应的逻辑电路符号。不同的灰色阴影分别表示具有oop和ip磁各向异性的逻辑门中的区域和pt条。图3b示出了针对nand门的两个逻辑输入中的磁化、偏置和逻辑输出之间的关系的示意图。图3c是针对可重新配置的nand和nor逻辑操作的真值表。图3d和图3e表示针对具有偏置“0”(d)和“1”(e)的“11”、“10”、“01”和“00”的输入的不同逻辑操作的mfm图像,以及它们对应的逻辑电路符号。通过施加1koe的oop磁场将dw储存器(每个图像顶部的圆形盘)和偏置设置为逻辑“0”。图3f示出了moke图像序列和对应的示意图,其示出了具有由电流驱动的逻辑输入序列的单个nand门的操作。通过施加1koe的oop磁场将初始磁化设置为

⊙

。示意图中的浅灰色和深灰色分别对应于

⊙

和磁化。逻辑门的边界由虚线表示,反转器的位置由白线表示。指示在每个moke图像之前施加的电流脉冲的方向和数量(电流密度7.5

×

10

11

a/m2和脉冲长度30ns)。mfm和moke图像中的设备区域中的亮和暗对比分别对应于

⊙

和磁化。所有比例尺均为1μm。

72.图4示意性地示出了数据流和级联dw逻辑电路的电控制。图4a示出了通过y形结构的数据流交换。左侧:设备的彩色sem图像和对应的逻辑电路符号。右侧:当电流流经上跑道(顶部)和下跑道(底部)时,磁配置的mfm图像。图4b表示moke图像的序列,其示出了通过交叉结构的数据流的电控制。指示电流脉冲的方向和数量(电流密度9

×

10

11

a/m2和脉冲长度30ns)。在顶部示出了交叉结构的sem图像和对应的逻辑电路符号。图4c示意性地示出了通过级联四个nand门而制造的xor门。左侧:xor逻辑门的sem图像和对应的逻辑电路符号。右侧:具有不同的逻辑输入“11”、“10”、“01”和“00”的xor逻辑门的mem图像。通过施加1koe的oop磁场将dw储存器和偏置设置为逻辑“0”。sem图像中的不同灰色阴影分别表示具有oop和ip磁化的区域以及pt条。图4d)示意性地示出了全加器门。顶部:具有输入操作数为“a=0”、“b=1”以及进位位为“cin=1”的全加器的逻辑电路符号。底部:全加器磁电路的mfm图像。moke和mfm图像中的设备区域中的亮和暗对比分别对应于

⊙

和磁化。所有比例尺均为1μm。

73.方法

74.a.设备制造

75.使用dc磁控管溅射在基础压力《2

×

10-8

托和沉积ar压力3毫托下将磁性膜沉积在硅衬底上的200nm厚的sin

x

层上,并通过电子束光刻进行图案化。将pt(5nm)/co(1.6nm)/al(2nm)的连续膜通过负性抗蚀剂(ma-n2401)掩模使用ar离子研磨成条。在这些磁条中,上面的co/al双层通过高分辨率正抗蚀剂(pmma)掩模被研磨以产生dw跑道和逻辑设备。为了在这些磁性结构中限定ip区,通过电子束光刻在al层之上图案化第二pmma掩模。在10毫托的氧压力下使用低功率(30w)氧等离子体,未保护的al层(图1c中的区域10和12)被氧化以在co层中引起垂直磁各向异性。最后,使用将电子束蒸发与剥离处理相结合的电子束光刻技术制造cr(5nm)/au(50nm)电极。设备制造的主要步骤如图16a所示。

76.使用极性moke测量证实oop区域(暴露于氧等离子体)和ip区域(使用pmma掩模保护)的不同各向异性(图16b)。有效的oop磁各向异性场是3.94koe,其是从应用了ip磁场的反常霍尔效应测量中获得的(图16c)。通过测量dmi引起的手性耦合,估计界面dmi常数d为-0.9

±

0.1mj/m2。

77.b.电测量配置

78.磁dw运动和逻辑操作由hp agilent 8114a高压脉冲发生器和avtech超高速脉冲发生器生成的电流脉冲驱动。脉冲发生器可以提供可变电压和脉冲宽度的脉冲。通过将标称电压除以设备电阻和横截面积来计算电流密度,并针对每个操作指示电流密度。针对每个设备描绘了电流脉冲的方向,并在图11中进行了总结。

79.c.mfm测量

80.使用安装在振动和声音隔离台上的bruker dimension icon扫描工作站,使用涂覆有cocr的尖端进行mfm测量。为了在测量期间最小化来自mfm尖端的杂散场的影响,在样品上旋涂薄pmma层(~20nm)以增加尖端和磁性膜之间的距离。

81.d.moke显微镜测量

82.使用定制的宽场moke显微镜记录moke图像。在施加1koe的大的正oop磁场之后捕获背景图像。从随后的图像中减去背景图像以获得具有磁对比的差异图像。为了准备图2c所示的dw的初始状态,首先使用oop磁场使跑道饱和。移除磁场,留下跑道磁化的oop,在v形ip区域具有由手性耦合产生的小反向区域。然后,在与图2b所示方向相反的方向上施加电流脉冲,以便在dw反转器的左侧产生单个dw(图2c)。

83.e.stxm测量

84.使用扫描透射x射线显微镜在paul scherrer研究所(5232villigen psi,瑞士)的瑞士光源的pollux光束线处对dw反转器的磁性构造成像。利用x射线磁性圆二色性(xmcd)以垂直入射在co l3吸收边缘探测磁化状态。使用stxm测量的设备在x射线可穿透的sin

x

膜上制造。

85.f.微磁模拟

86.为了理解dw反转的机制,使用包含2048

×

1024

×

1单元的计算盒、使用mumax3码、采用使用以下磁参数进行的2

×2×

1.6nm3离散化进行微磁模拟:饱和磁化强度ms=0.9ma/m,有效oop各向异性场h

eff

=150mt,交换常数a=16pj/m,自旋霍尔角pt θ

sh

=0.1,以及界面dmi常数d=-1.5mj/m2。

87.g.用于dw反转的机制

88.为了阐明oop-ip-oop结构中dw反转的基本机制,考虑了简单的模型。dw反转过程可以根据在非共线磁体中生成的有效dmi场来解释,其中dmi矢量位于磁性薄膜的平面中。该有效dmi场由下式给出:

89.然后可以考虑dw由sot朝向ip磁化区域驱动的情况(见图5a)。在平衡时,ip磁化区域与周围畴一起形成配置,其通过由g

dmi

(ip)指示的dmi场(沿+x指向)来稳定。在施加电流时,磁化受到由sot引起的有效场h

sot

的影响,其由下式给出:

90.91.其中,θ

sh

、j、e、ms、t、m和σ是在pt/co界面处的普朗克常数、自旋霍尔角、电流密度、电子电荷、饱和磁化强度、磁层厚度、磁化方向和自旋极化方向。由于手性耦合,在dw中间的磁化沿-x指向。

92.如图5b所示,h

sot

(dw)沿+z指向,使得dw将沿电流方向传播。一旦dw接近ip区域,ip区域中的磁化经历偶极场h

dip

(ip),该偶极场由dw的沿-x指向的ip磁化生成。sot还向ip区域压缩入射dw,这反过来又增加了dw能量。这导致紧凑的高能量自旋结构,其包含具有尾对尾ip磁化的两个紧密间隔的区域,如图5b中的相关磁电荷所示:一个ip磁化区域在dw的中间,磁化沿-x指向,另一个ip磁化区域在反转器中,具有沿+x指向的磁化。

93.在某个时间点,偶极场变得足够强以借助于sot将ip区域中的磁化从+x切换至-x(图5b和图5c)。同时,ip区域左侧的高能量自旋结构崩溃,导致图5b中灰色所示的ip区域左侧的畴的消灭。在ip区域中的磁化反转之后,由于h

dmi

(oop)沿-z指向,反向畴在ip区域的右侧成核(在图5c中以灰色示出)。磁化在得到的dw中间沿+x指向并且h

sot

(dw)沿-z指向,使得这个新的dw然后通过电流朝向+x传输(图5c)。

94.虽然这种简单的模型提供了对dw反转机制的理解,但是详细的磁化动力学更复杂。因此,相应地进行了微磁模拟。此处,dw由电流密度为3

×

10

12

a/m2的电流在包含直的、30nm宽的ip区域的窄线中驱动(图6a)。oop各向异性场在oop区域中设置为hk=1.5koe,在ip区域中设置为零。沿所述线在三个不同位置记录磁化的所有三个分量:在ip区域的中心,以及在每一侧距中心30nm(见图6a中的点)。

95.在图6b至图6d中,示出了磁化如何响应接近的dw。当dw接近ip区域的左侧时,ip区域左侧的磁化从-z反向至+z(见图6b)。ip区域中的磁化沿着图6c所示的路径从+x反向至-x,以减少与所累积的静磁电荷相关联的能量(在图6c中示意性地示出)。然后通过手性耦合迫使ip区域右侧的磁化从+z切换至-z(见图6d)。

96.dmi在电流驱动的dw反转的实现中是关键的,不仅为了实现电流驱动的dw运动,而且由于其在反向畴的成核中的作用。通过改变ip区域中的dmi值和oop各向异性,利用微磁模拟来确定dw反转过程中dmi的作用。在图7中针对包含直的、30nm宽的ip区域的窄线中的3

×

10

12

a/m2的电流密度示出了电流驱动的dw反转的dmi-oop各向异性相图。针对ip区域中的零oop各向异性,当d《-1mj/m2时,dw可以被反转。如果dmi被减少,则它不能提供足够的手性耦合来使反向畴成核,使得入射dw不能被反转。

97.通过将oop各向异性引入至从pt/co界面预期的ip区域中,用于dw反转的能量减少并且dmi操作窗口增加。

98.为了验证ip宽度对dw反转过程的影响,已经对针对ip区域的各种宽度的反转器中的磁化动态进行了附加的微磁模拟。电流密度为3

×

10

12

a/m2和d=-1.5mj/m2的模拟结果在表1中给出。

99.表1|针对j=3

×

10

12

a/m2和d=-1.5mj/m2的dw反转器的仿真结果。

[0100][0101]

各向异性k

oop

(ip区域)和k

oop

(oop区域)分别表示ip区域和oop区域中的单轴oop各向异性。对号(叉号)表示反转的dw可以(不可以)从ip区域传播至oop区域。

[0102]

此处,对号指示反转的dw根据需要从ip区域传播至oop区域。如果ip区域太窄(《25nm),则反转器任一侧的oop区域是强反平行耦合的,并且由电流感应的sot不够强以克服手性耦合。

[0103]

如果ip区域的宽度太大(》35nm),则手性耦合变得太弱而不能在ip磁化的左侧和右侧给出oop磁化的反平行耦合。然后,dw在ip区域中被简单地消灭,而在反转器的另一侧没有出现任何进一步的磁化动态。

[0104]

通过实验证实了微磁模拟的结果:针对在800nm宽的跑道中的直的dw反转器,dw成功地跨越50nm宽的dw反转器传输,但没有成功地跨越100nm宽的反转器传输。如表1所示,通过在ip区域中包括小的oop各向异性,可以增加ip区域的操作窗口。

[0105]

h.dw反转器的ip区域的形状的影响

[0106]

此处,从直ip反转器的测量开始,在ip区域的宽度为50nm的情况下,在实验上比较直的和v形dw反转器的性能。如图17a中的stxm图像所示,当dw遇到ip区域时,dw将在ip区域的左侧消灭,并且具有相反极性的新dw将在ip区域的右侧成核。在具有直ip区域的同一反转器中执行若干反转操作,并且发现反向磁畴在不同位置成核(图17b)。这意味着反向磁畴的成核由随机热波动或局部不均匀性辅助。

[0107]

为了提高dw反转器的可靠性,已经实现了v形ip区域,其具有两个主要优点:首先,v形的尖端为反向磁畴提供了容易的成核位置。这是因为,在v形的尖端,输出oop区域被输入oop区域包围,并经历最强的反平行手性耦合。在stxm测量中,针对五次操作中,发现五次反向磁畴的成核都位于v形的尖端。其次,ip区域的v形导致较低的静磁能量,因此降低了dw反转的能垒。如图17c所示,测量了在具有v形和直ip区域的dw反转器中测量的有效dw速度(见在方法中逻辑操作速度的估计中概述的方法)。在v形ip反转器中dw跨越ip区域传输的速度高于在直ip反转器中dw跨越ip区域传输的速度,并且在v形ip反转器中速度的标准偏差小于直ip反转器中速度的标准偏差。这证明了v形ip区作为dw反转器的更高效率和可靠性。

[0108]

i.逻辑操作速度的估计

[0109]

此处已经研究了not门中的逻辑操作速度。首先,测量跑道的均匀oop区域中的dw速度v

dm

。然后,在n个电流脉冲之后,跨越not门从s1至s2确定dw位移l

dw

(见图12中的示意图)。由此,dw跨越not门传输所花费的时间t

not

已被花费,因此当dw跨越not门传输并被反转时,dw的有效速度v

not

为:

[0110][0111]

其中t

pulse

和l

not

分别是电流脉冲的长度和not门的长度。使用这种方法,我们可以确定根据电流密度的v

dw

和v

not

(图12)。针对高电流密度,脉冲长度减小至2ns以减少发热,数据在图12的插图中给出。已经发现,针对1.65

×

10

12

a/m2的电流密度,not门中的dw速度可以达到160

±

17m/s。该dw速度的值用于估计能量消耗。

[0112]

此处,使用按比例缩小至10

×

10nm2的图11中指示的尺寸来估计dw跨越dw反转器传输的时间。采用160m/s的实验确定的反转器有效dw速度,dw跨越缩小的反转器传输的时间≈60ps。为了更精确地估计,针对尺寸为10

×

10nm2的缩小的反转器执行微磁仿真。在这种小规模下,设备设计受到可纳米制造的特征尺寸的限制。因此,考虑直ip区域而不是v形ip区域,宽度为10nm。采用118m/s的模拟有效反转器dw速度,dw跨越反转器传输的时间为85ps,这与上述粗略估计类似。通过优化材料以增加dw速度,例如通过使用非晶磁性材料(例如cofeb而不是co)和设备设计,可以进一步改进操作速度。

[0113]

使用类似的针对dw反转器的方法,从实验中估计nand门中逻辑操作的速度。为此,使用moke成像捕获在输入储存器中具有两个dw反转器的nand门的操作。在施加电流脉冲之后,dw传播通过nand门并执行逻辑操作(见图13中的moke图像和对应示意图)。根据这些图像,在电流密度为7.5

×

10

11

a/m2,有效dw速度为v

nand

=10.8m/s的情况下,dw跨越nand门传输的时间被确定为t

nand

=74.1ns。

[0114]

j.dw电路中的同步和传播延迟时间

[0115]

由于存在导致dw钉扎(pinning)的缺陷和电流驱动的dw运动的固有随机性质,dw在逻辑门处的到达时间可能不同。在电子逻辑电路中,这通常通过为每个操作引入传播延迟时间来解决,即,电路以比最长的内部传播延迟时间慢的速率循环。传播延迟时间的相同概念可以应用于当前的磁dw逻辑门,使得可以获得与输入畴的到达时间无关的稳定输出。换句话说,利用足够的传播延迟时间,所有的dw将到达逻辑门,这将导致给定逻辑操作的正确输出。

[0116]

为了展示传播延迟时间的引入可以如何改进门操作可靠性,已考虑nand门的最简单情况,其中逻辑输入随时间从“00”改变至“11”。如图14a示意性所示,针对逻辑输入a和b的dw到达时间不同。在这种情况下,输入a从“0”至“1”的改变比输入b的情况慢,即ta>tb,其中ti(i=a,b)是输入改变的时间。

[0117]

一旦两个dw都到达门,反向磁畴的成核将花费一些时间,这取决于nand门中的有效dw速度。正确磁畴传播至输出跑道之后的时间被定义为所需的传播延迟时间t

delay

。具有“11”逻辑输入的nand门被制造成具有不同的输入跑道长度,以给出两个逻辑输入的不同到达时间。在施加电流脉冲时,dw在左和右输入跑道两者中传播。这是测试逻辑门的传播延迟时间可靠性的最关键配置。如图14b所示,所有设备给出正确的输出“0”,表明磁dw逻辑门的输出与输入dw的到达时间的差异无关。

[0118]

针对nand门中的所有逻辑操作,一般来说,操作包括(i)输入跑道中的dw传播,(ii)跨越逻辑门的dw传输及(iii)输出跑道中的dw传播。总操作时间以及因此所需的传播

延迟时间然后可以表示为:

[0119][0120]

其中l

input

、l

out

以及l

nand

分别是输入跑道、输出跑道、nand门的长度。v

dw

和v

nand

分别是磁跑道和nand门中的dw速度。假设磁跑道和nand门中的dw速度具有正态分布:

[0121][0122]

其中和σ

dw

(σ

nand

)表示磁跑道中dw运动的速度分布的平均值和标准偏差(nand门)。为了获得逻辑操作成功的97.5%的概率(见图14c),所需的传播延迟时间可以被估计为

[0123][0124]

为了证明足够的传播延迟时间可以改善针对nand门中在统计上有效次数的操作的可靠性,将nand门的输出置于霍尔十字(hall cross)上(图15a)并且执行1172次测量。针对每次测量,nand门被使用oop磁场进行饱和,以将初始磁化方向在所有储存器中设置为

⊙

,并且施加一系列电流脉冲。通过施加dc电流时的反常霍尔(hall)效应来测量输出。脉冲源和dc源由偏置器分开。

[0125]

如图15b中霍尔电阻的改变所示,输出从“0”变为“1”并回到“0”的状态。使用对nand门执行的moke测量来验证电测量(见图15b中的moke图像)。通过使用14个电流脉冲(相当于14

×

30ns的传播延迟时间(propagation delay time)),nand门的可靠性增加至》95%(图15c)。

[0126]

针对级联逻辑电路,传播延迟时间由电路中最长的dw传播路径确定。为了减少传播延迟时间,可以采用几种可能的方法,例如电路尺寸的缩放、dw速度的增加和钉扎的减少。

[0127]

k.逻辑门可靠性

[0128]

为了实现逻辑门的大规模实现,可靠的操作是必要的。此处,根据设备至设备可靠性(device-to-device reliability)和操作可靠性来评估两个基本not门和nand门的可靠性(表2)。

[0129]

表2|not门和可重新配置nand门的可靠性。

[0130]

[0131]

*设备至设备可靠性是给出正确输出的功能设备的数量/设备的总数。

[0132]

*操作可靠性是单个设备的成功操作的数量/执行的操作的总数。

[0133]

为了证明not门的高设备至设备可靠性,制造了35个not门,其中34个not门(97%)被显示为成功操作。在具有100%操作可靠性的单个设备中,还以4

×

10

11

a/m2至1.65

×

10

12

a/m2范围内的各种电流密度执行not操作。

[0134]

为了测试nand门的设备至设备可靠性,制造了56个具有不同逻辑输入的nand门,并且发现平均成功率为42/56(75%)。一些设备的失效可能与由材料中的缺陷或纳米制造产生的不规则特征导致的dw的钉扎有关。nand门中磁跑道的宽度为200nm,而not门中磁跑道的宽度为800nm,这意味着边缘粗糙度可以引起更多的钉扎。针对四个所选择的设备,对每个设备执行20次操作(图8),并且它们都给出正确的输出,显示高操作可靠性。

[0135]

还考虑了针对不同逻辑输入的设备至设备可靠性的分布。针对56个nand门,每种类型的14个nand门被制造成具有逻辑输入“00”,“11”,“01”和“10”。针对逻辑输入“00”、“11”、“01”和“10”,给出正确输出的nand门的数量/nand门的总数分别是13/14、11/14、10/14和8/14。针对“00”和“11”输入的设备至设备可靠性稍高于针对“01”和“10”输入的设备至设备可靠性。这可以通过考虑以下给出的针对“00”、“11”、“01”和“10”输入的“1”和“0”输出之间的能量差来理解:

[0136]

δe

1/000

=-(2e

input

+e

bias

)

[0137]

δe

1/011

=2e

input-e

bias

[0138]

δe

1/001

=-e

bias

[0139]

δe

1/010

=-e

bias

,(8)

[0140]

其中,分别地,δe

1/0ij

是针对输入“ij”(“ij”=“11”、“00”、“01”或“10”)的“1”和“0”输出之间的能量差,e

input

是输出与输入之间的耦合强度,e

bias

是输出与偏置之间的耦合强度。从该组式子,得出针对“11”输入的稳定输出为“0”(δe

1/0

>0)并且针对“00”、“01”和“10”的其他输入的稳定输出为“1”(δe

1/0

<0),其满足nand操作的真值表。针对实验中使用的nand门,偏置(bias)的大小比输入的大小小一点。由于由ip区域分开的两个oop磁化之间的耦合能量与其边界的长度成比例,所以输出和输入磁化之间的耦合能量大于输出和偏置磁化之间的耦合能量,即e

input

>e

bias

。因此,针对nand操作,|δe

00

|>|δe

11

|>|δe

01

|=|δe

10

|。不同逻辑输入的正确和错误输出之间的能量差的趋势与不同逻辑输入的设备至设备可靠性的趋势很好地相关。

[0141]

还测试了图4d所示的级联逻辑电路(全加器)的操作可靠性。成功操作的数量/执行的操作的总数量为28/30。

[0142]

因此,在本概念验证实验中,已经证明了磁门的高可靠性。还必须强调的是,在制造工艺、设备设计和材料特性的优化方面,存在大量的空间来提高设备至设备的可靠性。

[0143]

l.逻辑输入的电控制和逻辑输出的检测

[0144]

针对图3f所示的概念验证实验,通过将反转器放置在输入跑道上,确保了特定dw到达输入。在使用oop磁场进行饱和之后,将跑道中的磁化方向设置为

⊙

。在施加电流时,传播的dw的磁化在它们跨越每个反转器传输时被反向。通过将不同数量的反转器放置在输入跑道中的不同位置处,生成逻辑输入序列以便随时间在同一门处获得不同输入,并且以此方式展示其实时操作。还示出了y形结构中的dw传播的电切换可以用于注入dw并定义特定

的逻辑输入(图4a)。

[0145]

针对缩小的逻辑电路,在逻辑输入跑道上制造的磁隧道结(mtj)将提供更紧凑的方法来控制逻辑输入(图9)。实际上,已经表明,磁跑道上的mtj可以用于经由自旋转移力矩(stt)写入磁畴。因此,在磁跑道上制造的mtj可以用于电控制逻辑输入。为了检测逻辑输出,在我们的概念验证实验中使用mfm、moke显微镜和霍尔测量。针对缩小的逻辑电路,在输出跑道上制造的mtj可以用于电检测逻辑输出。

[0146]

此外,实际上不仅能够读取门的输出,而且能够使用mtj设备将其传输至另一门的输入,以便实现信息反馈。反馈针对顺序逻辑操作诸如在触发器门中执行的顺序逻辑操作是关键的。因此,mtj/跑道混合结构也可以提供执行复杂逻辑的紧凑方法。

[0147]

m.小型逻辑设备的能耗

[0148]

为了估计实验中使用的反转器的能量消耗,考虑包含v形ip区域的区域,其中dw被反向。由底部pt层中的功率-延迟乘积计算反转器每次操作的能量消耗:

[0149][0150]

其中j、ρ、w、l、h和v

not

分别表示电流密度、pt的电阻率、反转器宽度、反转器长度、pt层的厚度(5nm)和反转器中的有效dw速度。取w

×

l=0.8

×

1.0μm2的反转器尺寸,ρ=30.0μω

·

cm的薄膜中的pt电阻率,以及j=1.65

×

10

12

a/m2和v

not

=160m/s的实验测量的电流密度和有效反转器dw速度,根据式9计算反转器每次操作的能量消耗为20.4pj。

[0151]

针对按比例缩小的反转器的能量消耗的粗略估计,反转器的尺寸已经按比例缩小,同时保持pt层厚度、pt电阻率、电流密度和跨越反转器的有效dw速度的值与实验中测量的相同。具有图11中指示尺寸的按比例缩小至10

×

10nm2的反转器的每次操作能量消耗为25.5aj。为了更精确的估计,针对横向尺寸为10

×

10nm2的缩小的反转器执行微磁模拟。在这种小规模下,设备设计受到可纳米制造的特征尺寸的限制。因此,考虑直ip区域而不是v形区域,其中宽度为10nm。在式9中使用1.2

×

10

12

a/m2的模拟电流密度和118m/s的有效反转器dw速度,发现每次操作的能量消耗是18.4aj,这类似于上面的粗略估计。

[0152]

该按比例缩小的反转器的能量消耗可与在先进cmos设备中发现的≈30aj的切换能量相比。能量消耗的进一步改进可以通过优化材料和设备设计以降低所需的电流密度和增加dw速度来实现。

[0153]

上述估计仅涉及逻辑门中消耗的能量,即dw反转所消耗的能量。需要额外的能量来使逻辑输入的跑道中的dw成核,以检测逻辑输出并沿互连移动dw。因此,总能耗取决于逻辑电路的详细设计。

[0154]

下面更详细地描述其余附图:

[0155]

图5示意性地示出了oop-ip-oop结构中的电流驱动的dw反转的简单模型。图5a至图5c示出了dw跨越反转器传输的侧视图。跑道中的磁化方向和有效场h

dmi

、h

sot

和h

dip

的方向由不同区域中的箭头表示。与紧凑的高能量自旋结构相关的磁电荷如b中所示。

[0156]

图6示出了具有直ip区域的dw反转的微磁模拟。图6表示在微磁模拟中使用的设备几何形状。记录磁化的三个分量的位置用点指示。图6b至图6d示出了如图6a指示的在ip区域左侧(b)、在ip区域中间(c)和在ip区域右侧(d)的三个点处的磁化的时间演变。

[0157]

图7示出了在包含具有3

×

10

12

a/m2的电流密度的直的、30nm宽的ip区域的窄线中针对电流驱动的dw反转的dmi-oop各向异性相图(anisotropy phase diagram)。浅灰色圆和深灰色叉号表示针对模拟中的特定dmi和各向异性,dw被反转或未被反转。相图中的相关区域用深灰色和浅灰色阴影突出显示。此处,各向异性koop(ip区域)和koop(oop区域)分别表示ip区域和oop区域中的单轴oop各向异性。

[0158]

图8示出了用于操作可靠性测量的(a)nand门和(b)nor门的时间序列的moke图像。在左侧示出了不同反转器配置的对应示意图。使用施加的oop磁场将dw储存器和偏置分别设置为(a)用于nand操作的“0”和(b)用于nor操作的“1”。示意图中的浅灰色和深灰色分别对应于

⊙

和磁化。dw储存器处的v形反转器与由手性耦合产生的初始状态(指示为深灰色或浅灰色三角形)中的小反向畴相关联。nand/nor门的边界由虚线指示。捕获moke图像序列,其中在电流密度为7.5

×

10

11

a/m2并且脉冲长度为30ns的两个电流脉冲之后获取每个图像。在moke图像中,门结构中的亮和暗对比分别对应于

⊙

和磁化。所有比例尺均为1μm。

[0159]

图9示意性地示出了在缩小的磁dw逻辑设备中用于逻辑输入的电控制和逻辑输出的检测的mtj/跑道混合结构的建议。深灰色和浅灰色阴影区域分别表示具有oop和ip磁化的区域。位于逻辑输入和偏置的储存器上的三个mtj用于控制其磁化,而输出跑道上的一个mtj用于检测输出磁化。施加的电流的方向用箭头表示。

[0160]

图10示出了各种级联dw逻辑电路。图10a表示通过级联一个nand门和一个not门而制造的and门。图10b示出了具有nand门和nor门的级联dw逻辑电路。注意,在nor门的偏置储存器中放置反转器,使用绿色框突出显示,如插图所示给出为“1”的偏置,而nand门的偏置为“0”。图10c是通过级联三个nand门和一个not门而制造的两位多路复用器。图10d示出了通过级联四个nand门和一个not门而制造的半减器。图10e表示包括10个nand门和11个not门的长级联dw逻辑电路。mfm图像中的设备区域中的亮和暗对比分别对应于

⊙

和磁化。在使用oop磁场进行饱和以将初始磁化方向在所有储存器中设置为

⊙

并随后施加电流脉冲以获得最终状态之后捕获mfm图像。所有比例尺均为500nm。

[0161]

图11示意性地示出了磁dw逻辑元件的示例。不同的灰色阴影区域分别表示具有oop和ip各向异性的区域。电流的方向由黑色箭头指示。示出了实验中使用的磁dw逻辑元件的尺寸。

[0162]

图12描绘根据电流密度的、跑道的均匀oop区域中的dw速度和not门中的有效dw速度。误差条表示在5个不同设备中测量的dw速度的标准偏差。

[0163]

图13表示操作期间nand门的时间序列的moke图像及对应示意图。nand门在dw储存器中包含两个反转器并且偏置设置为“0”,并且nand门的边界由虚线表示。dw储存器中的两个v形反转器与由手性耦合产生的初始状态(指示为紫色三角形)中的小反向畴相关联。捕获moke图像序列,其中在电流密度为7.5

×

10

11

a/m2并且脉冲长度为30ns的两个电流脉冲之后获取每个图像。moke图像中的门结构中的亮和暗对比分别对应于

⊙

和磁化。通过施加1koe的oop磁场将两个dw储存器和偏置设置为逻辑“0”。所有比例尺均为1μm。

[0164]

图14示意性地示出了dw逻辑的传播延迟时间的概念。图14a示意性地表示使用传播延迟时间来提高nand门中的逻辑操作的操作可靠性。不同的灰色阴影分别对应于

⊙

和

磁化。图14b示出了具有不同输入跑道长度的nand门的mfm图像(顶部:1a=1b,中间:1a>1b,底部:1a<1b,其中1a和1b分别表示输入a和b的跑道长度)。亮和暗对比分别对应于

⊙

和磁化。在使用oop磁场进行饱和以将所有储存器中的初始磁化方向设置为

⊙

并随后施加电流脉冲以获得最终状态之后捕获mfm图像。指示了电流的方向。图14c示意性地示出了根据传播延迟时间给出正确输出的概率的相关性。mfm图像中的所有比例尺均为500nm。

[0165]

图15示出了nand门中的逻辑操作的霍尔测量。在图15a中,设备的光学图像中的不同灰色阴影分别表示具有电极、pt十字和nand门的区域。图15b示出根据脉冲数的霍尔电阻和对应moke图像。左侧:典型的霍尔电阻随脉冲数的增加而变化。右侧:1172次重复测量的前30次测量和最后30次测量。

⊙

和输出磁化的霍尔电阻水平由虚线指示。施加oop磁场以在用红色箭头指示的每次测量开始时设置初始状态。moke图像中的门结构中的亮和暗对比分别对应于

⊙

和磁化。nand门的边界由虚线指示。施加的电流脉冲的电流密度和脉冲长度分别为7.5

×

10

11

a/m2和30ns。图15c表示根据电流脉冲数的逻辑nand门的操作可靠性。所有比例尺均为2μm。

[0166]

图16示出了设备制造和磁性表征。图16a示出了磁dw逻辑电路的主要纳米制造工艺的示意图。(i)离子研磨磁性pt/co/al多层以产生磁条,(ii)离子研磨以产生磁跑道和逻辑门,以及(iii)氧化oop区域中的al层。在插图中,示出了在氧等离子体处理期间用于保护图3a所示的nand门的ip区域的50nm宽的pmma掩模的sem图像。sem图像中的比例尺为100nm。图16b表示在施加oop磁场时ip和oop区域的极性moke测量。最后,图16c表示在施加ip磁场时oop区域的反常霍尔测量。

[0167]

图17示出了具有直ip区域的dw反转器中的dw反转。图17a表示针对在具有直ip区域的dw反转器中执行的入射dw的dw反转的stxm图像序列。在施加两个电流脉冲之后捕获每个xmcd图像。磁跑道的边缘使用红色虚线指示,反转器的位置使用白色实线指示。xmcd图像中的亮和暗对比分别对应于

⊙

和磁化。脉冲的电流密度和持续时间为1.1

×

10

12

a/m2和1ns。图17b示出了针对四个不同操作的、具有直ip区域的相同dw反转器中反向磁畴成核的stxm图像。图17c示出了根据从实验moke测量确定的电流密度的具有v形和直ip区域的dw反转器中的dw速度。每个点的误差条和彩色阴影表示5次测量的dw速度的标准偏差。所有比例尺均为500nm。

[0168]

非对称dw反转器

[0169]

现在,参照图18示出,通过修改dw反转器的形状,可以在dw反转器操作中引入非互易性。图18示出了非对称dw反转器的这种非互易操作。图18(a)示意性地示出了针对正电流(左示意图)和负电流(右示意图)的非对称dw反转器的顶视图,其中示出了在沿“v”的不同位置处的反向畴的扇形角。由下式定义能量比:

[0170][0171]

其中n是围绕扇形畴的顶点的ip边界的数量,σ

dmi

是每单位长度的手性耦合能量,

σ

dw

是每单位长度的dw能量。指示了用于在沿ip区域的每个位置处使反向畴成核的能量比λ。图18b)表示在施加30个电流脉冲之前和之后非对称dw反转器的差异moke图像。moke图像中的亮和暗对比分别对应于

⊙

和磁化。电流脉冲的电流密度和持续时间分别为4.2

×

10

11

a/m2和50ns。图18c)是根据电流密度的、通过非对称和对称dw反转器传输的dw的速度。误差条表示在5个不同设备中测量的dw速度的标准偏差。

[0172]

如图18a所示,ip区域左侧的跑道的宽度被增加以抑制负电流的畴成核的可能性。在这种情况下,由于λ~1/(π/2+α)<2/π,在“v”与跑道的交点处的oop区域具有比沿着ip区域的其他位置更小的成核概率。因此,难以使ip区域左侧的反向畴成核。这一点已经通过使用负电流从反转器的右侧向左侧传播dw而在实验上得到证明(图18b)。当dw从右侧到达v形ip区域时,它们保持被钉扎并且不能通过反转器。相反,由于“v”的顶点内侧上的成核中心不受影响,所以从左侧入射的dw可以利用正电流朝向右侧传输。针对和dw两者都观察到这种行为(图18b)。因此,反向畴的成核针对正电流和负电流是高度不对称的,但与dw极性无关。此外,通过测量根据电流密度的dw位移,发现dw在向前方向上以与对称反转器类似的速度传播通过非对称反转器,而在向后传播方向上完全被阻碍(图18c)。

[0173]

微磁模拟

[0174]

为了进一步理解对称和非对称dw反转器中dw反转的机制,使用可公开获得的mumax3代码进行微磁模拟。该模拟包含使用以下磁参数的、具有2

×2×

1.6nm3离散化的、2048

×

1024

×

1个单元:饱和磁化强度ms=0.9ma/m,有效oop各向异性场h

eff

=200mt,交换常数a=16pj/m,有效自旋霍尔角pt θ

sh

=0.1,以及界面dmi常数d=-1.5mj/m2。对称dw反转器中的跑道宽度为800nm,而非对称dw反转器中的左右跑道的宽度分别为1500nm和800nm。ip区域的宽度为30nm并且a=20

°

。

[0175]

图19中示出了对称和非对称dw反转器两者中电流驱动的dw反转的微磁模拟。图19(a)示出了根据电流密度的、通过反转器传输的dw的速度。叉号表示在高电流密度下反转过程的“击穿”,这对应于和dw的连续注入。图18(b)表示在j=4

×

10

11

a/m2的状态(i),j=1.6

×

10

12

a/m2的状态(ii)和j=2.6

×

10

12

a/m2的状态(iii)中对称(顶部两行)和非对称反转器(底部两行)的磁配置的快照。磁化方向由色环指示。

[0176]

电流密度-速度曲线表现出不同dw行为的三种状态(图19a)。在低电流密度(j《1.0

×

10

12

a/m2)的状态i中,在对称和不对称dw反转器两者中,dw正好在ip区域之前被钉扎,而与电流方向无关(见图19b中的快照i)。钉扎归因于必须克服以切换围绕反转器区域的手性磁性结构的能量势垒。例如,如图19b所示,如果反转器的初始磁配置是如dmi所支持的,则反转器必须切换至其他dmi支持的配置以便将入射dw从左侧传输至右侧。

[0177]

在状态ii中,即在中等电流密度(1.0

×

10

12

《j《2.0

×

10

12

a/m2)下,sot足够强以推动dw穿过能量势垒并在ip区域的另一侧成核反向畴。在该状态下,通过反转器的dw的速度随电流密度线性增加。对称dw反转器中的反向畴针对正电流在“v”的顶点处成核,针对负电流在“v”与跑道边缘的交点处成核,这与第iv部分中表示的stxm测量值和自变量一致。在跨越对称dw反转器的反向传播dw的模拟中,我们发现成核过程在“v”与跑道边缘的上和下交

点处不同(见图19b中的快照ii),这是由于sot和dmi的组合效应引起的dw倾斜。

[0178]

此外,向前传播方向上的dw反转的阈值电流密度略低于向后传播方向的阈值电流密度,这意味着尽管具有相同的手性耦合强度,但“v”顶点处的成核比跑道边缘处的成核更有利。在非对称dw反转器的仿真中,向前传播方向上的行为与对称dw反转器的相同,并且它们的dw速度几乎一致。在向后传播方向上,在边缘处没有成核,并且dw在ip区域之前被完全阻挡。这种非互易行为与图18中报告的实验结果非常一致。

[0179]

最后,在高电流密度(j》2.0

×

10

12

a/m2)下的状态iii对应于在ip区域周围形成复杂的磁性结构(见图19b中的快照iii)并且对应于dw速度的饱和。在甚至更高的电流密度(j》2.6

×

10

12

a/m2)下,从“v”的顶点连续注入气泡形式的磁畴,导致dw变换器在向后传播方向上击穿(由图19a中的叉号指示)。

[0180]

dw二极管

[0181]

在电子电路中,二极管是对电子流进行整流的关键非互易元件,即,它允许电流沿一个方向(向前)通过而沿相反方向(向后)阻断电流。这种整流特性通常用于在模拟电路中将ac信号转换为dc信号。因此,在本发明的一个实施方式中,这种dw二极管基于上述非互易dw反转器。

[0182]

图18c和图19a中报告的针对非对称dw反转器的dw速度-电流密度曲线模拟二极管的i/v特性。然而,在向前方向上传播的dw相对于初始dw被反转。这种效应在电子电路中没有对应。因此,通过级联一个非对称dw反转器和一个对称dw反转器可以获得正确工作的dw二极管。

[0183]

图20大致示出了二极管的示意图。图20(a)是dw二极管的符号和示意图。图20(b)示出了在施加30个电流脉冲之前和之后dw二极管的差异moke图像。moke图像中的亮和暗对比分别对应于

⊙

和磁化。电流脉冲的电流密度和持续时间为4.2

×

10

11

a/m2和50ns。

[0184]

如图20a所示,由于手性耦合,两个级联的dw反转器的左侧和右侧的磁化在平衡状态下是相同的。在正电流的情况下,通过具有反转极性的非对称dw反转器传输的dw在对称反转器处反转回来,使得最终的dw在跑道中传播而不改变其极性。相反,在负电流的情况下,dw可以通过具有反转极性的对称dw反转器,但是它被非对称dw反转器阻断,如图20b所示。这种非互易操作等效于dw二极管。电流驱动的dw二极管是将dw逻辑电路的操作扩展至ac信号状态的新组件。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1