存储器装置的制作方法

1.本发明实施例涉及存储器装置,且特别涉及具有下拉电路的存储器装置。

背景技术:

2.一种常见类型的集成电路存储器是静态随机存取存储器(sram)装置。典型的sram存储器装置包括位元单元的阵列,而每一位元单元具有连接在上参考电位和下参考电位之间的六个晶体管。每一位元单元具有两个存储节点,用以存储信息。第一存储节点存储所需的信息,而互补信息是存储在第二存储节点。sram单元具有无需刷新即可保存数据的优点。

技术实现要素:

3.本发明实施例提供一种存储器装置。存储器装置包括一位元单元以及一下拉电路。位元单元包括一第一反相器以及一第二反相器。第一反相器连接于一第一节点与一第二节点之间。第二反相器连接于第一节点与第二节点之间。第一反相器和第二反相器在第一数据节点和第二数据节点之间交叉耦接。下拉电路连接到第二节点。下拉电路可操作以相应于一使能信号而将第二节点的电压下拉到低于接地电压。

4.再者,本发明实施例提供一种下拉电路。下拉电路包括一晶体管开关、一反相器与一负电压产生器电路。晶体管开关连接在存储器单元的接地电压节点和接地节点之间。反相器连接到晶体管开关。反相器的输入端可操作以接收一使能信号,而反相器的输出端连接到晶体管开关的栅极。负电压产生器电路的第一端连接到接地电压节点,而第二端耦接到晶体管开关的栅极。负电压产生器电路可操作以相应于使能信号而将接地电压节点的电压从接地电压驱动到负值。

5.再者,本发明实施例提供一种拉低存储器单元的一接地节点的电压的方法。在一下拉电路的一反相器接收一使能信号,其中下拉电路连接到一存储器单元的一接地节点。相应于所接收的使能信号,关闭下拉电路的晶体管开关,其中反相器的输出端是连接到晶体管开关,而当关闭时,晶体管开关将接地电压节点与接地端断开。在晶体管开关关闭之后,将接地电压节点的电压下拉至负值。在使能信号结束时,导通晶体管开关,以将接地电压节点连接到接地端。

附图说明

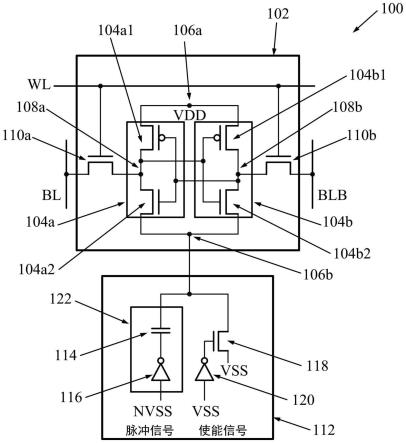

6.图1a是显示根据本公开一些实施例所述的示范例存储器装置。

7.图1b是显示根据本公开一些实施例所述的具有写入驱动器的示范例存储器装置。

8.图2a是显示根据本公开一些实施例所述的在读取操作期间的存储器装置的不同组件的电压。

9.图2b是显示根据本公开一些实施例所述的在写入操作期间的存储器装置的不同组件的电压。

10.图2c是显示根据本公开一些实施例所述的存储器装置的顺向电流。

11.图3是显示根据本公开一些实施例所述的示范例存储器装置。

12.图4是显示根据本公开一些实施例所述的示范例存储器装置。

13.图5a是显示根据本公开一些实施例所述的示范例下拉电路。

14.图5b是显示根据本公开一些实施例所述的示范例下拉电路。

15.图5c是显示根据本公开一些实施例所述的示范例下拉电路。

16.图5d是显示根据本公开一些实施例所述的示范例下拉电路。

17.图6是显示根据本公开一些实施例所述的示范例电荷泵。

18.图7是显示根据本公开一些实施例所述的示范例8t存储器装置。

19.图8是显示根据本公开一些实施例所述的示范例只读存储器装置。

20.图9是显示根据本公开一些实施例所述的操作存储器装置的方法。

21.附图标记说明:

22.100:存储器装置

23.102:存储器单元

24.102m,102m0-102mn:第二存储器单元

25.102n,1020n-102mn:第一存储器单元

26.104a:第一反相器

27.104a1:第一反相器第一晶体管

28.104a2:第一反相器第二晶体管

29.104b:第二反相器

30.104b1:第二反相器第一晶体管

31.104b2:第二反相器第二晶体管

32.106a:第一节点

33.106b:第二节点

34.108a:第一数据节点

35.108b:第二数据节点

36.110a:第三晶体管

37.110b:第四晶体管

38.112:下拉电路

39.114:下拉电路电容

40.116:下拉电路第一反相器

41.118:下拉电路晶体管

42.120:下拉电路第二反相器

43.122:负电压产生器电路

44.132a:写入驱动器第一晶体管

45.132b:写入驱动器第二晶体管

46.134:写入驱动器接地电压节点

47.202-208、212-220、250-254:曲线

48.300:存储器装置

49.302:选择器电路

50.400:存储器装置

51.502:金属氧化物半导体电容

52.504:耦合电容

53.506:nvss产生器

54.600:电荷泵电路

55.602:电荷泵第一反相器

56.604:电荷泵电容

57.606:电荷泵第二二极管

58.608:电荷泵第三二极管

59.610,610

1-610n:电荷泵二极管链

60.700:存储器装置

61.702:8t存储器单元

62.704:第一晶体管

63.706:第二晶体管

64.708:第三晶体管

65.710:第四晶体管

66.712:第五晶体管

67.714:第六晶体管

68.716:第七晶体管

69.718:第八晶体管

70.720a:第一节点

71.722a:第一数据节点

72.722b:第一数据节点

73.724:接地电压节点

74.802,802

1-802n:rom存储器单元

75.804,804

1-804n:接地电压节点

76.806:下拉线

77.900:方法

78.910-940:操作

79.bl:位元线

80.blb:反位元线

81.pd0-pdm:下拉线

82.rbl:读取位元线

83.vdd:电源

84.vss:接地端

85.wl:字元线

86.wrdata:写入数据信号

87.wrdatab:写入数据条信号

88.wwl:写入字元线

89.wbl:写入位元线

90.wblb:写入位元线条

具体实施方式

91.以下公开内容提供用于实作本发明实施例的不同特征的诸多不同的实施例或实例。以下阐述组件及排列的具体实例以简化本公开内容。当然,该些仅为实例且不旨在进行限制。举例而言,以下说明中将第一特征形成于第二特征“之上”或第二特征“上”可包括其中第一特征及第二特征被形成为直接接触的实施例,且亦可包括其中第一特征与第二特征之间可形成有附加特征、进而使得所述第一特征与所述第二特征可能不直接接触的实施例。另外,本发明实施例可能在各种实例中重复使用参考编号及/或字母。此种重复使用是出于简洁及清晰的目的,但自身并不表示所论述的各种实施例及/或配置之间的关系。

92.另外,为了易于描述图中所示的一个元件或特征与另一元件或特征的关系,本文中可使用例如“在...下”、“在...下方”、“下部”、“上覆”、及“上部”等空间相对用语。除了图中所示出的取向之外,所述空间相对用语亦旨在涵盖装置在使用或操作时的不同取向。设备可被另外取向(旋转90度或在其他取向),而本文所用的空间相对描述语可同样相应地作出解释。

93.本公开提供通过提供下拉电路来改善存储器装置(例如静态随机存取存储器(sram))操作的过程。下拉电路通过电容耦合将存储器装置的接地电压节点(也称为vss节点)的电压下拉至低于接地电压。

94.图1a是显示根据本公开一些实施例所述的存储器装置100。如图1a所显示,存储器装置100包括存储器单元102。存储器单元102是具有六个晶体管的sram装置(也称为6t sram)。存储器单元102包括第一反相器104a和第二反相器104b(统称为反相器104)。第一反相器104a的第一端连接到第一节点106a(也称为电源节点或vdd节点)。第一反相器104a的第二端连接到第二节点106b(也称为接地电压节点或vss节点)。

95.存储器单元102包括第一数据节点108a和第二数据节点108b。第一反相器104a和第二反相器104b在第一数据节点108a和第二数据节点108b之间相互交叉耦接。第一数据节点108a与第二数据节点108b互补。每一第一数据节点108a和第二数据节点108b都存储一位元的信息(即位元“0”或“1”)。

96.第一反相器104a包括第一反相器第一晶体管104a1和第一反相器第二晶体管104a2。第一反相器第一晶体管104a1的源极连接到第一节点106a,以及第一反相器第一晶体管104a1的漏极连接到第一数据节点108a。第一反相器第二晶体管104a2的漏极连接到第一数据节点108a,以及第一反相器第二晶体管104a2的源极连接到第二节点106b。第一反相器第一晶体管104a1和第一反相器第二晶体管104a2的每一栅极连接到第二数据节点108b,从而将第一反相器104a与第二反相器104b交叉耦接。在一些示范例中,第一反相器第一晶体管104a1也被称为第一上拉晶体管,而第一反相器第二晶体管104a2也被称为第一下拉晶体管。

97.在示范例中,第一反相器第一晶体管104a1是p型通道金属氧化物半导体(pmos)晶体管,而第一反相器第二晶体管104a2是n型通道金属氧化物半导体(nmos)晶体管。然而,本领域技术人员在阅读本公开内容后将清楚其他类型的晶体管,例如金属氧化物半导体场效

晶体管(mosfet)、nmos晶体管、pmos晶体管或是互补金属氧化物半导体(cmos)晶体管可以用于第一反相器第一晶体管104a1和第一反相器第二晶体管104a2中的每一个。此外,第一反相器第一晶体管104a1和第一反相器第二晶体管104a2是对称的。也就是说,每一个第一反相器第一晶体管104a1和第一反相器第二晶体管104a2的源极可以是漏极,而漏极可以是源极。

98.第二反相器104b包括第二反相器第一晶体管104b1和第二反相器第二晶体管104b2。第二反相器第一晶体管104b1的源极连接到第一节点106a,以及第二反相器第一晶体管104b1的漏极连接到第二数据节点108b。第二反相器第二晶体管104b2的漏极连接到第二数据节点108b,以及第二反相器第二晶体管104b2的源极连接到第二节点106b。第二反相器第一晶体管104b1和第二反相器第二晶体管104b2的栅极都连接到第一数据节点108a,从而将第二反相器104b与第一反相器104a交叉耦接。

99.在示范例中,第二反相器第一晶体管104b1是pmos晶体管,且第二反相器第二晶体管104b2是nmos晶体管。然而,本领域技术人员在阅读本公开内容后将清楚,其他类型的晶体管,例如mosfet、nmos晶体管、pmos晶体管或cmos晶体管可以用于每一个第二反相器第一晶体管104b1和第二反相器第二晶体管104b2。此外,第二反相器第一晶体管104b1和第二反相器第二晶体管104b2是对称的。也就是说,每一个第二反相器第一晶体管104b1和第二反相器第二晶体管104b2的源极可以是漏极,而漏极可以是源极。在一些示范例中,第二反相器第一晶体管104b1也被称为第二上拉晶体管,以及第二反相器第二晶体管104b2也被称为第二下拉晶体管。

100.存储器单元102还包括第三晶体管110a和第四晶体管110b。第三晶体管110a的源极连接到位元线bl,而第三晶体管110a的漏极连接到第一数据节点108a。第三晶体管110a的栅极连接到字元线wl。第四晶体管110b的源极连接到反位元线blb,而第四晶体管110b的漏极连接到第二数据节点108b。第四晶体管110b的闸汲连接到字元线wl。在一些示范例中,第三晶体管110a和第四晶体管110b也被称为导通闸(pg)晶体管。在示范例中,反位元线bbl与位元线bl为互补,也称为互补位元线。

101.在示范例中,每一个第三晶体管110a和第四晶体管104b2是nmos晶体管。然而,本领域技术人员在阅读本公开内容后将清楚,其他类型的晶体管,例如mosfet、pmos晶体管或cmos晶体管可以用于每一个第三晶体管110a和第四晶体管110b。此外,每一个第三晶体管110a和第四晶体管110b都是对称的。也就是说,每一个第三晶体管110a和第四晶体管110b的源极可以是漏极,而漏极可以是源极。

102.在存储器单元102上的读取或写入操作期间,字元线wl会相应于读取使能信号或是写入使能信号而被充电至高逻辑电平。字元线wl充电到高逻辑电平会导致第一数据节点108a连接到位元线bl,而第二数据节点108b连接到反位元线blb。

103.继续参考图1a,存储器装置100还包括下拉电路112。下拉电路112连接到存储器单元102的第二节点106b(或接地电压节点),并且用于在读取操作和写入操作期间将第二节点106b的电压下拉至负值。

104.如图1a所显示,下拉电路112包括下拉电路电容114、下拉电路第一反相器116、下拉电路晶体管118和下拉电路第二反相器120。下拉电路电容114的第一端连接到存储器单元102的第二节点106b(即接地电压节点或vss节点)。电容114的第二端连接到下拉电路第

一反相器116的输出端。下拉电路第一反相器116在其输入端接收负vss(nvss)脉冲信号。nvss脉冲信号的电压电平大约等于电源vdd。在示范例实施例中,下拉电路电容114和下拉电路第一反相器116一起也被称为负电压产生器电路122。

105.下拉电路晶体管118的源极连接到第二节点106b(即接地电压节点),并且下拉电路晶体管118的漏极连接到接地端vss。下拉电路晶体管118的栅极连接到下拉电路第二反相器120的输出端。下拉电路第二反相器120的输入端可操作以接收使能信号或vss使能信号。

106.在示范例中,下拉电路晶体管118是nmos晶体管。然而,本领域技术人员在阅读本公开内容后将明白,其他类型的晶体管,例如mosfet、pmos晶体管或cmos晶体管可用于下拉电路晶体管118。另外,下拉电路晶体管118是对称的。也就是说,下拉电路晶体管118的源极可以是漏极,而漏极可以是源极。

107.图1b是显示根据本公开一些实施例所述的具有写入驱动器的存储器装置100的另一示范图。如图1b所显示,存储器装置100包括存储器单元102和下拉电路112。下拉电路112连接到存储器单元102的第二节点106b(即接地电压节点)。存储器装置100还包括写入驱动器第一晶体管132a和写入驱动器第二晶体管132b。写入驱动器第一晶体管132a和写入驱动器第二晶体管132b一起也被称为写入驱动器。下拉电路112连接到写入驱动器接地电压节点134。因为下拉晶体管112连接到写入驱动器接地电压节点134,所以在写入操作期间,写入驱动器接地电压节点134和第二节点106b的电压电平被拉低至负值,从而提高存储器装置100的写入效率。

108.写入驱动器第一晶体管132a的源极连接到位元线bl,且写入驱动器第一晶体管132a的漏极连接到写入驱动器接地电压节点134。写入驱动器第一晶体管132a的栅极连接到写入数据条(data bar)信号wrdatab。写入驱动器第二晶体管132b的源极连接到反位元线blb,而写入驱动器第二晶体管132b的漏极连接到写入驱动器接地电压节点134。写入驱动器第二晶体管132b的栅极连接到写入数据信号wrdata。

109.在示范例中,写入驱动器第一晶体管132a和写入驱动器第二晶体管132b是nmos晶体管。然而,本领域技术人员在阅读本公开内容后将清楚,其他类型的晶体管,例如mosfet、pmos晶体管或cmos晶体管可以用于每一个写入驱动器第一晶体管132a和写入驱动器第二晶体管132b。此外,写入驱动器第一晶体管132a和写入驱动器第二晶体管132b都是对称的。也就是说,每一个写入驱动器第一晶体管132a和写入驱动器第二晶体管132b的源极可以是漏极,而漏极可以是源极。

110.在示范例实施例中,相应于存储器装置100的读取操作或写入操作而产生使能信号。图2a是显示在读取操作期间存储器装置100的不同组件的示范例电压分布。例如,图2a的第一曲线202是显示字元线wl的示范例电压分布。图2a的第二曲线204是显示nvss脉冲信号的示范例电压分布。图2a的第三曲线206是显示第二节点106b(即接地电压节点或vss节点)的示范例电压分布。图2a的第四曲线208是显示使能信号的示范例电压分布。

111.如图2a的第一曲线202所显示,字元线wl被充电至高逻辑电平。在示范例实施例中,字元线wl被充电至高逻辑电平(即被断言(asserted))以启动对存储器单元102的读取操作。字元线wl在时间t1被充电至高逻辑电平。在示范例实施例中,对应于高逻辑电平的电压大约等于存储器单元102的供应电压vdd,而对应于低逻辑电平的电压大约等于接地电压

或零伏特。

112.此外,如第二曲线204所显示,nvss脉冲信号被充电至高逻辑电平。如图2a所显示,在字元线wl被充电至高逻辑电平之前,nvss脉冲信号稍稍被充电至高逻辑电平(即在时间t0)。在示范例实施例中,nvss脉冲信号与字元线wl同时充电或稍早于字元线wl被充电至高逻辑电平。nvss脉冲信号充电到高逻辑电平会导致下拉电路第一反相器116的输出被充电到低逻辑电平并且耦合下拉电路电容114到存储器装置102的接地电压节点。

113.再者,如第四曲线208所显示,使能信号被充电至高逻辑电平以用于存储器单元102的读取或写入操作。使能信号在稍早之前(即在时间t0)或同时将字元线wl充电至高逻辑电平。

114.在示范例实施例中,当使能信号被充电到高逻辑电平时,下拉电路第二反相器120的输出处于低逻辑电平并且通过扩展下拉电路晶体管118的栅极处于低逻辑电平。这导致下拉电路晶体管118被关闭,从而将存储器单元102的接地电压节点与接地端断开。

115.此外,如图2a的第三曲线206所显示,由于下拉电路电容114耦合到接地电压节点,存储器单元102的接地电压节点的电压被拉至低逻辑电平。然而,随着接地电压节点汲取存储器单元102的读取电流,存储器单元102的接地电压节点的电压可能会继续逐渐被拉回。

116.如第一曲线202所显示,字元线wl在从其断言开始的预定持续时间之后被解除断言。在示范例实施例中,预定持续时间小于接地电压节点的电压达到零伏特的时间。在字元线wl被解除断言之后,字元线wl上的电压开始下降并且在时间t2达到第三晶体管110a或第四晶体管110b的临界电压vt电平。在时间t2,当字元线wl下降到低于第三晶体管110a或第四晶体管110b的临界电压vt电平时,第三晶体管110a或第四晶体管110b停止汲取单元电流。此外,第三晶体管110a或第四晶体管110b比字元线wl被取消断言之前汲取更多的电流i

ds

。如第三曲线206所显示,接地电压节点在时间t2的电压是低于零伏特的δvss(即负δvss)。由于在读取操作期间,在第一节点106a(即电源节点)和第二节点106b(即接地电压节点)之间较大的电压差(即(vdd+δvss-vdd)与(vdd-vss)相比),δvss提高存储器装置100的稳定性。

117.在示范例实施例中,正向偏压电流会随着接地电压节点的电压被拉低到零伏特以下而增加。图2c是显示比较存储器单元102的正向偏压电流的曲线250。例如,图2c的第一曲线252是显示具有连接到存储器单元102的接地电压节点的下拉电路112的存储器单元102的正向偏压电流。第二曲线254是显示没有连接到存储器单元102的接地电压节点的下拉电路112的正向偏压电流。如曲线250所显示,当下拉电路112连接到接地电压节点时,存储器单元102的正向偏压电流会更高。正向偏压电流的差值大约等于δvss。

118.参考回图2a,如第四曲线208所显示,在读取或写入操作结束之后,在时间t3重新断言使能信号(即充电至低逻辑电平)。重新断言使能信号会导致下拉电路第二反相器120的输出上升到高逻辑电平,这导致下拉电路晶体管118会导通。下拉电路晶体管118的导通会导致存储器单元102的接地电压节点要接地。此外,如第二曲线204所显示,nvss脉冲信号在读取或写入操作结束后被缓慢地解除断言。

119.图2b是显示在写入操作期间存储器装置100的不同组件的示范例电压分布。例如,图2b的第一曲线212是显示字元线wl的示范例电压分布。图2b的第二曲线214是显示位元线bl或反位元线blb的示范例电压分布。图2b的第三曲线216图是显示nvss脉冲信号的示范例

电压分布。图2b的第四曲线218是显示第二节点106b(即接地电压节点)的示范例电压分布。图2b的第五曲线220是显示使能信号的示范例电压分布。

120.如图2b的第一曲线212所显示,字元线wl被充电至高逻辑电平,以用于存储器单元102的写入操作。字元线wl在时间t1被充电至高逻辑电平。再者,如第二曲线214所显示,位元线bl或反位元线blb在时间t1被充电至低逻辑电平。此外,如第三曲线216所显示,nvss脉冲信号被充电至高逻辑电平。nvss脉冲信号在字元线wl被充电到高逻辑电平之前稍稍被充电到高逻辑电平(即在时间t0)。在示范例实施例中,nvss脉冲信号与字元线wl同时充电或稍早于字元线wl被充电至高逻辑电平。nvss脉冲信号充电到高逻辑电平会导致下拉电路第一反相器116的输出被充电到低逻辑电平,并且将下拉电路电容114耦合到存储器装置102的接地电压节点和写入驱动器的写入驱动器接地电压节点134。

121.如第五曲线220所显示,使能信号被充电到高逻辑电平,以用于存储器单元102上的写入操作。使能信号在稍早之前(即在时间t0)被充电到高逻辑电平,或同时地与字元线wl被充电到高逻辑电平。

122.在示范例实施例中,当使能信号被充电到高逻辑电平时,下拉电路第二反相器120的输出为低逻辑电平并且通过扩展下拉电路晶体管118的栅极于低逻辑电平。这导致下拉电路晶体管118被关闭,从而将存储器单元102的接地电压节点与接地端断开。

123.此外,如图2b的第四曲线218所显示,由于耦接下拉电路电容114至接地电压节点,存储器单元102的接地电压节点和写入驱动器接地电压节点134的电压会被拉至低逻辑电平。然而,随着接地电压节点汲取存储器单元102的读取电流,存储器单元102的接地电压节点的电压可能会继续逐渐被拉回。

124.如第一曲线212所显示,字元线wl在从其断言开始的预定持续时间之后被解除断言。在一些示范例中,预定持续时间小于接地电压节点的电压达到零伏特的时间。在字元线wl被解除断言之后,字元线wl上的电压开始下降并且在时间t2达到第三晶体管110a或第四晶体管110b的临界电压vt电平。如第四曲线218所显示,接地电压节点在时间t2的电压是低于零伏特的δvss(即负δvss)。在读取操作期间,由于第一节点106a(即电源节点)与接地电压节点之间较大的电压差(即(vdd+δvss-vdd)与(vdd-vss)相比),电压δvss会改善存储器装置100的稳定性。

125.在示范例实施例中,下拉电路112可以由多个存储器单元共享。图3是显示存储器装置300,其中下拉电路112是由多个存储器单元所共享。图3的存储器装置300包括排列成具有多列(row)(例如m列)和多行(column)(例如n行)的矩阵的多个存储器单元。多行中的每一行包括多个第一存储器单元,而多列中的每一列包括多个第二存储器单元。

126.此外,存储器装置300包括多条字元线、多条位元线和多条互补位元线(也称为位元线条)。多行中的一行的每一个第一存储器单元是连接到多个位元线中的一位元线和多个位元线条中的一位元线条。再者,多列中的一列的每一个第二存储器单元是连接到多个字元线中的一字元线。

127.例如,存储器装置300的第m列的每一第二存储器单元(即存储器单元102m0、

…

、存储器单元102mn,统称为第m列的第二存储器单元102m)是连接到第m个字元线(表示为字元线wlm)。相似地,每一个第m列的第二存储器单元102m的第二节点106b是连接到第m个下拉线(表示为pdm)。

128.接着,存储器装置300的第一列的第二存储器单元是连接到第一个字元线,以及第一列的每一个第二存储器单元的第二节点106b是连接到第一个下拉线(表示为pd1)。此外,存储器装置300的第0列的第二存储器单元是连接到第0个字元线,并且第0列的每一个第二存储器单元的第二节点106b是连接到第0个下拉线(表示为pd0)。

129.在示范例实施例中,每一下拉线是平行于与所对应的第二存储器单元相关联的字元线并且与字元线相关联。例如,下拉线pd0与字元线wl0平行。在示范例实施例中,下拉线形成在与字元线相同或不同的金属层中。例如,下拉线pd0和字元线wl0都形成在金属层3中。在另一个例子中,下拉线pd0形成在金属层1中,而字元线wl0形成在金属层3中。在示范例实施例中,下拉线在多个连续列之间共享。例如,每两连续列、四连续列、八连续列等共享下拉线。

130.图3的存储器装置300还包括选择器电路302。选择器电路302用于将下拉电路112连接到下拉线,而该下拉线与为读取或写入操作而充电的字元线平行并相关联。例如,当字元线wlm被选择用于对第m列的第二存储器单元102m的一者的读取或写入操作时,选择器电路302将下拉电路112连接到下拉线pdm。

131.在示范例实施例中,选择器电路302包括多个选择器晶体管开关。每一个选择器晶体管开关都与下拉线相关联,并且在导通时,将下拉电路112连接到下拉线。每一个选择器晶体管开关的源极是连接到下拉电路112,并且每一个选择器晶体管开关的漏极是连接到下拉线。每一个选择器晶体管开关的栅极是连接到控制电路,以导通和关闭。

132.在示范例实施例中,如图3所显示,选择器电路302的多个晶体管开关是nmos晶体管。然而,本领域技术人员在阅读本公开内容后将清楚,其他类型的晶体管,例如mosfet、pmos晶体管或cmos晶体管,可以用于选择器电路302的晶体管开关。另外,选择器电路302的每一个晶体管开关是对称的。也就是说,选择器电路302的每一个晶体管开关的源极可以是漏极,而漏极可以是源极。

133.虽然在图3中是显示下拉线是平行于字元线,但是对于本领域技术人员来说显而易见的是,下拉线可以平行于存储器装置的位元线。图4是显示具有平行于位元线的下拉线的存储器装置400。

134.例如,如图4所显示,存储器装置400的第n行的每一第一存储器单元(即存储器单元102on、...、存储器单元102mn,统称为第n行的第一存储器单元)的第二节点106b是连接到第n个下拉线(pdn)。继续,存储器装置400的第一行的每一第一存储器单元的第二节点106b是连接到第一下拉线(表示为pd1)。此外,存储器装置400的第0列的每一第一存储器单元的第二节点106b是连接到第0下拉线(表示为pd0)。在示范例实施例中,下拉线在多个连续行之间共享。例如,每连续两行、连续四行、连续八行等共用一个下拉线。

135.选择器电路302用于将下拉电路112连接到下拉线,而该下拉线平行于并与充电为读取或写入操作的位元线相关联。在示范例实施例中,下拉线pdn平行于第n位元线或第n互补位元线。下拉线pdn可以形成在与第n位元线或第n互补位元线相同的金属层或不同的金属层中。例如,下拉线pdm形成在金属层0或金属层2中。在示范例实施例中,下拉线在多个连续位元线之间共享。例如,每两条连续位元线、四条连续位元线、八条连续位元线等共用一条下拉线。

136.图5a是显示第一示范例下拉电路112。图5a的下拉电路112包括金属氧化物半导体

电容(moscap)502、下拉电路第一反相器116、下拉电路晶体管118和下拉电路第二反相器120。moscap 502的第一端连接到存储器单元102的第二节点106b。moscap 502的第二端连接到下拉电路第一反相器116的输出。下拉电路第一反相器116可操作以在其输入端接收nvss脉冲信号。下拉电路晶体管118的源极是连接到第二节点106b,并且下拉电路晶体管118的漏极是连接到接地端vss。下拉电路晶体管118的栅极是连接到下拉电路第二反相器120的输出端。下拉电路第二反相器120的输入端可操作以接收使能信号或vss使能信号。

137.在示范例实施例中,moscap 502包括金属氧化物半导体晶体管,其漏极与形成第一端的源极和形成第二端的栅极排序。moscap的mos晶体管可以是nmos晶体管、mosfet、pmos晶体管或cmos晶体管。

138.图5a的下拉电路112用于在读取/写入操作期间通过moscap 502的放电而将存储器装置100的存储器单元102的接地电压节点的电压下拉至负值。例如,在读取/写入操作期间,nvss信号和vss信号都被充电到高逻辑电平。这导致接地电压节点从接地端vss断开并且通过moscap 502将接地电压的电压电平拉低至负值。

139.图5b是显示第二示范例下拉电路112。图5b的下拉电路112包括耦合电容504、下拉电路第一反相器116、下拉电路晶体管118和下拉电路第二反相器120。耦合电容504的一端是连接到存储器单元102的第二节点106b。耦合电容504的第二端是连接到下拉电路第一反相器116的输出端。下拉电路第一反相器116是操作以在其输入端接收nvss脉冲信号。下拉电路晶体管118的源极是连接到第二节点106b,并且下拉电路晶体管118的漏极是连接到接地端vss。下拉电路晶体管118的栅极是连接到下拉电路第二反相器120的输出端。下拉电路第二反相器120的输入端可操作以接收使能信号或vss使能信号。

140.在示范例实施例中,耦合电容504包括彼此平行设置的多条金属线或金属板,从而形成耦合电容504。在一些示范例中,耦合电容504的金属线或金属板形成为相同的金属层或不同的金属层。例如,第一部分的金属线或金属板形成在第一金属层中,而第二部分的金属线或金属板形成在不同于第一金属层的第二金属层中。在一些其他示范例中,金属线或金属板可以形成在多于两个金属层中。

141.图5b的下拉电路112用于在读取/写入操作期间通过耦合电容504的放电而将存储器装置100的存储器单元102的接地电压节点的电压下拉至负值。例如,在读取/写入操作期间,nvss信号和vss信号都被充电到高逻辑电平。这导致接地电压节点从接地端vss被断开并且通过耦合电容504将接地电压的电压电平拉低至负值。

142.图5c是显示第三示范例下拉电路112。图5c的下拉电路112包括电容114、下拉电路晶体管118和下拉电路第二反相器120。电容114的第一端是连接到存储器单元102的第二节点106b。电容114的第二端是连接到下拉电路第二反相器120的输出端。下拉电路晶体管118的源极是连接到第二节点106b,以及下拉电路晶体管118的漏极是连接到接地端vss。下拉电路晶体管118的栅极连接到下拉电路第二反相器120的输出端。下拉电路第二反相器120的输入端可操作以接收使能信号或vss使能信号。电容114可以是n-moscap、p-moscap、n-moscap和p-moscap两者,或者是具有多个彼此平行放置的金属线或金属板的耦合电容。

143.图5c的下拉电路112用于在读取/写入操作期间通过电容114的放电而将存储器装置100的存储器单元102的接地电压节点的电压下拉至负值。例如,在读取/写入操作期间,nvss信号和vss信号都被充电到高逻辑电平。这导致接地电压节点从接地端vss被断开并且

通过电容114将接地电压的电压电平拉低至负值。

144.图5d是显示第四示范例下拉电路112。图5d的下拉电路112包括nvss产生器506、下拉电路晶体管118和下拉电路第二反相器120。nvss产生器506的第一端是连接到存储器单元102的第二节点106b。nvss产生器506的第二端是用于接收nvss脉冲信号。下拉电路晶体管118的源极是连接到第二节点106b,以及下拉电路晶体管118的漏极是连接到接地端vss。下拉电路晶体管118的栅极是连接到下拉电路第二反相器120的输出端。下拉电路第二反相器120的输入端可操作以接收使能信号或vss使能信号。

145.图5d的下拉电路112用于在读取/写入操作期间通过nvss产生器506的放电将存储器装置100的存储器单元102的接地电压节点的电压下拉至负值。例如,在读取/写入操作期间,nvss信号和vss信号都被充电到高逻辑电平。这导致接地电压节点从接地端vss被断开并且通过nvss产生器506将接地电压的电压电平拉低到负值。

146.在示范例实施例中,nvss产生器506是电荷泵(charge pump)。当被激活时,电荷泵可操作以将负电荷泵送(pump)到接地电压节点,从而拉低接地电压节点的电压。图6是显示根据一些实施例所述的示范例电荷泵电路600。

147.电荷泵电路600包括电荷泵第一反相器602、电荷泵电容604、电荷泵第二二极管606、电荷泵第三二极管608和电荷泵二极管链610。电荷泵二极管链610包括多个二极管,例如,电荷泵二极管链第一二极管6101、电荷泵二极管链第二二极管6102、

……

、和电荷泵二极管链第n二极管610n连接在一起形成链。电荷泵二极管链610通过连接形成一个成员的二极管的第二端与另一个成员的二极管的第一端。例如,电荷泵二极管链第一二极管6101的第二端连接到电荷泵二极管链第一二极管6102的第一端。第一成员二极管的第一端形成电荷泵二极管链610的第一端,以及最后一个成员二极管的第二端形成电荷泵二极管链610的第二端。电荷泵二极管链610的成员二极管的数量是可配置的并且可以取决于由电荷泵600所泵送的电荷量。

148.电荷泵第一反相器602可操作以在其输入端接收nvss脉冲信号。电荷泵第一反相器602的输出端连接到电荷泵电容604的第一端。电荷泵电容604的第二端连接到电荷泵第二二极管606的第一端。电荷泵第二二极管606的第二端是连接到接地端。电荷泵第二二极管606的第一端连接到电荷泵第三二极管608的第一端。电荷泵第三二极管608的第二端是连接到接地电压节点。电荷泵二极管链610的第一端连接到接地电压节点,以及电荷泵二极管链610的第二端连接到接地端。

149.在操作期间,当nvss脉冲信号上升到高逻辑电平(即当nvss脉冲信号被注入时)进入电荷泵第一反相器602、电荷泵电容604、电荷泵第二二极管606、电荷泵第三二极管608和电荷泵二极管链610时,将接地电压节点的电压下拉至负值。

150.在示范例实施例中,下拉电路112可以连接到八晶体管(8t)sram。图7是显示具有8t存储器单元的存储器装置700。如图7所显示,存储器装置700包括8t存储器单元702和连接到存储器单元702的接地电压节点的下拉电路112。

151.8t存储器单元包括八个晶体管,即第一晶体管704、第二晶体管706、第三晶体管708、第四晶体管710、第五晶体管712、第六晶体管714、第七晶体管716和第八晶体管718。第一晶体管704的源极连接到第一节点720a,而第一晶体管704的漏极连接到第一数据节点722a。第二晶体管706的漏极连接到第一数据节点722a,以及第二晶体管706的源极连接到

第二节点720b。第一晶体管704的栅极连接到第二晶体管706的栅极。第一节点720a也称为vdd节点或电源节点,而第二节点720b也称为vss节点或接地电压节点。第一晶体管704和第二晶体管706形成第一反相器。第一数据节点722a用于存储一位元的信息(即位元值“0”或“1”)。

152.第三晶体管708的源极连接到第一节点720a,以及第三晶体管708的漏极连接到第二数据节点722b。第四晶体管710的漏极连接到第二数据节点722b,而第四晶体管710的源极连接到第二节点720b。第三晶体管708的栅极连接到第四晶体管710的栅极。第三晶体管708和第四晶体管710形成第二反相器。第二反相器在第一数据节点722a和第二数据节点722b与第一反相器交叉耦接。

153.第五晶体管712的源极连接到写入位元线wbl,而第五晶体管712的漏极连接到第一数据节点722a。第五晶体管712的栅极连接到写入字元线wwl。第六晶体管714的源极连接到写入位元线条wblb,以及第六晶体管714的漏极连接到第二数据节点722b。第六晶体管714的栅极连接到写入字元线wwl。

154.第七晶体管716的漏极连接到读取位元线rbl,且第七晶体管716的源极连接到第八晶体管718的漏极。第七晶体管716的栅极连接到读取字元线rwl。第八晶体管718的栅极连接到第二数据节点722b。第八晶体管718的源极连接到接地电压节点724。下拉电路112也连接到接地电压节点724。在存储器单元702的读取操作期间,下拉电路112用于将接地电压节点的电压724拉为负电压。

155.在示范例实施例中,第一晶体管704、第二晶体管706、第三晶体管708、第四晶体管710、第五晶体管712、第六晶体管714、第七晶体管716和第八晶体管718中的每一个晶体管都是对称的。此外,第一晶体管704、第二晶体管706、第三晶体管708、第四晶体管710、第五晶体管712、第六晶体管714、第七晶体管716和第八晶体管718中的每一个晶体管可以包括nmos晶体管、pmos晶体管、cmos晶体管或mosfet晶体管。

156.存储器单元702也被称为双端口(dual port)存储器单元或多端口存储器单元,因为它包括读取端口和写入端口。在示范例实施例中,另一个下拉电路112可以连接到第二节点720b,而该第二节点720b可以在存储器单元702的写入操作期间将第二节点720b的电压下拉至负电压。在一些其他示范例中,下拉电路112可以连接到第二节点720b和接地电压节点724两者,并且可以在写入操作期间将第二节点720的电压下拉至负电压并且在读取操作期间将接地电压节点724的电压下拉至负电压。在示范例中,虽然图7是显示双端口存储器单元,但是本文公开的技术可以应用于多读取/写入端口存储器单元。在这样的示范例中,读取端口可以连接到第一数据节点722a或第二数据节点722b,以及写入端口可以通过连接到第一数据节点722a和第二数据节点722b并分别连接到写入位元线wbl[i]/写入位元线条wblb[i]的一对nmos元件来添加,其中i是整数。

[0157]

在示范例实施例中,下拉电路112可以连接到只读存储器(rom)和相联存储器(cam)。图8是显示具有多个rom存储器单元802的rom存储器装置800,即第一rom存储器单元8021、

…

、第n个rom存储器单元802n。每一rom存储器单元802的栅极连接到字元线wl。每一rom存储器单元802的源极连接到对应的位元线。例如,如图8所示,第一rom存储器单元8021的源极连接到第一位元线(即bl[0]),继续到第n个rom存储器单元802n,其中源极连接到第n位元线(即bl[n])。每一rom存储器单元802的漏极连接到对应的接地电压节点。例如,如图

8所显示,第一rom存储器单元8021的漏极连接到第一接地电压节点8041,继续到第n个rom存储器单元802n,对于该第n个rom存储器单元,漏极连接到第n个接地电压节点804n。此外,每一个接地电压节点(即第一接地电压节点8041、

……

、第n接地电压节点804n)都连接到下拉电路112。在示范例实施例中,rom存储器装置800的多个接地电压节点是经由下拉线806连接到下拉电路112。下拉线806平行于字元线wl。下拉线806形成在与字元线wl相同的金属层中或不同的金属层中。

[0158]

图9是显示根据一些实施例所述的用于操作存储器装置的方法900的流程图。例如,图9是说明用于操作存储器装置100、存储器装置300、存储器装置400、存储器装置700和存储器装置800中的任何一个存储器装置的方法900的流程图,如上面参考图1-8所描述。方法900可以由处理器所执行。再者,方法900可以存储为存储器装置上的指令,以及当由处理器执行时,可以使处理器执行方法900。

[0159]

在方法900的操作910,接收使能信号。使能信号是指示存储器装置100、存储器装置300、存储器装置400、存储器装置700或存储器装置800中的读取操作或写入操作。使能信号在下拉电路112的下拉电路第二反相器120被接收,其连接到存储器单元102的接地电压节点(即第二节点106b)。

[0160]

在方法900的操作920,相应于所接收的使能信号,下拉电路的晶体管开关被关闭。例如,下拉电路晶体管118会相应于下拉电路第二反相器120所接收到的使能信号而被关闭。下拉电路第二反相器120的输出端连接到下拉电路晶体管118的栅极。因此,当下拉电路第二反相器120的输出端处于低逻辑电平时,下拉电路晶体管118被关闭。当关闭时,下拉电路晶体管118将存储器单元102的接地电压节点(即第二节点106b)与接地端vss断开。

[0161]

在方法900的操作930,开始下拉接地电压节点的电压。例如,负电压产生器电路将第二节点106b的电压下拉至负值。在示范例实施例中,负电压产生器电路将第二节点106b的电压下拉至负vdd。

[0162]

在方法900的操作940,晶体管开关在使能信号结束时被导通,以便将接地电压节点连接到接地端vss。例如,下拉电路晶体管118相应于下拉电路第二反相器120的使能信号的结束而导通。下拉电路晶体管118的导通会导致将接地电压节点(即第二节点106b)连接到接地端vss。

[0163]

本公开提供一种存储器装置。存储器装置包括一位元单元以及一下拉电路。位元单元包括一第一反相器以及一第二反相器。第一反相器连接于一第一节点与一第二节点之间。第二反相器连接于第一节点与第二节点之间。第一反相器和第二反相器在第一数据节点和第二数据节点之间交叉耦接。下拉电路连接到第二节点。下拉电路可操作以相应于一使能信号而将第二节点的电压下拉到低于接地电压。

[0164]

在一些实施例中,下拉电路包括一晶体管开关与一电容。晶体管开关连接在第二节点和一接地节点之间。电容连接到第二节点。电容可操作以相应于使能信号而将第二节点的电压下拉至低于接地电压。

[0165]

在一些实施例中,存储器装置还包括下拉反相器。下拉反相器操作以对应于一读取使能信号而接收使能信号。下拉反相器的输出端是耦接到晶体管开关的栅极。

[0166]

在一些实施例中,电容包括金属氧化物半导体(mos)电容。

[0167]

在一些实施例中,电容包括多个彼此大体上平行的金属板。

[0168]

在一些实施例中,使能信号在字元线激活信号之前被激活,而字元线激活信号是指示存储器装置的读取操作。

[0169]

在一些实施例中,晶体管开关在字元线激活信号之后被关闭,以隔离下拉电路。

[0170]

在一些实施例中,使能信号在字元线激活信号之前被激活,而字元线激活信号是指示存储器装置的写入操作。

[0171]

在一些实施例中,下拉电路包括一晶体管开关与一负电压产生器电路。晶体管开关连接在第二节点和一接地节点之间。负电压产生器电路连接到第二节点。负电压产生器电路用于相应于使能信号而将第二节点的电压拉低到低于接地电压。

[0172]

本公开提供一种下拉电路。下拉电路包括一晶体管开关、一反相器与一负电压产生器电路。晶体管开关连接在存储器单元的接地电压节点和接地节点之间。反相器连接到晶体管开关。反相器的输入端可操作以接收一使能信号,而反相器的输出端连接到晶体管开关的栅极。负电压产生器电路的第一端连接到接地电压节点,而第二端耦接到晶体管开关的栅极。负电压产生器电路可操作以相应于使能信号而将接地电压节点的电压从接地电压驱动到负值。

[0173]

在一些实施例中,存储器单元包括一个6t(6个晶体管)静态随机存取存储器(sram)。

[0174]

在一些实施例中,存储器单元包括一个8t静态随机存取存储器(sram)。

[0175]

在一些实施例中,存储器单元包括只读存储器(rom)。

[0176]

在一些实施例中,存储器单元包括相联存储器(cam)。

[0177]

在一些实施例中,存储器单元包括多端口静态随机存取存储器(sram)。

[0178]

在一些实施例中,负电压产生器电路包括一电容。

[0179]

本公开提供一种拉低存储器单元的一接地节点的电压的方法。在一下拉电路的一反相器接收一使能信号,其中下拉电路连接到一存储器单元的一接地节点。相应于所接收的使能信号,关闭下拉电路的晶体管开关,其中反相器的输出端是连接到晶体管开关,而当关闭时,晶体管开关将接地电压节点与接地端断开。在晶体管开关关闭之后,将接地电压节点的电压下拉至负值。在使能信号结束时,导通晶体管开关,以将接地电压节点连接到接地端。

[0180]

在一些实施例中,接收使能信号包括相应于存储器单元的读取操作而接收使能信号。

[0181]

在一些实施例中,接收使能信号包括相应于存储器单元的写入操作而接收使能信号。

[0182]

在一些实施例中,拉低接地电压节点的电压包括启动连接到接地电压节点的电容的充电。电容的充电会拉低接地电压节点的电压。

[0183]

对于本领域的技术人员来说,本公开中所描述的实施方案的各种修改将是显而易见的,并且在不脱离本公开的范围的情况下,本文中所定义的一般原理可适用于其它实施方案。因此,本公开并不既定限于本文中所示出的实施方案,而应被赋予与本文所公开的新颖特征和原理相一致的最广泛范围,如权利要求中所述。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1