输入信号处理方法及存储器电路结构与流程

1.本发明属于半导体集成电路技术领域,尤其涉及输入信号处理方法及相应的存储器电路结构。

背景技术:

2.dram(dynamic random access memory),即动态随机存取存储器,是最为常见的系统内存。dram中输入信号对译码结果非常重要,以数据信号ca信号和dq信号为例,dram接收从cpu而来的ca信号在进入芯片后经过后续电路后译码成各种命令继而控制dram芯片的各种操作。dq信号是dram数据通道,在写入时接收从cpu传来的数据;在读取时将dram内存储的数据读出传出给cpu。当dram接收来自cpu的命令信号和数据信号时,输入信号在传输过程中的有效宽度会减小,如果输入信号宽度过小,在该信号进入dram后经过一系列数字逻辑后,由于数字逻辑本身的延迟等特性会导致最后译码结果丢失掉原本的信息。

3.输入信号的宽度如果特别大,在后续数字逻辑部分中因宽度减小并不一定导致数据丢失,但可能引起信号失真。宽度过小的输入信号在经过接收器后在后续数字逻辑部分过程中数据丢失的情况特别严重,是亟需解决的问题。显然通过一味大幅调高输入信号的做法不可行且未必能确保数据不丢失。现有技术中并没有十分有效的解决办法,存在的难点主要有:(1)必须要检测到数据丢失发生数字逻辑部分哪一段,才能相应处理;(2)控制延迟量控制宽度减小以避免信号宽度消失的做法技术难度高,实现代价过大。

4.因此目前需要研究一种输入信号处理方法及相应的存储器电路结构,无须额外设计控制延迟量,就能解决在存储器芯片中,输入信号在传输过程中因宽度减小而导致失真甚至数据丢失的问题。

技术实现要素:

5.本发明是为解决上述现有技术的全部或部分问题,一方面提供一种输入信号处理方法,避免在存储器芯片中,输入信号在后续数字逻辑部分过程中数据丢失的风险。另一方面提供了相应的存储器电路结构。

6.本发明提供的输入信号处理方法,包括:将输入信号分离为上升沿信号和下降沿信号;将所述上升沿信号和所述下降沿信号分别经过相同的逻辑链路,相应得到第一信号和第二信号;将所述第一信号和所述第二信号进行异或合并,得到命令信号并输出。将输入信号的上升沿和下降沿分离为两路信号经过相同的逻辑链路再合并,相同的逻辑链路对所述第一信号和所述第二信号的延迟时间一致,合并后传出的信号与原本的输入信号宽度保持一致,能够避免输入信号在经过一条逻辑链路时由于上升沿和下降沿的延迟量不同而导致信号宽度减小以至于消失的情况,保障了数据的完整性,也无须采取额外手段监控输入信号宽度的减小,有效提高了存储器芯片工作的可靠性。

7.当所述输入信号为模拟信号时,在经过相同的逻辑链路之前,将模拟信号转为数字信号。

8.将所述输入信号分离为所述上升沿信号和所述下降沿信号的方法包括同步分频或异步分频。采用同步分频,无传输延迟累积效应,最终的输出分频信号与输入时钟信号之间的相位偏差很小;采用异步分频可以可靠地工作在较高的频率下。

9.所述上升沿信号和所述下降沿信号分别经过相同的逻辑链路的过程包括:时钟抓取信号、信号译码为命令、时钟延迟调正和命令设置。经过所述逻辑链路直至完成了对命令进行控制、参数设置等处理,所述第一信号和所述第二信号是分别完成了常规dram完整的数字逻辑部分处理后的信号,将其合并得到传出的信号作为最终的命令信号,数据完整性好。

10.本发明另一方面提供的存储器电路结构,是一种存储器中处理信号的电路结构,包括沿信号传递方向依次设置的分频器、数字逻辑单元和异或门电路单元;所述数字逻辑单元包括相同的两条逻辑链路,所述逻辑链路的输出端与所述异或门电路单元的输入端连接;所述分频器用于将输入的信号分离为上升沿信号和下降沿信号;所述数字逻辑单元用于将所述上升沿信号和下降沿信号分别进行处理得到命令信号的上升沿部分和下降沿部分;所述异或门电路单元用于将所述上升沿部分和所述下降沿部分合并得到所述命令信号后输出。

11.一般情况中,所述存储器电路结构还包括模数转换模块,所述模数转换模块用于将模拟信号转为数字信号;所述模数转换模块设置在所述数字逻辑单元在信号传递路径的上游。所述模数转换模块可以设置在沿信号传递方向上所述分频器之前或者所述分频器与所述数据逻辑单元之间,无论输入信号是模拟信号还是数字信号都能进行处理,应用更灵活,对输入信号的限制少。

12.所述分频器为模拟分频器或数字分频器。根据输入信号的具体情况,可以先通过模拟分频器将输入的模拟信号分离后再转换为数字信号分别传入所述数字逻辑单元;也可以通过数字分频器直接将接收的数字信号分离后分别传入所述数字逻辑单元。

13.所述逻辑链路包括沿信号传递方向依次设置的时钟抓取信号模块、命令译码模块、延迟调整模块和控制模块;所述时钟抓取信号模块用于将输入信号与输入时钟对齐;所述延迟调整模块用于时钟延迟调正;所述命令译码模块用于将输入信号翻译成相应的命令;所述控制模块用于完成命令的设置。所述逻辑链路包含了常规dram的数字逻辑部分,能够完成将接收到数据信号转换为命令信号的过程,经过两条所述逻辑链路后合并得到的传出信号直接可以作为命令信号,保障逻辑处理过程没有数据丢失,工作可靠性更高,且设置两条完全相同的逻辑链路易于实现,不增加工艺难度。

14.所述输入信号包括ca信号和dq信号。

15.与现有技术相比,本发明的主要有益效果:1、本发明的输入信号处理方法,步骤简洁,无须额外监控信号宽度的减小情况,经历两条相同的逻辑链路再合并,易于实施且节约成本,能有效避免因信号宽度消失而导致数据丢失,提高了存储器芯片工作的可靠性和数据处理效率。

16.2、本发明的存储器电路结构,是一种存储器中处理信号的电路结构,包含分频器、两条相同的逻辑链路和异或门电路单元,通过将输入信号的上升沿和下降沿分离后经历同样的逻辑链路后由异或门电路单元合并输出,仅增加一条相同的逻辑链路,结构简单、易于制备且能保持输入信号的宽度不变,避免了输入信号在经历数字逻辑部分后数据丢失的风

险,工作可靠性强。

附图说明

17.图1为本发明示例的输入信号转换为命令信号的过程原理示意图。

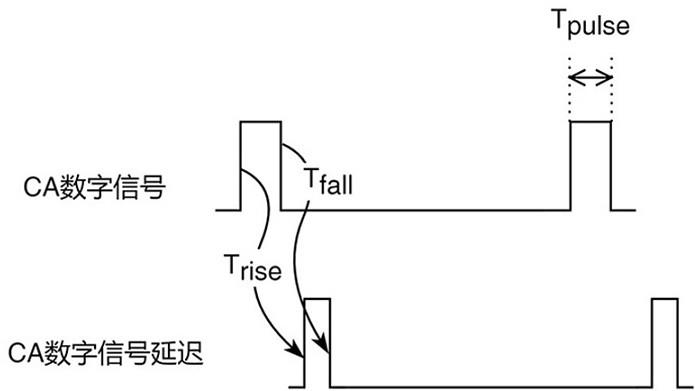

18.图2为本发明示例的信号的上升沿和下降沿的延迟波形图。

19.图3为本发明实施例一的输入信号处理方法示意图。

20.图4为本发明实施例一的输入信号及其分离后的波形示意图。

21.图5为本发明实施例一的两条逻辑链路延迟波形示意图。

22.图6为本发明实施例二的存储器电路结构示意图。

23.图7为本发明实施例二的接收器构成示意图。

24.图8为本发明实施例二的两条逻辑链路示意图。

25.图9为本发明实施例三的接收器构成示意图。

26.图10本发明实施例三的输入信号分频过程的波形示意图。

具体实施方式

27.在下述实施例中采用特定次序描绘了实施例的操作,这些次序的描述是为了更好的理解实施例中的细节以全面了解本发明,但这些次序的描述并不一定与本发明的方法一一对应,也不能以此限定本发明的范围。

28.为了便于理解本发明的工作原理,以下对dram芯片中输入信号经逻辑链路传递的过程进行示例,但不以任何形式限制本发明。

29.如图1所示,一般的情况中,输入信号包括地址信号(ca信号)和dram数据通道信号(dq信号)。以ca信号为例,ca信号一般要经过接收器rcv、时钟抓取信号模块、命令译码模块、延迟调整模块delay adj、进入控制模块ctr后作为命令信号再传输到其他电路模块。图1中示例的1st latch为第一级时钟抓取信号模块,示例的命令译码模块采用一个命令译码器cmd dec实现。一般的接收器rcv包括两级模块,第一级是信号放大模块将模拟差分信号进行放大,第二级是模数转换模块将模拟信号转为数字信号。ca信号输入接收器rcv经过模数转换后的数字信号ca_digital需要经过第一级时钟抓取信号模块1st latch等各种模块后才作为命令信号传出。但是当ca信号的信号宽度本身比较小的时候,信号在经过后续逻辑链路后失去有效信息的风险非常高。图2示例的情况中以数字信号ca_digital经过一个延迟电路的情况为例,当输入信号经过一个延迟电路时,延迟电路对信号的上升沿和下降沿的延迟不同,相应分别记为trise和tfall,trise与tfall是不同的,当trise》tfall时,信号宽度会减小。将输入信号的宽度记为tpulse,当出现了trise》tfall+tpulse时,延迟后的信号ca_digital_delay宽度就消失了,dram芯片将丢失信息。输入信号在逐个经历各种模块时,有可能在经历任何一个模块后信号宽度消失。如果要监测信号在哪一个模块出现宽度消失或者检测信号宽度是否消失再相应设计电路结构难度高,控制输入信号的trise和tfall需要进行的额外设计也非常复杂。信号宽度减小即使不消失,也存在信号失真,如果信号宽度消失则导致数据信息丢失,读取命令失败,dram芯片不能正常工作。

30.实施例一本实施例中提供一种输入信号的处理方法,能避免信号宽度的减小。如图3所示,

该处理方法包括:将输入信号分离为上升沿信号和下降沿信号;将上升沿信号和下降沿信号分别经过相同的逻辑链路,相应得到第一信号和第二信号;将第一信号和第二信号进行异或合并,得到命令信号并输出。示例的情况中,输入信号为模拟信号,首先将输入的模拟信号转换为数字信号,再通过同步分频的方式将其分离为上升沿信号和下降沿信号。也有些实施例中采用异步分频分离得到上升沿信号和下降沿信号,并不限定。如图4所示,将上升沿信号记为ca_rise,将下降沿信号记为ca_fall,ca信号被分离成ca_rise和ca_fall。如图5所示,输入信号ca是模拟信号,先将其转换为数字信号记为ca_digital。示例的情况ca_rise和ca_fall分别经过相同的逻辑链路的过程包括:时钟抓取信号、信号译码为命令、时钟延迟调正和命令设置。在dram芯片中,需要对命令进行一些参数设置,最终的从控制模块ctr输出的结果是芯片后面的控制信号(命令信号)。在有些实施例中ca_rise和ca_fall经过逻辑链路得到命令信号的过程还包括其他处理,在此不限定具体情况。

31.如图5所示,在本实施例中以ca_digital经历时钟抓取信号的延迟情况为例,ca_rise和ca_fall这两个信号分别经过延迟得到ca_rise_d和ca_fall_d,即使延迟的trise和tfall不一致,但是其对ca_rise和ca_fall的上升沿延迟时间一致,在继续经历后续逻辑链路后,将其异或后最终得到ca_out是原本的信号宽度,既不会出现命令信号失真也不会出现信息数据的丢失。

32.实施例二本实施例中提供的存储器电路结构如图6所示,通过该存储器电路结构可实施本发明的输入信号处理方法。示例的存储器电路结构包括沿信号传递方向t依次设置的分频器m、数字逻辑单元logic和异或门电路单元xor。数字逻辑单元logic包括相同的两条逻辑链路l1和l2,逻辑链路l1和l2的输出端分别与异或门电路单元xor的两个输入端连接。分频器m用于将输入的信号分离为上升沿信号ca_rise和下降沿信号ca_fall。数字逻辑单元logic用于将上升沿信号ca_rise和下降沿信号ca_fall分别进行处理得到命令信号ca_out的上升沿部分和下降沿部分。异或门电路单元xor用于将上升沿部分和下降沿部分合并得到命令信号ca_out后输出。在本实施例中分频器m采用一个数字分频器,在数字分频器之前设置有接收器rcv,示例的接收器rcv如图7所示,包括两级模块,沿信号传递方向t依次是第一级的信号放大模块r1和第二级的模数转换模块r2。图7示例的情况中输入信号是地址信号ca,是一对模拟差分信号,ca信号和参考电压vref输入接收器rcv,经信号放大模块r1将其放大后,在经过模数转换模块r2将输入的模拟信号转换为数字信号,得到一对数字差分信号ca_t和ca_b。结合参考图6,分频器m设置在数模转换模块r2与数字逻辑单元logic之间,ca_t和ca_b经分频器m后,得到上升沿信号ca_rise和下降沿信号ca_fall分别输入逻辑链路l1和l2。在输入信号到达数字逻辑单元logic之前需要先经过模数转换模块r2,接收器rcv的具体结构可以根据实际应用相应设置,在此并不限定。

33.在本实施例中,两条相同的逻辑链路l1和l2的构成如图8示例。每条逻辑链路包括沿信号传递方向依次设置的时钟抓取信号模块、命令译码模块、延迟调整模块delay adj和控制模块ctr。在有些实施例中根据存储器芯片具体工作需要,逻辑链路还可以设置有其他模块,使得经历逻辑链路后合并得到的传出信号是符合工作需要的命令信号。示例时钟抓取信号模块是一个锁存器latch,用于将输入信号(ca信号)与输入时钟对齐。根据实际工作需要,时钟抓取信号模块也可以有更多个锁存器latch级联实现,在此并不限定。示例的命

令译码模块是一个命令译码器cmd dec用于将输入信号翻译成相应的命令。延迟调整模块delay adj是一个时钟延迟调正电路。控制模块ctr用于完成命令的设置。结合参考图6,上升沿信号ca_rise和下降沿信号ca_fall分别经历逻辑链路l1和l2后分别得到了命令信号ca_out的上升沿部分和下降沿部分,即上述的第一信号和第二信号,输入异或门电路单元xor进行异或合并后得到了命令信号ca_out。ca信号宽度的即使很小,在经过数字逻辑单元logic后也不会消失。即使逻辑链路l1和l2还包括其他模块,只要将从逻辑链路l1和l2输出的信号进行异或合并后就能获得与输入信号宽度一致的命令信号。

34.实施例三本实施例与实施例二的区别主要在于分频器采用模拟分频器。如图9所示,本实施例的存储器电路结构中,模拟分频器m采用cml(current mode logic,电流模式逻辑)分频器,沿信号传递方向t设置在模数转换模块r2之前(上游),示例情况中分频器设置在接收器rcv中作为接收器rcv的一部分,cml分频器设置在信号放大模块r1和模数转换模块r2之间。仍以输入信号为地址信号ca为例参考图10,经过信号放大模块r1后的一对模拟差分信号输入到cml分频器,分别降频后输出两对模拟差分信号,即ca1_t、ca1_b和ca2_t、ca2_b。参考图9,ca1_t、ca1_b和ca2_t、ca2_b进入模数转换模块r2后分别输出数字信号,即上升沿信号ca_rise和下降沿信号ca_fall。结合参考图6上升沿信号ca_rise和下降沿信号ca_fall再相应分别输入数字逻辑单元logic中的逻辑链路l1和l2,最终通过异或合并为ca_out。

35.本发明为了便于叙述清楚而采用的一些常用的英文名词或字母只是用于示例性指代而非限定性解释或特定用法,不应以其可能的中文翻译或具体字母来限定本发明的保护范围。还需要说明的是,在本文中,诸如“第一”和“第二”等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1