一种高灵活性存储计算阵列

1.本发明属于半导体(semiconductor)和cmos超大规模集成电路(ulsi)中的非挥发性存储器(non-volatile memory)与存内计算(compute-in-memory)技术领域,具体涉及一种使用非挥发性存储器阵列进行向量矩阵乘法计算(vector matrix multiplication)的阵列结构。

背景技术:

2.随着人工智能与深度学习技术的发展,人工神经网络在自然语言处理、图像识别、自动驾驶、图神经网络等领域得到了广泛的应用。然而逐渐增大的网络规模导致数据在内存与传统计算设备如cpu与gpu间的搬运消耗了大量的能量,这被称为冯诺依曼瓶颈。在人工神经网络算法中占据最主要部分的计算为向量矩阵乘法计算(vector matrix multiplication)。基于非挥发性存储器(non-volatile memory)的存内计算(compute-in-memory),把权重存储在非挥发性存储器单元中,并在阵列中进行模拟向量矩阵乘法计算,避免了数据在内存与计算单元间的频繁搬运,被认为是一种有希望解决冯诺依曼瓶颈的途径。

3.图1为基于非挥发性器件阵列进行向量矩阵乘法的示意图。非挥发性存储器器件如rram、pcram、mram等在权值写入后,把权值存储在器件的电导值上。器件组织成阵列的形式,从一端输入电压作为向量矩阵乘法的输入,阵列中通过欧姆定律与基尔霍夫定律计算,在阵列的另一端得到的电流为向量矩阵乘法的求和结果。阵列中器件单元可以使用1r器件或1t1r器件。输入可以通过数模转换器(dac)输入多值电压,或通过缓冲器(buffer)输入二值电压。求和结果通常使用模数转换器(adc)读出。由于模数转换器面积与阵列单元面积在长度上不匹配,通常使用多路选择器(mux)让阵列中多个列共用一个模数转换器。

4.由于1t1r避免了写串扰的问题,在较大的阵列中通常使用1t1r的器件。在约定的命名方式中,连接晶体管栅极的线为字线(word line,wl),连接晶体管源极的线为源线(source line,sl),连接器件一端的线为位线(bit line,bl)。用于向量矩阵乘法的传统1t1r阵列结构如图2(a)或(b)。图2(a)中,通过字线打开所有晶体管,电压从源线输入,从位线读出电流和。图2(b)中,在源线上输入相同的读电压,通过字线控制一行的开启与关闭代表输入为“1”或“0”,仍然从位线读出电流和。以上两种阵列结构及其他常用阵列结构相同的特点是,字线wl与输入方向平行,这是沿用于传统存储器阵列结构的设计。

5.然而传统阵列结构在实现存内计算存在两个问题:1、假如使用数模转换器输入多值电压,存在数模转换器的面积与阵列单元面积在版图高度上不匹配,以及每行都要使用一个数模转换器,这带来消耗功耗高的问题。假如使用缓冲器输入二值电压,对高精度输入只能通过多次输入脉冲序列来表示,这增加了计算的延时,并且需要多次开启阵列计算进行多比特输入,这增加了阵列开启次数与模数转换器工作次数,也带来功耗的增加。2、传统的字线与输入方向平行的设计,在物理矩阵规模大于实际计算需要的矩阵规模时,无法关闭未用到的列上的器件的电流,这导致功耗的浪费。

技术实现要素:

6.针对以上问题,本发明提供一种高灵活性存储计算阵列。

7.本发明提供的技术方案如下:

8.一种高灵活性的存内计算阵列,其特征在于,包含1t1r阵列,把1t1r阵列的若干行划分为一个行段,若干列划分为一个列段,每个行段对应一个输入单元,每个列段对应一个输出单元,每个1t1r单元由一个mos管与一个非挥发性存储器件组成,其中mos管的栅极与字线连接,mos管的源极与源线连接,mos管的漏极与非挥发性存储器件一端连接,非挥发性存储器件一端与mos管漏极连接,另一端与位线连接。一条源线连接阵列一行中所有单元的mos管的源极,与输入方向平行;一条位线连接阵列一列中所有单元的非挥发性器件,与输入方向垂直;一条字线连接阵列中一列中所有单元的mos管的栅极,与输入方向垂直,所述1t1r阵列的外围电路包括字线驱动、输入单元、输出单元、线性稳压器与控制模块,用于选通一条对应的行和一条对应的列,把未选择的行的输入浮空,并把未选择的列对应的字线输入地电压以关闭晶体管,若1t1r阵列被划分为m个行段,在版图设计上对应m个输入单元,同时1t1r阵列被划分为n个列段,在版图设计上对应n个输出单元,每个行段包含b行存储单元,每个列段包含c列存储单元,则一个物理阵列划分为b*c个逻辑阵列,每个逻辑阵列包含的矩阵大小为m行*n列,每次执行向量矩阵乘法选择其中一个逻辑阵列进行计算,并在未选中存储单元上不产生功耗,在逻辑阵列中,选择其中任意行与任意列组成逻辑子阵列进行计算。

9.进一步,所述字线驱动用于控制1t1r阵列的字线输入电源电压或地电压,以打开或关闭一列字线。

10.进一步,所述输入单元包括输入寄存器,电压多路选择器与行多路选择器,输入寄存器由(a+1)个d触发器组成,(a+1)位扫描链输入在时钟信号的控制下,依次从最下方的输入单元扫描进上方的输入单元的输入寄存器中;输入寄存器的前a个输出为电压多路选择器译码信号,连接到电压多路选择器中的a-a译码器,第a+1个输出为行多路选择器使能信号,连接到行多路选择器的与门。电压多路选择器包含一个a-a译码器与a个传输门;a-a译码器把输入寄存器输出的a个译码信号转换成a位独热码输出,即a位输出里只有一位是高电平,其余位是低电平,以打开其中一个传输门,数量关系为a=2a;电压多路选择器把ldo输出的a个电压中选出一个送到行多路选择器,行多路选择器包含一个b-b译码器、b个与门与b个传输门;b-b译码器把b位行译码信号转换成b位独热码输出,即b位输出里只有一位是高电平,其余位是低电平,并连接到b个二输入与门,数量关系为b=2b;b个二输入与门的另一个输入为输入寄存器输出的行多路选择器使能信号,当使能信号为高电平时,与门输出与b-b译码器输出相同,选择打开其中一个传输门,在b行源线中选择一个与电压多路选择器的输出相连,其余源线处于浮空状态,当使能信号为低电平时,与门输出全部为低,所有传输门关闭,b行源线全部处于浮空状态。

11.进一步,所述输出单元结构包括列多路选择器,钳位电路与模数转换器,列多路选择器包含一个c-c译码器与c个传输门。c-c译码器把c位列译码信号转换成c位独热码输出,即c位输出里只有一位是高电平,其余位是低电平,数量关系为c=2c;译码器的输出选择打开其中一个传输门,在c列位线中选择一个与钳位电路相连,其余位线处于浮空状态;钳位电路使用运算放大器op与反馈电阻rf把选中的位线钳位在参考电位,此时运算放大器输出

电压等于向量矩阵乘法计算结果。所述输出电压被晶体管n1与电容c1组成的采样保持电路存储在c1上,最后输入模数转换器转换成x-比特数字信号,x是模数转换器设计精度,所述模数转换器采用flash-adc或sar-dac结构。

12.进一步,所述输入单元使用线性稳压器,统一产生计算所需要的多种输入电压,电压多路选择器用于将电压输入到行多路选择器,行多路选择器与1t1r阵列的源线连接,1t1r阵列的位线通过列多路选择器连接到一个模数转换器。

13.本发明相比传统阵列结构主要包括三个特点。

14.第一个特点是把字线方向从与输入平行换成与输入垂直。改变带来两个好处:一是使未选择的行输入保持浮空就能屏蔽一行,使其不影响阵列其余部分的计算。二是可以通过把字线输入低电压来关闭晶体管,达到屏蔽一列的效果,使其不影响阵列其余部分的计算。因此所提出的设计可屏蔽阵列中的任意数量的行与列,可选择一个大阵列中的任意子阵列进行计算,而不会在被屏蔽的器件上有电流流过导致功耗增加。

15.第二个特点是在输入单元内增加了行多路选择器。行多路选择器在多个阵列的行中选择一个与电压多路选择器相连。此设计的原因是,即使使用电压多路选择器代替数模转换器能减少版图高度不匹配问题,但仍然需要多个行的高度去匹配一个电压多路选择器。

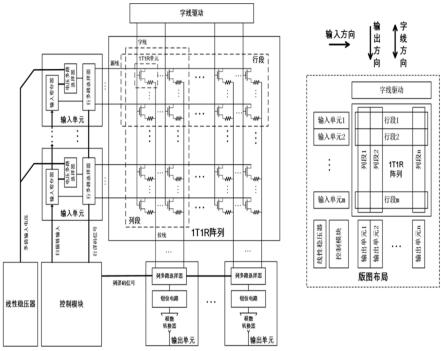

16.第三个特点是把输入单元的数模转换器或缓冲器换成共用的线性稳压器。线性稳压器统一产生计算所需要的多种输入电压,同时输入到所有输入单元,在输入单元通过电压多路选择器选择其中一个电压连接到阵列上。这减少了每行都要使用一个数模转换器输入带来版图不匹配问题与数模转换器消耗功耗高的问题。同时也可以利用多值电压输入带来的好处,无需像缓冲器输入二值电压的方式通过多次开启阵列的方式实现多比特输入,减少计算延迟与模数转换器的工作次数。

附图说明

17.图1为基于非挥发性器件阵列进行矩阵乘法的示意图;

18.图2为两种传统用于向量矩阵乘法的1t1r阵列结构示意图;

19.图3为本发明提出的阵列结构及外围电路示意图;

20.图4为本发明提出的输入单元电路图;

21.图5为本发明使用的输出单元电路图;

22.图6为本发明提出的阵列结构选择逻辑阵列的工作状态示意图;

23.图7为本发明提出的阵列结构选择逻辑子阵列的工作状态示意图。

具体实施方式

24.下面结合附图和具体实例对本发明进行详细说明。

25.参考图3,本发明高灵活性的存内计算阵列及其外围电路设计,包括1t1r阵列、字线驱动、输入单元、输出单元与控制模块。1t1r阵列由1t1r单元组成,每个1t1r单元由一个mos管与一个非挥发性存储器件组成,其中mos管的栅极与字线连接,mos管的源极与源线连接,mos管的漏极与非挥发性存储器件一端连接,非挥发性存储器件一端与mos管漏极连接,另一端与位线连接。一条源线连接阵列一行中所有单元的mos管的源极,与输入方向平行;

一条位线连接阵列一列中所有单元的非挥发性器件,与输入方向垂直;一条字线连接阵列中一列中所有单元的mos管的栅极,与输入方向垂直。设置字线驱动,用于控制1t1r阵列的字线输入电源电压或地电压,以打开或关闭一列字线。在版图上,把1t1r阵列的若干行划分为一个行段,若干列划分为一个列段,每个行段对应一个输入单元,每个列段对应一个输出单元。如右侧版图布局所示,1t1r阵列被划分为m个行段,在版图设计上对应m个输入单元,同时1t1r阵列被划分为n个列段,在版图设计上对应n个输出单元。

26.用输入单元代替dac实现多值输入功能。输入单元电路如图4所示,内部包括输入寄存器,电压多路选择器与行多路选择器。输入寄存器由(a+1)个d触发器组成,(a+1)位扫描链输入在时钟信号的控制下,依次从最下方的输入单元扫描进上方的输入单元的输入寄存器中。输入寄存器的前a个输出为电压多路选择器译码信号,连接到电压多路选择器中的a-a译码器,第(a+1)个输出为行多路选择器使能信号,连接到行多路选择器的与门。电压多路选择器包含一个a-a译码器与a个传输门。a-a译码器把输入寄存器输出的a个译码信号转换成a位独热码输出,即a位输出里只有一位是高电平,其余位是低电平,以打开其中一个传输门,数量关系为a=2a。电压多路选择器把ldo输出的a个电压中选出一个送到行多路选择器。行多路选择器包含一个b-b译码器、b个与门与b个传输门。b-b译码器把b位行译码信号转换成b位独热码输出,即b位输出里只有一位是高电平,其余位是低电平,并连接到b个二输入与门,数量关系为b=2b。b个二输入与门的另一个输入为输入寄存器输出的行多路选择器使能信号,当使能信号为高电平时,与门输出与b-b译码器输出相同,选择打开其中一个传输门,在b行源线中选择一个与电压多路选择器的输出相连,其余源线处于浮空状态,当使能信号为低电平时,与门输出全部为低,所有传输门关闭,b行源线全部处于浮空状态。

27.输出单元电路如图5所示。输出单元结构包括列多路选择器,钳位电路与模数转换器。列多路选择器包含一个c-c译码器与c个传输门。c-c译码器把c位列译码信号转换成c位独热码输出,即c位输出里只有一位是高电平,其余位是低电平,数量关系为c=2c。译码器的输出选择打开其中一个传输门,在c列位线中选择一个与钳位电路相连,其余位线处于浮空状态。钳位电路使用运算放大器op与反馈电阻rf把选中的位线钳位在参考电位,此时运算放大器输出电压等于向量矩阵乘法计算结果。此输出电压被晶体管n1与电容c1组成的采样保持电路存储在c1上,最后输入模数转换器转换成x-比特数字信号,x是模数转换器设计精度,模数转换器可以使用flash-adc或sar-dac结构。

28.一个行多路选择器只选通一条对应的行上的源线,一个列多路选择器只选通一条对应的列上的位线,未选中行中的源线与未选中列中的位线都保持浮空。行多路选择器相比列多路选择器增加了把所有对应源线都浮空的功能,以实现灵活的子阵列选择功能。假设一个物理阵列包含了m个行段与n个列段,每个行段包含b行存储单元,每个列段包含c列存储单元,则一个物理阵列可划分为b*c个逻辑阵列,每个逻辑阵列包含的矩阵大小为m行*n列。每次执行向量矩阵乘法可以选择其中一个逻辑阵列进行计算,并在未选中存储单元上不产生功耗,在逻辑阵列中,也可以选择其中任意行与任意列组成逻辑子阵列进行计算,并在所有未选中存储单元上都不产生功耗。

29.图6为本发明所提出的阵列结构选择逻辑阵列的工作状态示意图。图6中以1t1r物理阵列大小为6行*6列为例,物理阵列分为三个行段,每个行段包括两行器件,物理阵列分为三个列段,每个列段包括两列器件。每个行段对应一个输入单元,每个列段对应一个输出

单元。在一次向量矩阵乘法计算中,一个输入单元中的行多路选择器只能在一个行段中选通一行,一个输出单元的列多路选择器只能在一个列段中选通一列。所有被选通的行与列上的器件组成用于本次向量矩阵乘法计算的阵列,被称为逻辑阵列(logical array)。相对的,整个阵列被称为物理阵列(physical array)。物理阵列被分成4个逻辑阵列,每个逻辑阵列包括3行*3列存储单元。每次向量矩阵乘法计算只能选择其中一个逻辑阵列进行计算。如图6中示意,行译码信号为0,所有行译码器选择第1、3、5行组成阵列,列译码信号为0,所有列译码器选择第1、3、5列组成阵列,所选中的3行*3列器件组成本次计算的逻辑阵列,如图中红色所示。在列译码器选择1、3、5列时,字线驱动要同时把1、3、5列的字线电压输入电源电压(vdd),把其余字线输入地电压(gnd)。未选中的单元可以分为两类,

①

未选中列的单元,

②

选中列上未选中行的单元。分析可得,

①

在未选中列,由于晶体管都栅极都接地,1t1r器件在源线与位线间的通路被关闭,没有电流流过。

②

在选中列上的未选中行,晶体管栅极接电源电压,晶体管打开,位线被钳位到地电平,源线浮空,因此也没有电流流过。这说明每次执行向量矩阵乘法可以选择其中一个逻辑阵列进行计算,并在未选中存储单元上不产生功耗。在输入模块,输入数据通过扫描链存入每个输入单元的输入寄存器,并产生电压多路选择器译码信号,在线性稳压器产生的多个输入电压中选出一个送入行多路选择器,以代替数模转换器的功能。在输出模块被选中列的位线电流通过钳位电路转换成电容上的电压,最终被adc转换成数字信号读出。

30.图7为在逻辑阵列中选择一部分逻辑子阵列(logical sub array)进行计算的示意图。在逻辑阵列中可任意选择一部分行与列组成逻辑子阵列进行向量矩阵乘法计算。如图7中所示为例,选择关闭行多路选择器3对应的行,与关闭列多路选择器3对应的列,而把行多路选择器1与2,列多路选择器1与2对应的行列组成一个2行*2列大小的逻辑子阵列。方法是通过扫描链把输入单元3中的行多路选择器使能信号置低,以关闭所有与门,使输入单元3对应的全部源线浮空,同时字线驱动把输出单元3对应的所有存储单元的字线置到地电平,以关闭所有输出单元3对应的列。如图所示,未选中的单元可以分为两类,

①

未选中列的单元,

②

选中列上未选中行的单元。分析可得,

①

在未选中列,由于晶体管都栅极都接地,1t1r器件在源线与位线间的通路被关闭,没有电流流过。

②

在选中列上的未选中行,晶体管栅极接电源电压,晶体管打开,位线被钳位到地电平,源线浮空,因此也没有电流流过。这说明在逻辑阵列中可任意选择一部分行与列组成逻辑子阵列进行向量矩阵乘法计算,并在未选中存储单元上不产生功耗。在选中列与行中的器件,其计算方法与图6相同。

31.以上实施例仅用以说明本发明的技术方案而非对其进行限制,本领域的普通技术人员可以对本发明的技术方案进行修改或者等同替换,而不脱离本发明的精神和范围,本发明的保护范围应以权利要求所述为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1