包括具有氧和碳单层的超晶格的半导体器件及相关方法与流程

1.本公开一般而言涉及半导体器件,并且更具体地,涉及具有增强的半导体材料的半导体器件及相关方法。

背景技术:

2.已经提出了增强半导体器件的性能的结构和技术,诸如通过增强电荷载流子的移动性。例如,授予currie等人的美国专利申请no.2003/0057416公开了硅、硅锗和松弛硅的应变材料层,并且还包括无杂质的区(否则杂质会造成性能降级)。在上部硅层中产生的双轴应变更改了载流子移动性,从而实现了更高速度和/或更低功率的器件。授予fitzgerald等人的已公开美国专利申请no.2003/0034529公开了也基于类似的应变硅技术的cmos反相器。

3.授予takagi的美国专利no.6,472,685b2公开了一种半导体器件,其包括硅和夹在硅层之间的碳层,使得第二硅层的导带和价带接受拉伸应变。有效质量较小并且已经由施加到栅极电极的电场感应出的电子被限制在第二硅层中,因此,断言n沟道mosfet具有更高的移动性。

4.授予ishibashi等人的美国专利no.4,937,204公开了一种超晶格,其中交替地且外延生长其中少于八个单层并且包含分数或二元或二元化合物半导体层的多个层。主电流流动的方向垂直于超晶格的层。

5.授予wang等人的美国专利no.5,357,119公开了通过减少超晶格中的合金散射而获得的具有更高移动性的si-ge短周期超晶格。沿着这些思路,授予candelaria的美国专利no.5,683,934公开了一种增强移动性的mosfet,该mosfet包括沟道层,该沟道层包括以将沟道层置于拉伸应变下的百分比交替存在于硅晶格中的硅合金和第二材料。

6.授予tsu的美国专利no.5,216,262公开了一种量子阱结构,其包括两个势垒区域和夹在势垒之间的外延生长的薄半导体层。每个势垒区域由交替的sio2/si层组成,其厚度一般在二到六个单层的范围内。在势垒层之间夹有厚得多的硅部分。

7.tsu于2000年9月6日在applied physics and materials science&processing第391-402页在线发表的标题为“phenomena in silicon nanostructure devices”的文章公开了硅和氧的半导体原子超晶格(sas)。公开了在硅量子和发光器件中有用的si/o超晶格。特别地,构造并测试了绿色电致发光二极管结构。二极管结构中的电流流动是垂直的,即,垂直于sas的层。所公开的sas可以包括被诸如氧原子和co分子之类的吸附物质隔开的半导体层。超出被吸附的氧单层的硅生长被描述为具有相当低缺陷密度的外延生长。一种sas结构包括1.1nm厚的硅部分,该部分大约为八个原子硅层,而另一种结构的硅厚度是该硅厚度的两倍。发表在physical review letters第89卷第7期(2002年8月12日)上的luo等人的标题为“chemical design of direct-gap light-emitting silicon”的文章进一步讨论了tsu的发光sas结构。

8.授予wang等人的美国专利no.7,105,895公开了由薄硅和氧、碳、氮、磷、锑、砷或氢

形成的势垒层构造块,由此超过四个数量级进一步减少了垂直流过晶格的电流。绝缘层/势垒层允许在绝缘层旁边沉积低缺陷外延硅。

9.授予mears等人的公开的英国专利申请2,347,520公开了非周期性光子带隙(apbg)结构的原理可以适用于电子带隙工程。特别地,该申请公开了可以调整材料参数(例如,能带最小值的位置、有效质量等),以产生具有期望带结构特点的新型非周期性材料。还公开了其它参数(诸如电导率、热导率和介电常数或磁导率)也可能被设计进该材料中。

10.此外,授予wang等人的美国专利no.6,376,337公开了用于生产半导体器件的绝缘或势垒层的方法,该方法包括在硅基板上沉积一层硅和至少一种附加元素,由此沉积层基本上没有缺陷,使得可以在沉积层上沉积基本上没有缺陷的外延硅。可替代地,一种或多种元素(优选地包含氧)的单层被吸收在硅基板上。夹在外延硅之间的多个绝缘层形成势垒复合物。

11.尽管存在此类方法,但是可能期望进一步的增强以使用先进的半导体材料和处理技术来提高半导体器件的性能。

技术实现要素:

12.一种半导体器件可以包括半导体层和与半导体层相邻的超晶格。超晶格可以包括多个堆叠的层组,每个层组包括:限定基础半导体部分的多个堆叠的基础半导体单层,以及限制在相邻的基础半导体部分的晶格内的至少一个非半导体单层。超晶格的第一层组中的至少一个非半导体单层可以包含氧并且不含碳,并且超晶格的第二层组中的至少一个非半导体单层可以包含碳。

13.在示例实施例中,第二层组可以在超晶格中的第一层组上方。在一个示例实施方式中,半导体层可以包括超晶格下方的基板,并且半导体器件还可以包括超晶格上方的应变半导体层。作为示例,超晶格的第二层组可以包含碳并且不含氧。根据另一个示例,超晶格的第二层组可以包含碳和氧。

14.在一个示例配置中,半导体器件还可以包括在半导体层上并在超晶格中限定沟道的源极区域和漏极区域,以及在超晶格上方的栅极。根据另一个示例实施例,半导体器件还可以包括在超晶格上方的金属层。此外,在一些实施例中,超晶格可以将半导体层划分成第一区域和第二区域,其中第一区域具有与第二区域相同的导电类型和不同的掺杂浓度。根据另一个示例实施方式,超晶格可以将半导体层划分成第一区域和第二区域,其中第一区域与第二区域具有不同的导电类型。作为示例,基础半导体层可以包含硅。

15.另一方面涉及一种用于制造半导体器件的方法,该方法可以包括形成与半导体层相邻的超晶格。超晶格可以包括多个堆叠的层组,每个层组包括:限定基础半导体部分的多个堆叠的基础半导体单层,以及限制在相邻的基础半导体部分的晶格内的至少一个非半导体单层。超晶格的第一层组中的至少一个非半导体单层可以包含氧并且不含碳,并且超晶格的第二层组中的至少一个非半导体单层可以包含碳。

16.在示例实施例中,第二层组可以在超晶格中的第一层组上方。在一个示例实施方式中,半导体层可以包括超晶格下方的基板,并且该方法还可以包括在超晶格上方形成应变半导体层。作为示例,超晶格的第二层组可以包含碳并且不含氧。根据另一个示例,超晶格的第二层组可以包含碳和氧。

17.在一个示例配置中,该方法还可以包括形成在半导体层上并在超晶格中限定沟道的源极和漏极区域,以及在超晶格上方的栅极。根据另一个示例实施例,该方法还可以包括在超晶格上方形成金属层。此外,在一些实施例中,超晶格可以将半导体层划分成第一区域和第二区域,其中第一区域具有与第二区域相同的导电类型和不同的掺杂浓度。根据另一个示例实施方式,超晶格可以将半导体层划分成第一区域和第二区域,其中第一区域与第二区域具有不同的导电类型。作为示例,基础半导体层可以包含硅。

附图说明

18.图1是用在根据示例实施例的半导体器件中的超晶格的非常放大的示意性横截面图。

19.图2是图1中所示的超晶格的一部分的透视原子示意图。

20.图3是根据示例实施例的超晶格的另一个实施例的非常放大的示意性横截面图。

21.图4a是对于现有技术中的块状硅以及对于如图1-2中所示的4/1si/o超晶格,都从伽玛点(g)计算得到的能带结构的曲线图。

22.图4b是对于现有技术中的块状硅以及对于如图1-2中所示的4/1si/o超晶格,都从z点计算得到的能带结构的曲线图。

23.图4c是对于现有技术中的块状硅以及对于如图3中所示的5/1/3/1si/o超晶格,都从伽玛和z点计算得到的能带结构的曲线图。

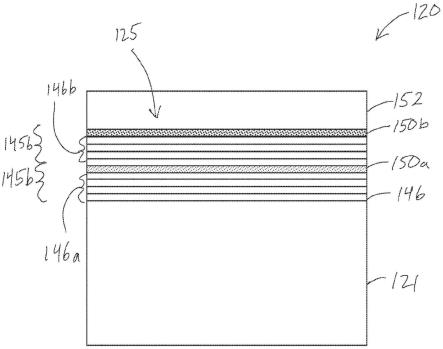

24.图5是根据示例实施例的包括具有碳和氧单层的超晶格的半导体器件的示意性横截面图。

25.图6是图示用于制造图5的半导体器件的示例方法的流程图。

26.图7-10是图5的半导体器件的不同制造运行的二次离子质谱(sims)图。

27.图11是与图10中表示的制造运行对应的x射线衍射(xrd)图。

28.图12是包括结合图5的超晶格的超晶格沟道的半导体器件的示意性横截面图。

29.图13是包括图5的将半导体层划分成具有相同导电类型和不同掺杂剂浓度的区域的超晶格的半导体器件的示意性横截面图。

30.图14是包括图5的超晶格和超晶格上方的金属接触层的半导体器件的示意性横截面图。

31.图15是在示例性实施例中结合图5的超晶格的平面mosfet器件的示意性横截面图。

32.图16-17是结合图5的超晶格的堆叠纳米片环绕栅极(gaa)晶体管的示意性横截面图。

具体实施方式

33.现在将在下文中参考附图更全面地描述示例实施例,在附图中示出了示例实施例。但是,实施例可以以许多不同的形式来实现,并且不应该被解释为限于本文阐述的具体示例。而是,提供这些实施例以使得本公开将是透彻和完整的。贯穿全文,相似的数字指示相似的元件,并且在不同的实施例中使用撇号来指示相似的元件。

34.一般而言,本公开涉及利用增强型半导体超晶格形成半导体器件。增强型半导体

超晶格在本公开中也可以称为“mst”层/膜或“mst技术”。

35.更特别地,mst技术涉及先进的半导体材料,诸如以下进一步描述的超晶格25。申请人理论上不希望受限于此,认为本文所述的某些超晶格降低了电荷载流子的有效质量,并且这导致更高的电荷载流子移动性。有效质量在文献中有各种定义。作为改善有效质量的措施,申请人使用“电导率倒数有效质量张量”,并且针对电子和空穴的和分别对于电子被定义为:

[0036][0037]

并且对于空穴被定义为:

[0038][0039]

其中f是费米-狄拉克(fermi-dirac)分布,ef是费米能量,t是温度,e(k,n)是处于在与波向量k和第n个能带对应的状态的电子的能量,索引i和j是指笛卡尔坐标x、y和z,积分在brillouin区(b.z.)上获取,并且总和在能量分别高于和低于费米能量的电子和空穴的能带上获取。

[0040]

申请人对电导率倒数有效质量张量的定义使得,对于电导率倒数有效质量张量的对应分量的越大值,材料的电导率的张量分量越大。希望不限于此,申请人再次在理论上认为本文所述的超晶格设置电导率倒数有效质量张量的值,以增强材料的导电特性,诸如典型地对于电荷载流子运输的优选方向。适当张量元素的倒数被称为电导率有效质量。换句话说,为了表征半导体材料结构,如上所述并在预期的载流子运输方向上计算的电子/空穴的电导率有效质量被用于区分改进的材料。

[0041]

申请人已经识别出用在半导体器件中的改进的材料或结构。更具体而言,申请人已经识别出具有能带结构的材料或结构,对于这些材料或结构,用于电子和/或空穴的适当电导率有效质量基本上小于针对硅的相应值。除了这些结构的增强的移动性特点外,它们还可以以提供有利于在各种不同类型的器件中使用的压电、热电和/或铁电特性的方式被形成或使用,如将在下面进一步讨论的。

[0042]

现在参考图1和2,材料或结构为超晶格25的形式,其结构被控制在原子或分子水平,并且可以使用原子或分子层沉积的已知技术来形成。超晶格25包括以堆叠关系布置的多个层组45a-45n,如通过具体参考图1的示意性横截面图可能最好地理解的。

[0043]

超晶格25的每个层组45a-45n说明性地包括多个堆叠的基础半导体单层46,其限定相应的基础半导体部分46a-46n和其上的能带改性层50。为了说明清楚,在图1中用点划线指示能带改性层50。

[0044]

能带改性层50说明性地包括一个非半导体单层,该非半导体单层被约束在相邻的基础半导体部分的晶格内。“约束在相邻的基础半导体部分的晶格内”是指来自相对的基础半导体部分46a-46n的至少一些半导体原子通过其间的非半导体单层50化学键合在一起,

如图2中所看到的。一般而言,通过控制通过原子层沉积技术沉积在半导体部分46a-46n上的非半导体材料的数量,使得并非所有(即,小于全部或100%覆盖率)可用半导体键合位点上都填充有与非半导体原子的键,使得这种构造成为可能,如下面将进一步讨论的。因此,当半导体材料的另外的单层46沉积在非半导体单层50上或上方时,新沉积的半导体原子将填充在非半导体单层下方的半导体原子的剩余的空键合位点。

[0045]

在其它实施例中,有可能可以多于一个这样的非半导体单层。应该注意的是,本文中对非半导体或半导体单层的提及是指,如果用于该单层的材料以块状形成,那么它将是非半导体或半导体。即,如本领域技术人员将认识到的,材料(诸如硅)的单个单层不一定表现出与如果以块状或以相对厚的层形成时相同的特性。

[0046]

申请人从理论上阐明而不希望限制于此,能带改性层50和相邻的基础半导体部分46a-46n使得超晶格25对于在平行层方向上的电荷载流子具有比其它方式将存在的更低的适当电导率有效质量。以另一种方式考虑,这个平行方向与堆叠方向正交。能带改性层50还可以使得超晶格25具有共同的能带结构,同时还有利地用作在超晶格的垂直上方和下方的层或区域之间的绝缘体。

[0047]

而且,这种超晶格结构还可以有利地充当在超晶格25的垂直上方和下方的层之间的掺杂剂和/或材料扩散的屏障。这些特性因此可以有利地允许超晶格25提供用于高k电介质的界面,该界面不仅减少高k材料向沟道区域中的扩散,而且还可以有利地减少不想要的散射效应并改善器件移动性,如本领域技术人员将认识到的。

[0048]

理论上还认为包括超晶格25的半导体器件可以基于比其它情况下将存在的更低的电导率有效质量而享有更高的电荷载流子移动性。

[0049]

在一些实施例中,并且作为由本发明实现的能带设计的结果,超晶格25还可以具有基本上直接的能带隙,这对于例如光电子器件可以是特别有利的。

[0050]

超晶格25还说明性地包括在上层组45n上的盖层52。盖层52可以包括多个基础半导体单层46。作为示例,盖层52可以具有基础半导体的1至100个单层46,并且更优选地10至50个单层。但是,在一些应用中,可以省略盖层52,或者可以使用大于100个单层的厚度。

[0051]

每个基础半导体部分46a-46n可以包括选自iv族半导体、iii-v族半导体和ii-vi族半导体的基础半导体。当然,如本领域技术人员将认识到的,术语“iv族半导体”还包括iv-iv族半导体。更特别地,例如,基础半导体可以包括硅和锗中的至少一种。

[0052]

每个能带改性层50可以包括例如选自氧、氮、氟、碳和碳-氧的非半导体。还期望通过沉积下一层来使非半导体热稳定,由此促进制造。在其它实施例中,非半导体可以是与给定的半导体处理兼容的另一种无机或有机元素或化合物,如本领域技术人员将认识到的。更特别地,例如,基础半导体可以包括硅和锗中的至少一种。

[0053]

应该注意的是,术语“单层”意味着包括单个原子层以及单个分子层。还应该注意的是,由单个单层提供的能带改性层50还意味着包括其中并非所有可能的位点都被占据的单层(即,小于全部或100%的覆盖率)。例如,特别参考图2的原子图,图示了4/1重复结构,其中硅作为基础半导体材料,而氧作为能带改性材料。在所示的示例中,仅一半用于氧的可能位点被占用。

[0054]

在其它实施例中和/或对于不同的材料,如本领域技术人员将认识到的那样,这种一半的占用将不一定是这种情况。实际上,即使在这个示意图中也可以看出给定单层中氧

的各个原子没有沿着平坦的平面精确对准,这也是原子沉积领域的技术人员将认识到的。举例来说,优选的占用范围是可能的充满的氧位点的大约八分之一至二分之一,但是在某些实施例中可以使用其它数量。

[0055]

硅和氧目前广泛用在常规半导体处理中,因此,制造商将能够容易地使用本文中所述的这些材料。原子或单层沉积现在也被广泛使用。因而,如本领域技术人员将认识到的,结合根据本发明的超晶格25的半导体器件可以容易地被采用和实现。

[0056]

希望不限于此,申请人在理论上认为,例如,对于超晶格(诸如si/o超晶格),硅单层的数量应该期望地为七个或更少,以便超晶格的能带在整个超晶格是共同的或相对均匀的,以实现期望的优点。对于si/o,图1和2中所示的4/1重复结构已被建模为指示电子和空穴在x方向上增强的移动性。例如,计算得出的电导率有效质量针对于电子(针对块状硅的各向同性)为0.26,并且对于x方向上的4/1sio超晶格为0.12,导致比率为0.46。类似地,对于块状硅,对于空穴的计算得出的值为0.36,对于4/1si/o超晶格的得出的值为0.16,导致比率为0.44。

[0057]

虽然在某些半导体器件中可能期望这种方向上优先的特征,但是其它器件可以从平行于层组的任何方向上的移动性的更均匀增加中受益。如本领域技术人员将认识到的,对于电子和空穴两者或仅这些类型的电荷载流子之一具有增加的移动性也可以是有益的。

[0058]

超晶格25的4/1si/o实施例的较低电导率有效质量可以小于以其它方式将发生的电导率有效质量的三分之二,并且这适用于电子和空穴两者。当然,也如本领域技术人员将认识到的,超晶格25还可以在其中包括至少一种类型的电导率掺杂剂。

[0059]

实际上,现在附加地参考图3,现在描述具有不同特性的根据本发明的超晶格25'的另一个实施例。在这个实施例中,示出了3/1/5/1的重复图案。更特别地,最低的基础半导体部分46a'具有三个单层,并且第二最低的基础半导体部分46b'具有五个单层。这种图案在整个超晶格25'上重复。能带改性层50'可以各自包括单个单层。对于包括si/o的这种超晶格25',电荷载流子移动性的增强与层在平面中的取向无关。图3中未具体提及的那些其它元件与以上参考图1讨论的那些元件相似,并且在此无需进一步讨论。

[0060]

在一些器件实施例中,超晶格的所有基础半导体部分都可以是相同数量的单层那么厚。在其它实施例中,基础半导体部分中的至少一些可以是不同数量的单层那么厚。在其它实施例中,所有的基础半导体部分可以是不同数量的单层那么厚。

[0061]

在图4a-4c中,呈现了使用密度泛函理论(dft)计算的能带结构。在本领域中众所周知,dft低估了带隙的绝对值。因此,可以通过适当的“剪刀校正”来移位间隙上方的所有能带。但是,已经知道能带的形状可靠得多。垂直能量轴应该以这个角度来解释。

[0062]

图4a示出了对于块状硅(由连续线表示)和对于图1中所示的4/1si/o超晶格25(由点线表示)两者从伽玛点(g)计算出的能带结构。方向涉及4/1si/o结构的单元晶胞,而不是si的常规单元晶胞,但是图中的(001)方向确实与si的常规单元晶胞的(001)方向对应,因此示出了si导带最小值的预期位置。图中的(100)和(010)方向与常规si单元晶胞的(110)和(-110)方向对应。本领域技术人员将认识到的是,图上si的能带被折叠,以针对4/1si/o结构在适当的倒易晶格方向上表示它们。

[0063]

可以看出,与块状硅(si)相比,4/1si/o结构的导带最小值位于伽玛点处,而价带最小值出现在(001)方向上brillouin区的边缘处,我们称之为z点。还可以注意到的是,由

于由附加氧层引入的扰动引起的能带分裂,与si的导带最小值的曲率相比,4/1si/o结构的导带最小值具有更大的曲率。

[0064]

图4b示出了对于块状硅(连续线)和4/1si/o超晶格25(点线)两者从z点计算出的能带结构。这个图图示了价带在(100)方向上的增强曲率。

[0065]

图4c示出了对于块状硅(连续线)以及对于图3的超晶格25'的5/1/3/1si/o结构(点线),都从伽玛和z点两者计算得到的能带结构。由于5/1/3/1si/o结构的对称性,在(100)和(010)方向上计算出的能带结构是等效的。因此,预期电导率有效质量和移动性在平行于层(即,垂直于(001)堆叠方向)的平面上是各向同性的。注意的是,在5/1/3/1si/o示例中,导带最小值和价带最大值均在z点处或其附近。

[0066]

虽然曲率增加指示有效质量减小,但是可以经由电导率倒数有效质量张量计算来进行适当的比较和判别。这导致申请人进一步在理论上认为5/1/3/1超晶格25'应当基本上是直接带隙。如本领域技术人员将理解的,用于光学跃迁的适当矩阵元素是直接带隙行为与间接带隙行为之间的区别的另一个指标。

[0067]

现在转向图5,使用上述技术,可以制造具有(一个或多个)mst层的先进半导体器件,这些mst层在其中结合了不同类型的非半导体材料,诸如氧和碳/碳-氧。在本示例中,半导体器件120说明性地包括半导体层121(例如,基板)和与半导体层相邻的超晶格125。如上文进一步讨论的,超晶格125包括多个堆叠的层组145a-145b,每个层组包括:限定基础半导体部分146a-146b的多个堆叠的基础半导体(例如,硅)单层146,以及每个组的限制在相邻的基础半导体部分的晶格内的相应非半导体单层150a、150b。

[0068]

更特别地,第一层组145a中的(一个或多个)非半导体单层150a包含氧并且不含碳,并且第二层组145b中的(一个或多个)非半导体单层150b包含碳,例如,(一个或多个)全碳单层或(一个或多个)碳-氧单层。如下面将进一步讨论的,碳的包含可以有利地为超晶格内的氧提供更高的稳定性(就热处理期间的迁移而言),但在将碳定位在远离关键界面(例如,栅极界面)的布置中,否则碳可能会导致性能问题。应当注意的是,虽然在图5的示例中示出了具有两个层组145a、145b的4/1图案,但是在不同的实施例中也可以使用其它组/层配置,如上面所讨论的。此外,氧和碳/碳-氧单层定位的顺序在不同的实施例中也可以不同,并且在所有实施例中超晶格125中的氧和碳/碳-氧单层的数量不需要相同。

[0069]

作为背景,化学气相沉积(cvd)硅碳合金生长在过去已经通过流动碳源(诸如sih3ch3(单甲基硅烷))与硅源(诸如硅烷(sih4)、di-硅烷(si2h6)、三硅烷(si3h8)或二氯硅烷(sih2cl2))混合来沉积。这些碳源和硅源可以是稀释的混合物或未稀释的。稀释剂可以包括例如氢气(h2)、氮气(n2)、氩气(ar)或氦气(he)。在减压(rp)cvd期间,上述硅源和碳源进一步用例如载气(诸如h2、n2、ar或he)稀释。气体混合物流过加热的基板,使反应物分子发生反应并沉积在基板上,形成外延层。换句话说,元素在共同的气流中被输送到基板。还使用了其它技术,诸如低压cvd(通常小于1托至1毫托),这通常是现代立式炉将操作的压力,或uhv cvd(10毫托至10-9

托)。mocvd是另一种创建外延sic工艺的示例。

[0070]

前述方法都可以用于运行“脉冲式配量(pulsed dose)”方法来制造在超晶格中包括氧和碳/碳-氧单层的mst膜。“脉冲式配量”是指对于每个非半导体单层制造,不同类型的气体源短暂地流动以产生相应层组45a-45n的(一个或多个)氧或碳/碳-氧单层50。在一个示例方法中,与使碳源与硅源共同流动的传统方法相比,该工艺可以开始于例如以碳源(诸

如丙烯(c3h6))给起始表面配量。可以使用包括碳和其它失去/离开并且不会显著结合到mst膜中的元素的碳源。这样的其它元素可以包括例如氢、氯和氟。环丙烷是脉冲式配量外延的另一个示例源,因为环丙烷是仅包含碳和氢的分子。诸如氟利昂(ccl3f2)和氯二氟甲烷(cf3cfch2)之类的前体也是用于脉冲式配量生长的潜在碳源。在这种情况下,氟和氯将将主要作为副产物离开而碳保留在薄膜中。

[0071]

甲基硅烷(sih3ch3)是脉冲式配量外延的另一个潜在源的示例。这种气体通常用于外延硅碳,但分子中的硅原子会在反应过程中沉积,从而破坏脉冲式配量mst膜制造所需的表面下交换机制。

[0072]

可以执行表面配量工艺,使得被吸收的碳原子不处于如此高的表面密度,使得在配量工艺之后一旦硅源流动用于硅生长,外延就不被中断。此外,在硅生长之前,在表面上配量的许多碳原子可能会经历与表面下硅原子的交换机制。这种表面下交换类似于创建mst氧界面层时发生的情况。这些碳源和硅源可以是稀释或未稀释的混合物。稀释剂可以包括例如氢气(h2)、氮气(n2)、氩气(ar)或氦气(he)。氢气是期望的,因为与氢封端的硅表面接触的碳原子很可能结合到表面下而不是表面上(在表面上碳可以形成否则可能会破坏外延的簇)。

[0073]

另外参考图6的流程图600,现在描述用于制造超晶格120的示例脉冲式配量方法。工艺开始于(方框601)在方框602处制备用于外延生长的基板121(例如,硅)。基板121晶片制备可以包括氢氟酸(hf)湿法清洁,随后是相对低的温度(例如,700℃至900℃)在处理室中进行h2烘烤。其它制备步骤可以包括反应器中相对高温的h2烘烤(大约1000℃或更高),以及预清洁模块中的基板表面制备,如本领域技术人员将认识到的。

[0074]

在方框603处,基板121可以在期望的配量条件下稳定,并且初始基础硅部分146a可以外延形成并使用氧源配量。在其它实施例中,基板121的上部可以用作基础硅部分146a,其使用氧源配量以形成(一个或多个)氧单层150a。优选地选择配量时间和温度,使得氧原子经历与表面下的交换,并且保留在表面的氧的密度不会高到阻止随后的外延硅生长,如上文进一步讨论的。

[0075]

在方框604处,氧表面配量之后是硅生长步骤以形成基础硅部分146b。例如,在氧配量表面上/上方生长1至100埃的硅。生长的硅例如可以在5和40a之间,但是在不同的实施例中也可以使用其它尺度。示例硅源包括si2h6、si3h8、sicl2h2或sihcl3。

[0076]

硅生长之后可以可选地进行蚀刻循环(方框605),诸如但不限于盐酸(hcl)。也可以使用其它蚀刻剂,诸如例如氯气(cl2)或nf3。该蚀刻步骤用于排除在生长或碳配量步骤期间可能引起的任何缺陷。该蚀刻步骤被设计为具有比单晶外延更高的非晶硅、多晶硅和/或错位硅的蚀刻速率。每个周期的蚀刻去除可以小于沉积硅厚度的任何量。例如,当初始硅沉积层的厚度为和的量级时,蚀刻量可以是沉积硅层的20%到30%。关于制造缺陷减少的超晶格的回蚀处理的更多细节可以在授予weeks等人的美国专利no.10,566,191和10,811,498中找到,这些专利已转让给本技术人并通过引用整体并入本文。

[0077]

在方框606处,基板121然后可以在期望的配量条件下稳定,并且如前所述硅表面用碳源(或用于碳-氧单层150b的碳-氧源)进行配量。如上所述,可以选择配量时间和温度,使得碳(或碳-氧)原子经历与硅表面下的交换,但保留在表面处的碳(或碳-氧)的密度不会高到阻止随后的外延硅生长。

[0078]

然后可以执行进一步的外延硅生长和回蚀(方框607-608)以生长覆盖层152或附加的基础半导体部分,这取决于有多少层组将被包括在超晶格120中(方框609)。图6的方法说明性地在块610处结束,但是此后可以执行附加的半导体处理步骤以制造各种类型的半导体器件,其示例将在下面进一步讨论。

[0079]

有多种方式可以使氧层和碳层交错。例如,氧源和碳源可以在碳-氧单层的相同脉冲期间配量硅层。根据另一个示例,可以首先是氧,然后是碳脉冲,或者反之亦然。如上所述,单层150a、150b之间的示例硅分离厚度可以在到的范围内,但是在一些实施例中可以使用其它厚度。

[0080]

作为示例,可以在100℃到1400℃的温度范围内,更特别地在300℃和900℃的温度范围内进行脉冲式配量碳结合。在低于600℃的温度下,共同流动的硅碳层将主要结合到替代位点上的硅晶格中。在高于600℃的温度下,mst膜中的一些碳将是替代的,一些将是间隙的,并且可能一些作为碳化硅沉淀物(在接近800℃的温度下)。在不同温度下每个状态的碳量取决于几个因素。例如,在600℃时,如果合金成分小于0.5原子百分比,那么可以将几乎所有的碳结合在替代晶格位点中。超过1原子百分比时,越来越多的碳部分将进入mst膜中在不是晶格点位的位置。不同的因素会影响碳的最终替代/间隙/沉淀状态,诸如膜生长速率、选择的源气体等。

[0081]

与标准的共同流动的硅碳外延相比,本文所述的脉冲式配量碳工艺给予工艺工程师更多的对碳结合的控制,因为碳主要首先结合在表面下位点中。对于传统的硅碳外延,为了获得大于或等于一个原子的替代碳,可以使用等于或低于550℃的生长温度,但是如此低的沉积温度可能具有挑战性。低温用于提供替代碳,但通常伴随着较低的生长速率和低的生长晶体质量。脉冲式碳沉积与蚀刻相结合有助于确保碳结合在晶格点位上,并且由于缺陷和沉淀物的蚀刻速度比无缺陷外延更快,因此该工艺可以消除缺陷和碳沉淀物。

[0082]

可以用于脉冲式配量碳沉积的示例气体源是丙烯(c3h6),又名丙烯或甲基乙烯。这是一种常温下呈液态的有机碳源,并且其蒸气压略高于sih2cl2(dcs)。这允许经由质量流量控制器(mfc)输送蒸汽,而无需起泡器。在丙烯工艺金属测试中,丙烯在530℃至800℃的温度范围内进行了测试,结果良好。更特别地,没有观察到丙烯沉积物导致腔室过度变色,基于30元素vpd-icp-ms测试也没有观察到任何金属污染。所有金属均低于测试的检测极限。

[0083]

对于图6中描述的工艺,循环各个步骤,直到实现超晶格120的所需厚度/配置。应当注意的是,在一些实施例中执行碳和氧配量步骤的顺序可以与所示顺序相反(例如,碳单层150b可以在超晶格120的底部),或者对于碳-氧单层进行共同配量。

[0084]

另外参考图7-11,参考二次离子质谱(sims)图170、180、190、200和x射线衍射(xrd)图210将进一步理解前述内容,例如用于制造半导体器件120的工艺流程。在sims图170中所示的示例中,使用1.1e15at/cm2的氧配量(16o)连同1.49e14at/cm2配量的碳。这导致器件中的碳含量为0.22原子百分比,这与异质结双极晶体管(hbt)技术用于掺杂剂阻挡的碳百分比兼容。使用上述工艺导致期望的硅晶体质量、原子排列没有明显的破坏以及横截面透射电子显微镜(x-tem)中氧和硅之间相对干净的质量对比。

[0085]

在sims图180中图示了不同的工艺运行,其中碳(12c)配量为4.27e17at/cm2(具有4.6e20at/cm3的峰)并且氧(16o)配量为1.16e15at/cm2。这种方法展示了0.96原子百分比的碳水平,这将与包括以下各项的应用兼容,例如:mosfet平面和3d体系架构,诸如finfet;掺

杂剂阻挡;应力源;以及微机电系统(mems)和基板应用,诸如用于硅上小晶格常数材料的蚀刻停止层和分级缓冲。关于在此类应用中实施mst膜的更多细节在美国专利公开no.2007/0020860;2007/0015344;2007/0007508;2007/0010040;2006/0292765;2006/0273299;以及美国专利no.7,531,828;7,586,165;7,598,515;7,202,494;10,580,867;10,854,717;和10,840,337中阐述,所有这些专栏都转让给本技术人并且在此通过引用整体并入本文。

[0086]

在sims图190中图示了又一个工艺运行,其中碳(12c)配量为6.97e14at/cm2(具有6.2e20at/cm3的峰)并且氧(16o)配量为1.16e15at/cm2。这导致膜的碳含量为1.2原子百分比,这可以有利于诸如例如应力源、蚀刻停止和掺杂剂阻挡之类的应用。

[0087]

在sims图200中图示了又一个工艺运行,其中碳(12c)配量为1.54e15at/cm2(具有6.75e20at/cm3的12c浓度)并且氧(16o)配量为2.16e15at/cm2。这个运行类似于图7中所示的运行,但没有外延硅帽且包括八个脉冲式生长循环。如图10中所见,实现了稳定的碳和氧配量浓度。此外,xrd图210中所示的x射线分析证实,图10中所示样品中的碳基于衍射光谱中所示的拉伸应变碳峰是替代的。同样对于该样品,傅立叶变换红外光谱(ftir)分析证实样品中的碳是替换的,并且因此导致拉伸应变的外延层。612cm-1

处的光谱峰表明碳在晶格位点与硅键合,而不是在碳化硅沉淀时在层中键合。

[0088]

许多半导体器件制造中的一个重要工艺步骤是进行蚀刻。在一些情况下,蚀刻的均匀性是重要的,但在其它情况下,期望蚀刻具有选择性,或在特定深度停止。一个示例是环绕栅极(gaa)器件的形成,其中通常会生长交替的硅(si)和硅锗(sige)的堆叠,使得在硅周围形成栅极之前,在该工艺的后期可以选择性地蚀刻sige以仅留下硅。在其它器件中,例如在某些图像传感器或rf器件中,期望去除感兴趣的器件下方的硅,或将硅蚀刻到特定深度。存在本领域技术人员熟悉的更多示例。

[0089]

典型的si/omst膜配方使得蚀刻速率与体硅非常相似。但是,与体硅相比,上述用于超晶格125的配方可以提供显著不同的蚀刻速率,使得该膜可以用于选择性蚀刻或蚀刻停止应用,如上所述。就此而言,将除氧之外的其它元素结合到膜中可以有利地促进实现可以用于指示给定蚀刻的终点的“信号”,如本领域技术人员将认识到的。

[0090]

在示例应用中,超晶格125可以用作高级逻辑应用的沟道材料(例如,在nmos的情况下),因为拉伸应变具有提高电子迁移率的效果。另一个应用包括例如用于凹陷的源极/漏极配置的应力源。这将涉及用诸如例如硼、砷或磷的掺杂剂来掺杂超晶格125。更特别地,超晶格125可以用作应力源衬里以防止诸如磷或砷之类的掺杂剂扩散到晶体管的沟道中。用超晶格125加衬凹陷具有掺杂剂阻挡的效果,对膜电阻率的影响最小。“衬里”或“加衬”是指超晶格125位于应力源凹陷的前几个单层内。

[0091]

此外,许多半导体器件制造中的重要工艺步骤是进行蚀刻。在一些情况下,蚀刻的均匀性是重要的,但在其它情况下,期望蚀刻具有选择性,或在特定深度停止。一个示例是环绕栅极(gaa)器件的形成(将在下面参考图16-17进一步讨论),其中通常会生长交替硅(si)和硅锗(sige)的堆叠,使得在硅周围形成栅极之前,在该工艺的后期可以选择性地蚀刻sige以仅留下硅。在其它器件中,例如在某些图像传感器或rf器件中,期望去除关注器件下方的硅,或将硅蚀刻到特定深度。存在本领域技术人员熟悉的更多示例。

[0092]

典型的mst硅配方使得蚀刻速率与常规硅非常相似。但是,与常规硅相比,本文所述的sic/sicomst膜配方可能具有显著不同的蚀刻速率,使得sic/sico膜可以用于选择性

蚀刻或蚀刻停止应用。还预计将其它元素结合到膜中可以有助于实现可以用于指示给定蚀刻的终点的“信号”。

[0093]

超晶格125的其它用途包括作为抗蚀刻材料用于诸如绝缘体上硅(soi)和mems的应用。更特别地,如果生长硅锗的外延层作为用于虚拟基板形成的抗蚀刻材料,那么可以添加超晶格125以补偿由于在外延层中添加大锗原子而导致的外延硅锗层中的压缩应变。添加碳可以帮助防止外延层在超过临界厚度后松弛。一旦外延层超过临界厚度,应变层就会松弛,从而在外延层中产生穿线和失配位错。超晶格125的另一个应用是用于应变soi的渐变缓冲层。超晶格125还可以提供异质结双极晶体管(hbt)中的掺杂剂阻挡以及增强的迁移率,如上文进一步讨论的。

[0094]

许多类型的半导体结构可以用上述氧和碳/碳-氧超晶格制造并从中受益。一种这样的器件是现在参考图12描述的平面mosfet 220。所示的mosfet 220包括基板221、源极/漏极区域222、223、源极/漏极延伸区226、227,以及它们之间由氧和碳/碳-氧超晶格225提供的沟道区域。沟道可以部分或完全在超晶格225内形成。源/漏硅化物层230、231和源/漏接触件232、233覆盖源/漏极区域,如本领域技术人员将认识到的。由虚线234a、234b指示的区域是最初由超晶格225形成但之后被重掺杂的可选残留部分。在其它实施例中,这些残留超晶格区域234a、234b可能不存在,如也由本领域技术人员所认识到的。栅极235说明性地包括与由超晶格225提供的沟道相邻的栅极绝缘层237,以及栅极绝缘层上的栅极电极层236。所示的mosfet 220中还提供了侧壁间隔物240、241。

[0095]

另外参见图13,根据其中可以结合氧和碳/碳-氧超晶格325的器件的另一个示例是半导体器件300,其中超晶格用作掺杂剂扩散阻挡超晶格以通过防止扩散到器件的沟道区域330中在原位掺杂外延处理期间有利地增加表面掺杂剂浓度以允许更高的nd(金属/半导体界面处的活性掺杂剂浓度)。更特别地,器件300说明性地包括半导体层或基板301,以及形成在半导体层中的间隔开的源极区域和漏极区域302、303(其中沟道区域330在其间延伸)。掺杂剂扩散阻挡超晶格325说明性地延伸穿过源极区域302以将源极区域划分成下源极区域304和上源极区域305,并且还延伸穿过漏极区域303以将漏极区域划分成下漏极区域306和上漏极区域307。

[0096]

掺杂剂扩散阻挡超晶格325在概念上也可以被认为是源极区域302内的源极掺杂剂阻挡超晶格、漏极区域303内的漏极掺杂剂阻挡超晶格和沟道330下方的体掺杂剂阻挡超晶格,但是在这种配置中,所有这三者都是通过mst材料作为连续膜在基板301上的单覆盖式沉积(single blanket deposition)来提供的。掺杂剂阻挡超晶格325上方的半导体材料(其中限定上源极/漏极区域305、307和沟道区域330)可以在掺杂剂阻挡超晶格325上外延生长,作为例如厚超晶格盖层或体半导体层。在所示示例中,上源极/漏极区域305、307可以各自与该半导体层的上表面齐平(即,它们被注入到该层内)。

[0097]

由此,上源极/漏极区域305、307可以有利地具有与下源极/漏极区域304、306相同的导电率,但具有更高的掺杂剂浓度。在所示示例中,上源/漏极区域305、307和下源/漏极区域304、306对于n沟道器件是n型的,但是对于p沟道器件,这些区域也可以是p型的。例如,可以通过离子注入引入表面掺杂剂。但是,扩散阻挡超晶格325的mst膜材料减少了掺杂剂扩散,因为它捕获了介导掺杂剂扩散的离子注入引入的点缺陷/间隙。

[0098]

半导体器件300还示例性地包括沟道区域330上的栅极308。该栅极说明性地包括

栅极绝缘层309栅极电极310。在所示示例中还提供了侧壁间隔物311。关于器件300以及其中可以使用氧和碳/碳-氧超晶格的其它类似结构的进一步细节在授予takeuchi等人的美国专利no.10,818,755中阐述,该专利已转让给本技术人并且在此通过引用整体并入本文。

[0099]

转向图14,现在描述其中可以使用氧和碳/碳-氧超晶格的半导体器件400的另一个示例实施例。更特别地,在所示示例中,源极和漏极掺杂剂扩散阻挡超晶格425s、425都经由异质外延膜集成有利地提供肖特基势垒高度调制。更特别地,下源极和漏极区域404、406包括与上源极和漏极区域405、407不同的材料。在这个示例中,下源极和漏极区域404、406是硅,并且上源极和漏极区域405、407是sigec,但是在不同的实施例中可以使用不同的材料。下金属层(ti)442、443形成在上源极和漏极区域(sigec层)405、407上。上金属层(co)444、445分别形成在下金属层442、443上。因为mst材料在集成异质外延半导体材料方面是有效的,因此将c(1-2%)结合到si或si上的sige可能引起正导带偏移。更特别地,这是对于降低肖特基势垒高度有效的sigec/mst/n+si结构。关于器件400的更多细节在上述'755专利中进行了阐述。

[0100]

参考图15,现在描述平面mosfet 500的示例实施例,其中具有氧和碳/碳/氧单层的超晶格525可以用作半导体(有源器件)层552的应力源。一般而言,电子和空穴在应变(双轴拉伸)硅中具有更高的迁移率。期望分别对于nmos和pmos器件在每个方向上优化应力极性。已经研究了用于提高nmos迁移率的硅帽/sige/硅基板结构,其中硅帽通过插入下面的sige层而被应力拉伸。在所示示例中,包括一个或多个碳/碳-氧单层的超晶格膜525而不是sige层可以有利地在硅覆盖层552中引起压缩应力。因为原子半径c《si《ge,所以这种配置也有利地适用于纵向方向上(即,在源极s和漏极d之间)的pmos器件。超晶格525可以相应地提供期望的应力极性以提高迁移率。在一些实施例中,上盖层552可以包括另一种或不同的半导体,诸如例如应变sige。此外,说明性地包括栅极电极536和栅极电介质537并且被侧壁间隔物540围绕的栅极535可以是以先栅或后栅配置形成的高k金属栅,如本领域技术人员将认识到的。

[0101]

另外参考图16,根据另一个示例实施例,现在描述结合了上述氧和碳/碳-氧超晶格膜625的堆叠纳米片gaa晶体管600。晶体管600说明性地包括其中具有浅沟槽隔离(sti)区域647的基板621。如图所示,限定晶体管沟道的半导体(例如,硅)纳米片646以垂直堆叠的形式布置并且被栅极氧化物637和栅极电极636包围。在所示实施例中,相应的氧和碳/碳-氧超晶格625形成在每个纳米片646的顶部和底部,以在其中提供期望的应力,如上文进一步讨论的。在图17中所示的gaa晶体管600'的替代实施例中,氧和碳/碳-氧超晶格625'替代地形成为更靠近纳米片646'的中间或中心。应该认识到的是,其它配置是可能的,其中超晶格625、625'位于每个纳米片646、646'的底部、中间和/或顶部,并且如果期望,那么配置可以从一个纳米片到下一个纳米片改变。

[0102]

还应该注意的是,在一些示例实施方式中,

28

si和/或

18

o材料也可以结合在上述氧和碳/碳-氧mst膜中,如共同待审的于2021年4月21日提交的美国申请序列no.17/236,329和17/236,289,以及于2021年5月26日提交的美国申请序列no.17/330,860和17/330,831中分别进一步描述的,所有这些申请都转让给本技术人并且通过引用整体并入本文。

[0103]

受益于前述描述和相关附图中呈现的教导,本领域技术人员将想到本发明的许多修改和其它实施例。因此,应该理解的是,本发明不限于所公开的具体实施例,并且修改和

实施例旨在被包括在所附权利要求的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1