结势垒二极管和肖特基二极管的形成以及MPS器件的制作方法

结势垒二极管和肖特基二极管的形成以及mps器件

技术领域

1.本公开涉及制造mps(合并式pin肖特基)器件的方法以及mps器件。具体地,将讨论基于sic的器件。

背景技术:

2.众所周知,具有宽带隙(特别是带隙的能量值eg大于1.1ev)、低通态电阻(r

on

)、高热导率值、高操作频率和电荷载流子的高饱和速度的半导体材料非常适合生产诸如(尤其是用于电源应用的)二极管或晶体管的电子部件。具有所述特性并且被设计为用于制造电子部件的材料是碳化硅(sic)。具体地,就前面列出的性质而言,碳化硅的不同多型(例如,3c-sic、4h-sic、6h-sic)优选于硅。

3.与在硅衬底上提供的类似器件相比,在碳化硅衬底上提供的电子器件具有许多优点,诸如低导通输出电阻(output resistance in conduction)、低漏电流、高工作温度和高操作频率。具体地,sic肖特基二极管表现出更高的切换性能,使得sic电子器件特别适合高频应用。当前的应用对器件的电性质以及长期可靠性提出了要求。

技术实现要素:

4.本公开提供了电子器件和制造电子器件的方法。

附图说明

5.为了更好地理解本公开,现在参考附图、仅通过非限制性示例的方式来描述其优选实施例,在附图中:

6.图1以截面图形式示出了根据已知实施例的mps器件;

7.图2a和图2b以截面图形式示出了根据现有技术的图1的mps器件的中间制造步骤;以及

8.图3a-图3c以截面图形式示出了根据现有技术的在图2a和图2b的步骤之后用于在图1的mps器件中形成欧姆接触的步骤;

9.图4以平面图形式图示了根据现有技术的由于图3a-图3b的制造步骤而形成的不希望的区域;

10.图5以截面图形式示出了根据本公开的一个实施例的mps器件;

11.图6a-图6d以截面图形式图示了根据本公开的图5的mps器件的制造步骤;以及

12.图7a-图7d图示了形成mos2半导体层的步骤,其可用于图6d的制造步骤的上下文中。

具体实施方式

13.本公开将参考基于sic的合并式pin肖特基mps器件进行描述;然而,如从以下描述中显而易见的,本公开通常应用于基于不同类型的半导体(例如,gan)的mps器件。

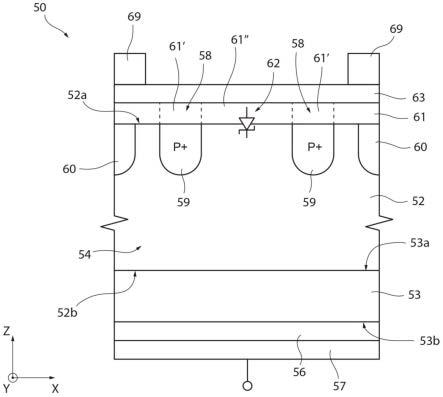

14.图1以x、y、z轴的笛卡尔(三轴)参考系的横向截面图形式示出了mps器件1。

15.mps器件1包括:由n型sic形成的衬底3,具有第一掺杂浓度,被提供有与表面3b相对的表面3a,并且厚度等于大约350μm;由n型sic形成的漂移层(以外延方式生长)2,具有低于第一掺杂浓度的第二掺杂浓度、在衬底3的表面3a上延伸,并且厚度在5-10μm范围内;欧姆接触区域6(例如由硅化镍形成),在衬底3的表面3b上延伸;阴极金属化部16,在欧姆接触区域6上延伸;阳极金属化部8,在漂移层2的顶表面2a上延伸;漂移层2中的多个结势垒(jb)元件9,面向漂移层2的顶表面2a,并且各自包括相应的p型注入区域9'和金属材料的欧姆接触部9”;以及边缘终止区域或保护环10(可选),例如完全围绕结势垒(jb)元件9的p型注入区域。

16.肖特基二极管12形成在漂移层2和阳极金属化部8之间的界面处。在一些实施例中,肖特基(半导体-金属)结由漂移层2中与阳极金属化部8的相应部分直接电接触的部分形成。

17.mps器件1中包括jb元件9和肖特基二极管12的区域(即,保护环10内包含的区域)是mps器件1的有源区4。

18.参考图2a和图2b,图1的mps器件1的制造步骤提供(图2a)被掩蔽的注入具有第二导电类型(p)的掺杂物质(例如,硼或铝)的步骤。注入物在图2a中用箭头18图示。掩模11,例如由氧化硅或teos形成的硬掩模用于进行注入。由此形成注入区域9'和边缘终止区域10。然后,在图2b中,掩模11被去除并且被执行热退火步骤来激活在图2a的步骤中注入的掺杂物质。热退火例如在高于1600℃(例如,在1700-1900℃范围内并且在某些情况下甚至更高)的温度下执行。

19.参考图3a-图3c,接下来执行进一步的步骤来形成欧姆接触部9”。参考图3a,由氧化硅或teos形成的沉积掩模13,以覆盖漂移层2中除注入区域9'之外的表面区域(以及边缘终止区域10,如果存在的话)。换言之,掩模13在注入区域9'处(并且可选地在边缘终止区域10的至少一部分处)具有贯通开口13a。接下来,在图3b,在掩模13上和贯通开口13a(图3b中的金属层14)内部执行镍沉积。如此沉积的镍通过贯通开口13a到达并接触注入区域9'和边缘终止区域10。

20.参考图3c,随后的高温热退火(快速热处理,在900℃-1050℃范围内持续1分钟至120分钟的时间区间)允许硅化镍的欧姆接触部9”通过经沉积的镍和漂移层2的硅在贯通开口13a处的化学反应而形成。事实上,经沉积的镍在与漂移层2的表面材料接触的位置发生反应而形成ni2si(即,欧姆接触)。随后,执行去除在掩模13之上延伸的金属的步骤并去除掩模13。

21.发明人已证实,如图4作为示例所示,尽管是有限的,但在金属层14的镍和它们直接接触的掩模13之间仍然发生反应。图4是图3b的器件的一部分的xy平面俯视图,在此,该区域由虚线界定,并且在图3b中以附图标记15标识。图4涉及图3b和图3c之间的中间制造步骤,即,掩模13仍然存在,但镍层14被去除。如图4所示,不规则区域或岛17在掩模13上延伸,并且不规则区域或岛17是由于掩模13的镍和硅之间的不希望的反应。发明人还注意到,类似的锯齿状或齿状区域在掩模13下方延伸,即,在漂移层2的表面2a上延伸。在图4中,这些锯齿状或齿状区域以附图标记16标识,并且由导电材料(包括镍)形成。如果这些锯齿状或齿状区域16在xy平面上的延伸(例如沿x轴的延伸)大于注入区域9'的对应延伸,则将存在

会导致器件故障的短路。具体而言,如果不希望的导电区域延伸到专用于肖特基接触的区域中,则会在n型区域上形成欧姆或准欧姆接触(具有低势垒的肖特基接触)(从电观点来看,是阻力);因此,在正向和反向偏置中都会有连续的电流流动,从而失去了二极管的特性。

22.图5以轴x、y、z的笛卡尔(三轴)参考系中的横向截面图的方式示出了根据本公开的一个方面的合并式pin肖特基(mps)器件50。

23.mps器件50包括宽带隙半导体材料的衬底53。在一些实施例中,衬底53包括n型sic,例如4h-sic,具有第一n+掺杂浓度,被提供有与表面53b相对的表面53a,并且厚度在50μm-350μm的范围内,并且在一些实施例中,在160μm-200μm的范围内,并且在一些其他实施例中,等于180μm。在一些实施例中,衬底53可以由gan形成。

24.由n型sic(替代地,gan)形成的(外延生长的)漂移层52具有低于第一掺杂浓度的第二n掺杂浓度,在衬底53的表面53a上延伸,并且具有在5-15μm范围内的厚度。例如由硅化镍形成的欧姆接触部56的区域或层在衬底53的表面53b上延伸。例如ti/niv/ag或ti/niv/au的底部金属化部57在欧姆接触部56的区域上延伸。

25.一个或多个p型掺杂区域59,以下称为“结势垒元件”或“jb元件”,在漂移层52内部面向或邻近漂移层52的顶表面52a而延伸。附图以非限制性示例的方式示出了两个jb区域59。如所提到的,每个jb元件59是p型注入区域,在一些实施例中,是p+型注入区域。每个jb元件具有例如高于1

·

10

18

原子/cm3的掺杂浓度。

26.在一些实施例中,边缘终止区域或保护环60(可选)是在外部界定器件或围绕器件的有源区的p型(p+)的注入区域。

27.根据本公开的一个方面,由例如mos2(硫化钼,也称为辉钼矿,或二硫化钼)形成的半导体层61在漂移层52的顶表面52a上延伸。半导体层61与jb元件59电接触(例如,与p+注入区域59直接接触)并且与n型漂移层52的顶表面52a中与jb元件59水平的各部分电接触。

28.通常,层61由属于过渡金属硫属化物组的材料形成,在一些实施例中,二硫属化物被称为“过渡金属二硫属化物(transition metal dichalcogenides)”或“tmd”,具有半导体特性。tmd是具有化学式mx2的材料,其中m是第4-10族的过渡金属(例如,mo、w、nb、ta等),并且x是硫属元素(例如,s、se、te)。除了前述的mos2之外,非限制性列表还包括mose2、mote2、ws2、wse2、wte2、nbs2。这些材料具有典型的层状结构,即,这些材料由通过弱范德华键相互键合的不同结晶层堆叠而形成。根据化学式mx2,每个结晶层由过渡金属原子与硫属元素原子键合而形成,具有强共价键。单层的对称性是六边形或菱面体,其中原子排列成八面体或三角棱柱配位。半导体tmd薄膜(诸如mos2)的一个特殊特性是带隙宽度和功函数取决于构成堆叠的厚度(即,层数)。例如,由单个mos2层(厚度为0.65nm)制成的薄膜具有1.8-1.9ev的“直接”带隙,而由两个或更多个mos2层制成的膜具有1.2ev的“间接”带隙。

29.此外,根据本公开的一个方面,半导体层61的材料基于衬底53和外延层52的材料来选择。在一些实施例中,半导体层61的材料使得其与形成其的外延层52的材料具有良好的晶格匹配。例如,发明人已证实,在由sic或gan形成的衬底或外延层上使用mos2满足了该要求。

30.顶部金属化部63在半导体层61上延伸,并且与半导体层61电接触,例如与半导体层61直接电接触。

31.钝化层69在顶部金属化部63上延伸而至少部分地保护后者。钝化层69具有使顶部金属化部63通过钝化层69而暴露的至少一个开口,以使得能够从外部例如通过引线键合或其他技术与顶部金属化部63电接触,以在使用期间将器件偏置。

32.根据本公开的一个方面,为了在每个jb元件59处形成欧姆接触,并且例如在n型漂移层52的表面区域处与jb元件59横向地形成肖特基接触,半导体层61被选择性地掺杂来选择性地改变其导电性。在这点上,半导体层61在相应jb元件59处或其附近具有p型导电性的区域61',并且在具有n型导电性的漂移层52的表面部分处具有n型导电性的区域61”,这形成相应的肖特基二极管62。

33.沿着x轴方向,区域61'和区域61”彼此交替。此外,每个区域61'沿x与至少一个相应区域61”相邻。

34.p型的每个区域61'例如沿z轴竖直延伸,贯穿半导体层61的厚度,以与相应的jb元件电接触,其中它(至少部分地)垂直对准。类似地,每个区域61”例如沿z轴竖直延伸,贯穿半导体层61的厚度,以与n型层52的相应表面区域电接触。

35.每个区域61'与和其电接触的相应jb元件形成相应的结势垒二极管58;类似地,每个区域61”与和其电接触的层52的相应表面部分形成相应的肖特基二极管62。

36.mps器件50中包括jb二极管58和肖特基二极管62的区域,例如保护环60内包含的区域,是mps器件50的有源区。

37.发明人已证实,mos2材料的功函数可以通过mos2的合适功能化(例如,用于修改mos2的导电性质(n型或p型)的功能化)来改变或修改或调整。此外,作为上述内容的替代或附加,mos2材料的功函数可以通过选择合适数目的叠加的mos2层来改变或修改或调整。例如,在本公开的上下文中,“半导体层61”可以是单个mos2层,例如具有二维结构的单层,或例如具有三维结构的mos2多层。

38.例如,mos2多层的功函数可以通过氧(o2)的适当掺杂来例如在4.4ev和5.6ev之间调整,这用于生成p型导电性的唯一掺杂区域。

39.作为其他示例,单个mos2层的功函数可以通过氧(o2)的适当掺杂来例如在4.1ev和6ev之间调整,这用于生成p型导电性的唯一掺杂区域。

40.在本公开的上下文中,术语“半导体层61”包括多层和单层。

41.通过选择性地改变mos2层61的导电性和/或制造其(多层或单层)的子层的数目,mos2层61的势垒因此可以被修改。

42.例如,在n型掺杂mos2的情况下,与n型4h-sic衬底形成肖特基接触,势垒高度在多层情况下约为1.3ev,并且在单层情况下约为1ev。

43.例如,在p型掺杂mos2的情况下,与n型4h-sic衬底中的p+注入区域形成欧姆接触,势垒高度在多层情况下约为0.6ev,并且在单层情况下约为0.2ev。

44.参考图6a-图6d来描述mps器件50的制造步骤。

45.参考图6a,布置了晶片100,晶片100包括由sic形成的衬底53,例如4h-sic,然而,可以使用其他多型体。如上所述,也可以使用其他材料,例如gan。

46.衬底53具有第一类型的导电性,在一些示例实施例中为n型掺杂剂,并且被提供有沿z轴彼此相对的前表面53a和后表面53b。衬底53具有例如1

·

10

19-1

·

10

20

原子/cm3范围内的n+掺杂浓度。

47.晶片100的前侧对应于前表面53a,并且晶片100的背侧对应于后表面53b。

48.由碳化硅形成的漂移层52具有导电性n,并且其n-掺杂浓度低于衬底53的浓度,例如在1

·

10

14-5

·

10

16

原子/cm3的范围内,其例如通过在衬底53的前表面53a上外延生长而形成。漂移层52由sic制成,例如4h-sic,但也可以使用其他sic多型或替代地,可以使用gan。

49.漂移层52在其厚度上在顶侧52a和底侧52b之间延伸,底侧52b与衬底53的前表面53a直接接触。

50.然后,图6b,硬掩模70例如通过沉积光致抗蚀剂或四乙氧基硅烷(teos)或适合该目的的其他材料在漂移层52的顶侧52a上形成。硬掩模70具有0.5μm-2μm范围内的厚度,或者在任何情况下具有使其遮蔽下文参考相同的图6b描述的注入物的厚度。硬掩模70延伸到晶片100的区域中,其中在随后的步骤中,将形成mps器件50的有源区54。

51.在平面图中,已参考图5描述了硬掩模70在xy平面上覆盖漂移层52的顶侧52a中将形成肖特基单元(二极管62)的区域,并且使得漂移层52中将形成注入区域59的顶侧52a的区域暴露。

52.然后利用硬掩模70来执行注入掺杂物质(例如硼或铝)的步骤,该掺杂物质具有第二类型的导电性,此处为例如p型(注入物在图中由箭头72指示)。在图6b的步骤期间,也形成保护环60(如果存在的话)。

53.在一个示例实施例中,图6b的注入步骤包括掺杂物质的一次或多次注入,掺杂物质具有第二类型的导电性,注入能量在30kev-400kev范围内,并且剂量在1

·

10

12

原子/cm

2-1

·

10

15

原子/cm2的范围内,以形成掺杂浓度大于1

·

10

18

原子/cm3的注入区域59。由此形成的注入区域具有从表面52a测量的在0.4μm-1μm范围内的深度。

54.随后,图6c,掩模70被去除,并且,图6d,例如由mos2形成的半导体层61被形成。

55.现在描述用于形成半导体层61的示例过程,其通过在外延层52上cvd(“化学气相沉积”)沉积mos2而形成,在该示例中外延层52是sic。参考图7a-7c描述了该过程,其中示意性地图示了双区反应器90,其包括石英管状体,并且由可以彼此独立加热的两个区域90a、90b形成。

56.参考图7a,硫(s)和钼(mo,或moo

x

,例如,其中x=3)被用作用于生长mos2的前体。硫前体(例如,以粉末的形式)被布置在区域90a中的坩埚92中,与将在其上执行mos2生长的晶片相距一定距离(在约7-15cm的距离处)。钼前体(例如,也以粉末的形式)被布置在区域90b中的相应坩埚93中,靠近将在其上执行mos2生长的晶片100(即,在晶片100和硫坩埚之间的区域90b中)。

57.参考图7b,区域90a被加热到100-200℃范围内的温度t1,例如150-160℃范围内的温度,导致沉积在晶片100上的硫蒸发。区域90b被加热到高于温度t1的温度t2(因此在700-800℃的范围内),导致沉积在晶片100上的钼蒸发。

58.该过程在存在载流子气体的情况下发生,载流子气体以图7a-图7c中的箭头91指示的方向被引入反应器90中。气体例如是以大约100sccm引入的氩气(ar)。气体的方向使得硫和钼蒸气被推向晶片100。

59.在晶片100的层级,图7c,硫和钼沉积在其上,通过化学反应形成mos2层61。

60.在硫和钼蒸气在晶片100上的反应期间形成的mos2亚层(单层或多层)的数目可以通过调节以下一项或多项来控制:温度t2、生长过程的持续时间以及硫蒸气的流量(通过调

节载流子气体的流量)。

61.替代地或附加地,mos2多层可以被沉积,并且接下来可以通过蚀刻技术而选择性地去除一个或多个层,直至将该多层减少为单个层/单层。

62.坩埚92、93和晶片100在反应器90中的其他相对布置是可能的。例如,图7d,坩埚93可以被布置在晶片100下方。在这种情况下,晶片100被定向为使得顶面(将在其上形成层61)朝向坩埚93。

63.在本公开的上下文中可以使用其他技术或方法来形成半导体层61。这样的方法(文献中已知)均为自下而上和自上而下的类型,并且包括:原子层沉积(ald)、脉冲激光沉积(pld)、溅射。

64.如此形成的半导体层61在没有进一步掺杂的情况下示出n型导电性,这在待进一步调整多数导电物质的浓度的情况下仍然是可能的。

65.返回到图6d,在半导体层61中需要被功能化的区域处具有开口80a的掩模80(例如光致抗蚀剂)形成在半导体层61,以改变其导电性。半导体层61的表面区域61a通过光致抗蚀剂中的开口80a暴露。这些开口80a(沿z轴,或在xy平面俯视图中)与相应的jb元件59至少部分地对准。

66.被提供有掩模80的晶片100被布置在反应器中,在反应器中生成用于半导体层61的功能化的氧等离子体。氧与通过开口80a暴露的半导体层61的材料反应,提供选择性p型掺杂。参考图5描述的掺杂区域61'(p型)并且根据上下文(contextually),区域61”(n型)由此形成。

67.用于形成p型区域61'的mos2的功能化例如通过等离子体处理发生,并且可以使用各种化学物质(包括o2、chf3、cf4和sf6)来执行。

68.被掩模80覆盖的半导体层61的区域61”的导电性不会被通过o2的功能化步骤改变;因此这些区域保持n型导电性。

69.然后掩模80可以被去除。

70.接下来制造步骤以图中未图示的方式进行,以本身已知的方式形成顶部金属化部和钝化层,并且因此在图中未进一步描述或图示。在晶片背侧上形成欧姆接触以及形成底部金属化部本身也是已知的,并且因此不再进一步描述。

71.通过检查根据本说明书提供的本公开的特征,其提供的优点是显而易见的。

72.在一些实施例中,sic mps二极管的“ifsm耐用性”值被最大化,制造流程被简化,并且参考现有技术描述的与突起或镍残留物相关的问题被避免和克服。

73.最后,很明显,可以对本文中描述和图示的内容进行修改和改变,而不偏离如所附权利要求中限定的本公开的范围。

74.一种制造合并式pin肖特基mps器件(50)的方法可以被概括为包括以下步骤:在具有第一导电性(n)的固体(52、53)的前侧(52a)处注入掺杂物质,掺杂物质具有与第一导电性(n)相对的第二导电性(p),从而形成从前侧(52a)延伸到固体中的注入区域(59);在前侧(52a)上形成半导体层(61),半导体层(61)的材料是具有第一导电性(n)的过渡金属二硫属化物tmd;通过化学物质来将半导体层(61)的第一区域(61')选择性地功能化,以在所述第一区域中生成第二导电性(p),所述第一区域与注入区域(59)电接触,并且与半导体层(61)的具有第一导电性(n)的第二区域相邻,第二区域与具有第一导电性(n)的前侧(52a)的相

应表面部分电接触。

75.第一区域(61')可以贯穿半导体层(61)的厚度而延伸,至少部分地在注入区域(59)处到达固体(52、53)的前侧(52a)。

76.将第一区域(61')功能化可以包括在固体(52、53)和注入区域(59)之间的界面处形成欧姆接触。

77.形成欧姆接触可以包括形成结势垒jb二极管。

78.形成半导体层(61)的步骤可以包括在第二区域(61”)和固体之间的界面处横向于注入区域(59)而形成肖特基二极管。

79.固体(52、53)的材料可以是以下材料之一:sic、4h-sic、gan、aln、金刚石、ga2o3。

80.半导体层(61)的材料可以是mos2、mose2、mote2、ws2、wse2、wte2中的一种。

81.方法还可以包括以下步骤:在半导体层(61)上形成与所述jb二极管和所述肖特基二极管共用的第一电端子,第一电端子包括第一金属层;以及在与固体的前侧(52a)相对的背侧(53b)处形成所述jb二极管和所述肖特基二极管共用的第二电端子(57),,第二电端子包括第二金属层。

82.方法还可以包括以下步骤:布置衬底(53);在衬底(53)上外延生长形成mps器件(50)的漂移层的外延层(52),其中衬底(53)和外延层(52)一起形成所述固体。

83.形成半导体层(61)的步骤可以包括执行cvd生长工艺,或ald工艺,或溅射工艺,或pld工艺。

84.第一导电性可以是n型,第二导电性可以是p型,并且将第一区域(61')功能化的步骤可以包括通过o2掺杂第一区域(61')。

85.合并式pin肖特基mps器件(50)可以被概括为包括:固体(52、53),具有第一导电性(n);注入区域(59),延伸到固体(52、53)中,面向固体(52、53)的前侧(52a)而具有与第一导电性(n)相对的第二导电性(p);以及半导体层(61),其在前侧(52a)上延伸,由过渡金属二硫属化物tmd材料形成,其中半导体层(61)的第一区域(61')具有第二导电性(p),并且与注入区域(59)电接触地延伸,并且半导体层(61)的第二区域(61”)具有第一导电性(n),并且邻近第一区域(61')延伸,并且与具有第一导电性(n)的前侧(52a)的相应表面部分电接触。

86.第一区域(61')可以穿过半导体层(61)的厚度而延伸,至少部分地在注入区域(59)处到达固体(52、53)的前侧(52a)。

87.第一区域(61')可以与注入区域(59)形成欧姆接触。

88.在第一区域(61')处,半导体层(61)可以与注入区域(59)一起形成结势垒jb二极管。

89.在第二区域(61”)处,半导体层(61)可以与固体(52、53)一起形成肖特基二极管。

90.固体(52、53)的材料可以是以下材料之一:sic、4h-sic、gan、aln、金刚石、ga2o3。

91.半导体层(61)的材料可以是mos2、mose2、mote2、ws2、wse2、wte2中的一种材料。

92.器件还可以包括所述jb二极管和所述肖特基二极管共用的第一电端子,可以包括在半导体层(61)上的第一金属层;以及所述jb二极管和所述肖特基二极管共用的第二电端子(57),可以包括位于与固体的前侧(52a)相对的背侧(53b)处的第二金属层。

93.固体可以包括衬底(53);以及在衬底(53)上的外延层(52),其中外延层(52)可以是mps器件(50)的漂移层。

94.第一导电性可以是n型,并且第二导电性可以是p型。

95.上述各种实施例可以被组合来提供进一步的实施例。如果需要,实施例的各方面可以被修改为采用各种实施例的构思来提供更进一步的实施例。

96.可以根据以上详细描述对实施例进行这些和其他改变。一般而言,在所附权利要求中,所使用的术语不应被解释为将权利要求限制于在说明书和权利要求中公开的具体实施例,而应被解释为包括所有可能的实施例以及这样的实施例所要求保护的等同物的全部范围。因此,权利要求不受本公开内容的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1