一种集成PMOS自适应控制SOILIGBT

一种集成pmos自适应控制soi ligbt

技术领域

1.本发明属于功率半导体技术领域,涉及一种集成pmos自适应控制soi ligbt(lateral insulated gate bipolar transistor,横向绝缘栅双极型晶体管)。

背景技术:

2.传统的ligbt在正向导通时电导调制的过程会有利于降低正向导通压降(on-state voltage drop,v

on

),但同时在器件关断过程中,大量的过剩载流子需要消除会产生较长的拖尾电流,大大增加了关断损耗(turning off energy loss,e

off

)。

3.为了改善ligbt器件导通压降与关断损耗的折中关系,通常的方法是引入阳极短路结构,这样在器件关断时引入了一条抽取电子的通路,加快了过剩载流子的消除,降低了关断损耗,但阳极短路结构导致器件在导通时载流子单极导电模式向双极导电模式转换所造成的电压折回snapback效应,降低了器件并联使用的可靠性。

技术实现要素:

4.本发明的目的,就是针对上述一些问题,提出一种集成pmos自适应控制soi ligbt。

5.本发明的技术方案是:一种集成pmos自适应控制soi ligbt,包括沿器件垂直方向自下而上依次层叠设置的p衬底1、埋氧层2和顶部半导体层;所述的顶部半导体层沿器件横向方向依次包括阴极结构、栅极结构、n型漂移区3、阳极结构与集成pmos结构;

6.所述阴极结构位于顶部半导体层上层一端,包括p阱区4、p+体接触区5、n+阴极区6与导电材料81;所述p+体接触区5和n+阴极区6相互接触,并列位于p阱区4内上表面远离型n型漂移区3的一端,且n+阴极区6在靠近n型漂移区3的一侧,p+体接触区5在远离n型漂移区3的一侧,p+体接触区5和n+阴极区6上表面共同引出导电材料81为阴极电极;

7.所述主栅极结构由栅介质层71与栅电极82共同构成;

8.所述阳极结构包括n型缓冲层9、p+阳极区10和n+阳极区11;所述p+阳极区10和n+阳极区11并列位于n型缓冲层9内上表面,且p+阳极区10位于靠近n型漂移区3的一侧,n+阳极区11位于远离n型漂移区3的一侧,p+阳极区10上表面的的导电材料84引出为阳极电极;

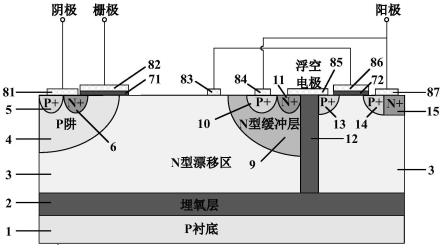

9.其特征在于,所述集成pmos结构与阳极结构之间设有介质隔离槽12,且介质隔离槽12从器件表面沿垂直方向向下贯穿n型漂移区3与埋氧层2接触;所述集成pmos结构包括p+漏区13、p+源区14、n+体接触区15、平面栅结构、栅控金属电极83与浮空复合电极85;所述p+漏区13位于集成pmos结构内上表面靠近阳极结构的一端,所述p+源区14与n+体接触区15相互接触,并列位于集成pmos结构内上表面远离阳极结构的一端;所述平面栅结构包括平面栅氧化层72及其上表面的导电材料86,所述平面栅氧化层72位于p+漏区13与源区14之间n型漂移区3的上方,且两端分别与p+漏区13和p+源区14部分交叠;所述栅控金属电极83位于栅极结构和阳极结构之间的n型漂移区3上表面,且与导电材料86短接,所述浮空复合电极85位于介质隔离槽12上表面且与n+阳极区11和p+漏区13上表面接触,所述p+源区14与n+

体接触区15共同引出导电材料87且与阳极电极短接;

10.进一步的,所述ligbt主栅结构为平面栅,所述平面栅由栅介质层71及位于其上表面的导电材料82构成,所述栅介质层71位于p阱区4上表面且两端分别与n型漂移区3和n+阴极区6部分交叠;

11.进一步的,所述ligbt主栅结构为槽栅,所述槽栅由栅介质层71及填充在的凹槽中的导电材料82构成,所述槽栅远离漂移区的一侧的侧壁从上至下依次与n+阴极区6及p阱区4接触,且槽栅深度超过p阱区4深度。

12.本发明的有益效果为,相对于传统的阳极短路ligbt结构,本发明在正向导通初期,pmos自适应关断,器件无snapback现象;在关断过程中,集成pmos自适应开启,加速电子的抽取,减少器件的关断损耗;在正向阻断时,集成pmos自适应开启,抑制了阳极pnp三极管的开启,使器件由双极击穿转换为单极击穿模式,从而提高器件的耐压。

附图说明

13.图1为实施例1的结构示意图;

14.图2为实施例2的结构示意图;

具体实施方式

15.下面结合附图和实施例,详细描述本发明的技术方案:

16.实施例1

17.如图1所示,本例的结构为一种集成pmos自适应控制soi ligbt,包括沿器件垂直方向自下而上依次层叠设置的p衬底1、埋氧层2和顶部半导体层;所述的顶部半导体层沿器件横向方向依次包括阴极结构、栅极结构、n型漂移区3、阳极结构与集成pmos结构;

18.所述阴极结构位于顶部半导体层上层一端,包括p阱区4、p+体接触区5、n+阴极区6与导电材料81;所述p+体接触区5和n+阴极区6相互接触,并列位于p阱区4内上表面远离型n型漂移区3的一端,且n+阴极区6在靠近n型漂移区3的一侧,p+体接触区5在远离n型漂移区3的一侧,p+体接触区5和n+阴极区6上表面共同引出导电材料81为阴极电极;

19.所述平面栅由栅介质层71及位于其上表面的栅电极82构成,所述栅介质层71位于p阱区4上表面且两端分别与n型漂移区3和n+阴极区6部分交叠;

20.所述阳极结构包括n型缓冲层9、p+阳极区10和n+阳极区11;所述p+阳极区10和n+阳极区11并列位于n型缓冲层9内上表面,且p+阳极区10位于靠近n型漂移区3的一侧,n+阳极区11位于远离n型漂移区3的一侧,p+阳极区10上表面的的导电材料84引出为阳极电极;

21.其特征在于,所述集成pmos结构与阳极结构之间设有介质隔离槽12,且介质隔离槽12从器件表面沿垂直方向向下贯穿n型漂移区3与埋氧层2接触;所述集成pmos结构包括p+漏区13、p+源区14、n+体接触区15、平面栅结构、栅控金属电极83与浮空复合电极85;所述p+漏区13位于集成pmos结构内上表面靠近阳极结构的一端,所述p+源区14与n+体接触区15相互接触,并列位于集成pmos结构内上表面远离阳极结构的一端;所述平面栅结构包括平面栅氧化层72及其上表面的导电材料86,所述平面栅氧化层72位于p+漏区13与源区14之间n型漂移区3的上方,且两端分别与p+漏区13和p+源区14部分交叠;所述栅控金属电极83位于栅极结构和阳极结构之间的n型漂移区3上表面,且与导电材料86短接,所述浮空复合电

极85位于介质隔离槽12上表面且与n+阳极区11和p+漏区13上表面接触,所述p+源区14与n+体接触区15共同引出导电材料87且与阳极电极短接。

22.本例的工作原理为:

23.新器件在正向导通随着阳极电压增大时,集成pmos栅源之间压差为零而处于关断状态,阳极p+/n-buffer结开启器件直接进入双极模式,有效避免了snapback现象;在器件的关断过程中,随着阳极电压的增大,耗尽区由主结扩展至耗尽线经过栅控金属电极位置,由于电压降落在耗尽区上,此时集成pmos栅源之间压差超过其阈值电压,pmos自适应开启,从而关断过程中pmos导通产生的空穴将与漂移区内的电子通过复合电极进行复合消除,加速了电子的抽取速度,降低了拖尾电流,有效的降低了关断损耗;在器件的正向阻断过程中,同样的由于耗尽区的扩展pmos自适应开启,从而抑制了阳极p+/n-buffer结的开启,从而有效的降低了耐压时的空穴泄露电流,使器件由双极击穿转换为单极击穿模式,因此获得高耐压特性。

24.本发明的有益效果为,相对于传统的阳极短路ligbt结构,本发明在较小的阳极电压导通时直接进入双极模式,器件无snapback现象;在关断过程中和正向阻断时集成pmos自适应开启,从而减少了器件的关断损耗及增加了器件的耐压。

25.实施例2

26.如图2所示,本例与实施例1中图1的区别在于,本例中ligbt主栅结构是槽栅。相比于实施例1,槽栅可阻挡空穴抽取,增加漂移区空穴浓度,从而进一步增强电导调制能力,减小正向导通压降。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1