气密性晶圆级芯片封装结构及模组、电路板和电子设备的制作方法

1.本实用新型涉及一种气密性晶圆级芯片封装结构,同时也涉及一种包含该气密性晶圆级芯片封装结构的模组、电路板和电子设备,属于芯片封装技术领域。

背景技术:

2.随着微电子技术的不断演进,芯片小型化和高集成度的需求越来越迫切,因此声学滤波器的微小化在诸如射频前端模组(rf fem)的集成度高的模组、电路板或电子设备中,变得尤为重要。

3.声学滤波器按照结构不同,可以分为声表面波滤波器(简写为saw滤波器)和体表面波滤波器(简写为baw滤波器),其基本原理大致相同,只是声学信号传播方向存在差异。saw滤波器的基本原理是在输入端由压电效应把无线信号转换为声信号在介质表面传播,在输出端由逆压电效应将声信号转换为无线信号。baw滤波器的基本原理与saw滤波器相同,不同的是baw滤波器的声波是垂直传播。因此,两者均需要空腔结构以保护叉指换能器(idt)。

4.在专利号为zl 201721882163.2的中国实用新型中,公开了一种声表面波器件气密性晶圆级封装结构,在功能芯片工作面的外围镀有一圈键合层金属,封盖晶圆上与每块芯片键合层金属对应位置分别镀有一圈键合层金属,功能芯片与封盖晶圆通过金-金键合或者共晶键合对应结合在一起;在封盖晶圆背向功能芯片工作面那面设有外部电路布线结构和外电极;在外电极上制作有外部焊球;封盖晶圆上设有导通孔以将功能芯片工作面电路依次通过导通孔、外部电极和外部焊球电连接。该实用新型能够实现高芯片剪切强度、散热性好、封装内部气氛可控的晶圆级(wlp)声表面波器件的气密性封装,具有可靠性高的特点。

技术实现要素:

5.本实用新型所要解决的首要技术问题在于提供一种气密性晶圆级芯片封装结构。

6.本实用新型所要解决的另一技术问题在于提供一种包含上述气密性晶圆级芯片封装结构的模组。

7.本实用新型所要解决的又一技术问题在于提供一种包含上述气密性晶圆级芯片封装结构的电路板。

8.本实用新型所要解决的再一技术问题在于提供一种包含上述气密性晶圆级芯片封装结构的电子设备。

9.为了实现上述目的,本实用新型采用以下的技术方案:

10.根据本实用新型实施例的第一方面,提供一种气密性晶圆级芯片封装结构,包括:芯片体,具有电极面以及与电极面相对的安装面,具有贯穿电极面和安装面的导电通孔,所述安装面上有导电盘,多个电极,位于所述电极面上,并且通过所述导电通孔与所述导电盘电连接,连接器,位于所述电极面上,围合所述多个电极并形成空腔;封盖,覆盖所述连接器

以及所述空腔,使得所述封盖、所述连接器和所述芯片体共同封闭所述空腔。

11.其中较优地,所述电极面上还设有金属的导电垫片,连接所述电极和所述导电通孔。

12.其中较优地,所述连接器是一层环形结构,由导电层形成或由干膜经热压形成。

13.其中较优地,所述连接器是两层环形结构,包括芯片体上金属层、封盖上金属层,

14.所述芯片体上金属层与封盖上金属层键合连接,形成气密性挡墙。

15.其中较优地,所述连接器是三层环形结构,包括芯片体上金属层、封盖上金属层,以及接合层,所述接合层位于所述芯片体上金属层和封盖上金属层之间。

16.其中较优地,所述接合层与所述芯片体上金属层及所述封盖上金属层键合连接,形成气密性挡墙。

17.根据本实用新型实施例的第二方面,提供一种包含气密性晶圆级芯片封装结构的模组,所述气密性晶圆级芯片封装结构是如前述的气密性晶圆级芯片封装结构。

18.根据本实用新型实施例的第三方面,提供一种包含气密性晶圆级芯片封装结构的电路板,所述气密性晶圆级芯片封装结构是如前述的气密性晶圆级芯片封装结构,所述气密性晶圆级芯片封装结构通过安装面安装于基板。

19.根据本实用新型实施例的第四方面,提供一种包含气密性晶圆级芯片封装结构的电子设备,所述气密性晶圆级芯片封装结构是如前述的气密性晶圆级芯片封装结构。

20.与现有技术相比较,本实用新型具有以下的技术特点:

21.1. 本气密性晶圆级芯片封装结构封装到基板的塑封过程中,由于芯片体以及与其焊接在一起的封盖,承担了主要的塑封压力,因此空腔结构得到了极大的保护,不会因塑封压力挤压变形而发生坍塌。

22.2. 由于芯片体和封盖承受了塑封压力,所以本气密性晶圆级芯片封装结构中的芯片体和封盖的厚度可以减小,使得晶圆级封装尺寸可以做到很小、厚度也可以灵活控制。尤其是,在高密度集成的诸如rf fem产品中,具有显著的优势。

23.3. 本气密性晶圆级芯片封装结构既能避免在密闭空腔内进行焊接带来的助焊剂残留等问题,也能避免因空腔中焊接凸点与空腔墙高度间的不匹配问题,大大简化了工艺流程,提升了产品质量。

附图说明

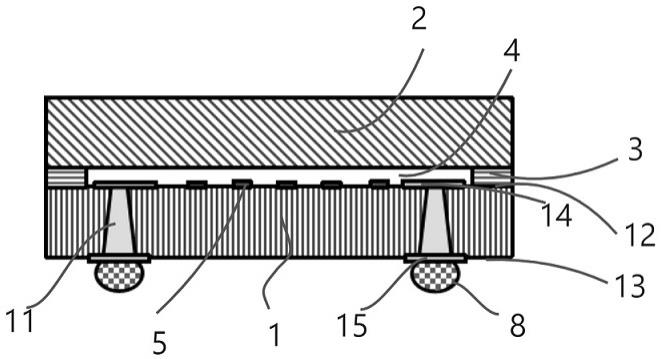

24.图1为本实用新型的第一实施例中,气密性晶圆级芯片封装结构的示意图;

25.图2为图1所示的第一实施例中,芯片体结构的示意图;

26.图3为图1所示的第一实施例中,连接器安装结构的示意图;

27.图4为图1所示的第一实施例中,组装结构的示意图;

28.图5为本实用新型的第二实施例中,气密性晶圆级芯片封装结构的示意图;

29.图6为图5所示的第二实施例中,连接器的芯片体上金属层的结构示意图;

30.图7为图5所示的第二实施例中,连接器的封盖上金属层的结构示意图;

31.图8为本实用新型的第三实施例中,气密性晶圆级芯片封装结构的示意图。

具体实施方式

32.下面结合附图和具体实施例对本实用新型的技术内容进行详细具体的说明。

33.《第一实施例》

34.如图 1所示,本实用新型提供的气密性晶圆级芯片封装结构包括芯片体1、封盖2,连接器3,位于空腔4内的电极5。

35.芯片体1在本实施例中为压电芯片,例如saw芯片、baw芯片。芯片体1是由硅晶片制成。如图 2所示,在芯片体1内通过激光钻孔形成导电通孔11,贯穿芯片体1的电极面12和安装面13。在电极面12上还通过溅射种子层或电镀导电层形成导电垫片14;在安装面13上形成导电盘15。导电盘15可以通过表面贴装技术(smt)或焊料与基板进行电连接。

36.在芯片体1上通过硅通孔(tsv)工艺形成导电通孔11,然后完成叉指换能器等其他功能信号层的制备。也可是先完成叉指换能器电极5等功能信号层之后,再形成导电层或利用tsv工艺形成导电通孔11。

37.封盖2通过连接器3与芯片体1连接。封盖2的材质包括但不限于玻璃晶片、硅基晶片、soi晶片或者其他litao3基材,也可以是覆铜板,或者其他硬质盖板。封盖2与芯片体1一样大小。换言之,封盖2在芯片体1上的投影覆盖整个电极面12。

38.连接器3位于电极面12上,连接芯片体1和封盖2,与芯片体1和封盖2共同围合形成空腔4。连接器3是一层环形结构,并且环绕电极5。因此,连接器3与芯片体1和封盖2形成的气密性良好的空腔结构,可以保护电极5,在本实施例中为叉指换能器(idt)电极。

39.连接器3可以是导电层,例如以金金键合的方式形成,也可以是聚合物干膜材料,经热压形成。如图3所示,例如,将聚合物干膜制成的连接器3覆压在芯片体1上;或者是用其他交联粘接材料涂覆在封盖2上形成连接器3(未图示)。

40.如图4所示,将封盖2覆压在相应的连接器3上,通过热压,使封盖2与连接器3压合在一起以形成气密连接。之后,可以通过植球(形成焊料8)或者凸点技术进行导电互连,也可以直接以lga 焊盘的形式完成后续在模组基板上的贴装。随后就可以进行切单、焊接、塑封等封装工艺。

41.《第二实施例》

42.如图5所示,本实用新型提供的气密性晶圆级芯片封装结构包括芯片体1、封盖2,连接器3’,位于空腔4内的电极5。

43.与第一实施例类似,芯片体1,在本实施例中为压电芯片,由硅晶片制成。在芯片体1内通过激光钻孔形成导电通孔11,贯穿芯片体1的电极面12和安装面13。在电极面12上还通过溅射种子层或电镀导电层形成导电垫片14;在安装面13上形成导电盘15。导电盘15可以通过表面贴装技术(smt)或焊料与基板进行电连接。

44.在芯片体1上通过硅通孔(tsv)工艺形成导电通孔11。

45.封盖2通过连接器3’与芯片体1连接。

46.不同于第一实施例,连接器3’包括三层结构:芯片体上金属层30、封盖上金属层31以及接合层32。

47.芯片体上金属层30,是在芯片体1上的连接器3’的位置利用电镀工艺形成的,可以是在tsv工艺之后,可以是tsv工艺之前,如图6所示。然后,完成idt等其他功能信号等fab制程。可以理解,也可是先完成idt等功能信号层之后再进行tsv通孔和导电极制作。

48.芯片体上金属层30与电极5,厚度(高度)不一样,材料不一样,加工制备工艺也是不一样;但是,金属层30与导电垫片14可以是同一层,使用相同材料,甚至可以在一个电镀工艺里面实现,例如都是金属电镀铜材料,在一道工艺里面同时加工形成。

49.在封盖2上,在连接器3’位置电镀相应的一层铜,作为封盖上金属层31,如图7所示。

50.然后,在芯片体上金属层30上涂敷焊锡,作为接合层32,再将封盖2和芯片体1进行热压,这样芯片体上金属层30上的焊锡与铜发生键合,形成cu-sn-cu键合,以将封盖上金属层31和芯片体上金属层30连接在一起。由此得到图5所示的具有三层结构的连接器3’的气密性晶圆级芯片封装结构。利用连接器3’形成气密性挡墙后,随后进行切单、焊接、塑封等封装工艺。

51.《第三实施例》

52.如图8所示,连接器3”具有两层结构。不同于第二实施例,连接器3”包括芯片体上金属层30、封盖上金属层31,但是没有接合层。

53.在芯片体1上的连接器3”的位置电镀一层铜得到芯片体上金属层30,在封盖2上的连接器3”的位置电镀相应的一层铜,作为封盖上金属层31。再将封盖2和芯片体1进行热压,形成使得芯片体上金属层30和封盖上金属层31之间直接发生cu-cu键合,连接在一起,形成气密性挡墙。

54.《第四实施例》

55.本实施例提供一种包含气密性晶圆级芯片封装结构的模组。其中,将第一至第三实施例中的气密性晶圆级芯片封装结构,以模组集成产品制备工艺,得到前述模组。

56.本实施例中的模组适用范围广,例如在各类rf fem模组产品中使用,如在difem、lpamid等射频模组器件中使用。

57.《第五实施例》

58.本实施例提供一种包含气密性晶圆级芯片封装结构的电路板,其中包含第一至第三实施例中的气密性晶圆级芯片封装结构,通过安装面安装于基板。

59.《第六实施例》

60.本实施例提供一种包含气密性晶圆级芯片封装结构的电子设备,其中包含第一至第三实施例中的气密性晶圆级芯片封装结构,或包含第一至第三实施例中的气密性晶圆级芯片封装结构的模组,或包含第一至第三实施例中的气密性晶圆级芯片封装结构的电路板。

61.本实施例中的气密性晶圆级芯片封装结构封装到基板的塑封过程中,由于芯片体以及与其焊接在一起的封盖,承担了主要的塑封压力,因此空腔结构得到了极大的保护,不会因塑封压力挤压变形而发生坍塌。

62.由于芯片体和封盖承受了塑封压力,所以本气密性晶圆级芯片封装结构中的芯片体和封盖的厚度可以减小,使得晶圆级封装尺寸可以做到很小、厚度也可以灵活控制。尤其是,在高密度集成的诸如rffem产品中,具有显著的优势。

63.而且,在本实用新型的各个实施例中,芯片体和封盖过覆膜热压形成空腔,通过导电通孔,将信号从位于电极面的导电极垫片引出到位于安装面的导电盘,再通过封装工艺焊接到模组基板上完成最终产品级互连。该结构能够有效地避免在密闭空腔内进行焊接带

来的助焊剂残留等问题,也避免了因空腔中焊接凸点与空腔墙高度间的不匹配问题,大大简化了工艺流程,提升了产品质量。

64.上面对本实用新型所提供的气密性晶圆级芯片封装结构及模组、电路板和电子设备进行了详细的说明。对本领域的一般技术人员而言,在不背离本实用新型实质内容的前提下对它所做的任何显而易见的改动,都将构成对本实用新型专利权的侵犯,将承担相应的法律责任。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1