一种高耐压防反灌保护电路的制作方法

1.本实用新型涉及模拟集成电路领域,具体涉及一种高耐压防反灌保护电路。

背景技术:

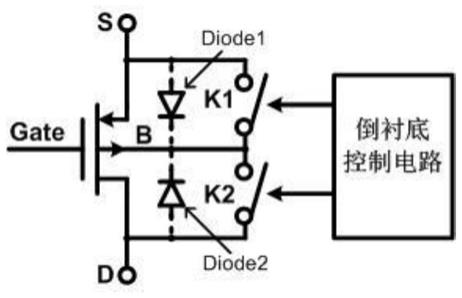

2.目前,低压差线性稳压器(ldo)跟线性锂电池充电管理芯片(charger)被广泛应用于各种便携式电子产品中,有些ldo的应用需要防止输入端vin掉电后输出端vout电压反灌到输入端vin;而锂电池charger都需防止bat电压反灌到输入端vin。主流ldo跟线性锂电池charger的内部功率管都是pmos晶体管,因pmos晶体管的源端s及漏端d跟衬底b间存在寄生二极管(见图1所示的diode1、diode2),所以pmos晶体管的衬底b不能固定接在其源端s上,需要控制电路根据其源端s跟漏端d的电位高低来选择,将衬底b的电位始终接到pmos晶体管源漏两极中的最高电位上(倒衬底电路如图1所示)。

3.对于高压应用场合,需要用到高压pldmos晶体管,而bcd工艺中pldmos晶体管的衬底b跟其源端s是固定接在一起的,其漏端d跟衬底b间的寄生二极管的负极就连接到其源端s上(如图2所示),当s端接的电源掉电后,其漏端电压就会经过寄生二极管反灌到源端。

4.对于高压pldmos晶体管的防反灌问题,传统的解决办法是将两个pldmos晶体管串联(如图3所示),上管的漏端d作为输入端in,下管的漏端d作为输出端out,两个pldmos晶体管的源端s连接,两者的栅极gate也连接,这样上下两个pldmos的寄生二极管是背靠背的,不存在反灌问题。

5.上述将两个pldmos晶体管串联解决防反灌问题的缺点是内阻增大了一倍,如果要将两个串联pldmos晶体管的内阻降到跟单个pldmos晶体管内阻一样,其版图面积将是单个pldmos晶体管版图面积的四倍。

6.高压防反灌的ldo跟线性锂电池充电管理芯片成本居高不下,因此如何降低高压防反灌pmos晶体管的内阻跟成本,成为问题的关键。

技术实现要素:

7.为解决上述问题,本实用新型提供了一种高耐压防反灌保护电路。

8.为实现上述目的,本实用新型的技术方案为:

9.一种高耐压防反灌保护电路,包括:

10.一pmos晶体管,其漏极与保护电路的输入端相连;

11.一pldmos晶体管,其源极与pmos晶体管的源极连接,漏极与保护电路的输出端相连;

12.所述pmos晶体管的栅极与pldmos晶体管的栅极连接之后接入外部控制信号。

13.进一步的,所述pmos晶体管为低压晶体管,所述pldmos晶体管为高压晶体管。

14.进一步的,所述pmos晶体管的漏极与源极通过第一体二极管连接,所述第一体二极管的阳极与pmos晶体管的漏极连接,阴极与pmos晶体管的源极连接。

15.进一步的,所述pldmos晶体管的漏极与源极通过第二体二极管连接,所述第二体

二极管的阳极与pldmos晶体管的漏极连接,阴极与pldmos晶体管的源极连接。

16.更进一步的,所述保护电路的输入端与电压源连接,输出端与低压差线性稳压器或线性锂电池充电管理芯片的输出端连接。

17.与现有技术相比,本实用新型的有益效果在于:

18.本实用新型提出的高耐压防反灌保护电路在高压pldmos晶体管的上方串了一个低压pmos晶体管,利用二者衬底间背靠背的二极管可以避免输入端掉电后输出端电压反灌到输入端。由于低压pmos晶体管的内阻跟版图面积远小于高压pldmos晶体管,本实用新型提出的高耐压防反灌保护电路的版图面积在同等内阻下仅为传统方案两个高压pldmos晶体管串联结构的40%~45%,大大降低了高耐压防反灌保护电路的成本。

附图说明

19.图1是低压防反灌保护电路倒衬底控制电路图;

20.图2是pldmos晶体管及衬底寄生二极管电路图;

21.图3是传统的两个高压pldmos晶体管串联形成的防反灌保护电路示意图;

22.图4是本实用新型实施例提出的高耐压防反灌保护电路示意图。

具体实施方式

23.以下将结合附图,对本实用新型的技术方案进行详细说明。

24.本实用新型的实施例设计了一种高耐压防反灌保护电路,如图4所示,低压pmos晶体管的漏极d1与保护电路的输入端in相连,其源极s1连接到高压pldmos晶体管的源极s2,高压pldmos晶体管的漏极d2与保护电路的输出端out相连,其栅极跟低压pmos晶体管的栅极连接之后接入外部控制信号。

25.该高耐压防反灌保护电路用于低压差线性稳压器ldo时,其输入端接稳压器的供电电源,输出端接稳压器的输出端,其栅极gate由稳压器的控制电路控制。

26.正常工作时,本实施例中高耐压防反灌保护电路的栅极gate电位由稳压器控制电路控制使防反灌保护电路中的低压pmos晶体管跟高压pldmos晶体管均处于开启状态,由于该保护电路上端的低压pmos晶体管内阻很小,低压pmos晶体管源漏两极的压降很小,所以该结构的耐压值不受低压pmos晶体管影响,其输入端电源电压可以高到pldmos晶体管的最高耐压值。当稳压器电源掉电后,稳压器控制电路将该保护电路的gate电位连接到输入端与输出端二者中的高电位上使本实施例中的低压pmos晶体管跟高压pldmos晶体管均处于关闭状态,此时高压pldmos晶体管的衬底二极管正偏,低压pmos晶体管的衬底二极管反偏截止,输入端到输出端的两个体二极管背靠背不通,不存在反灌路径。

27.实施例仅为说明本实用新型的技术思想,不能以此限定本实用新型的保护范围,凡是按照本实用新型提出的技术思想,在技术方案基础上所做的任何改动,均落入本实用新型保护范围之内。

技术特征:

1.一种高耐压防反灌保护电路,其特征在于,包括:一pmos晶体管,其漏极与保护电路的输入端相连;一pldmos晶体管,其源极与pmos晶体管的源极连接,漏极与保护电路的输出端相连;所述pmos晶体管的栅极与pldmos晶体管的栅极连接之后接入外部控制信号。2.根据权利要求1所述的高耐压防反灌保护电路,其特征在于:所述pmos晶体管为低压晶体管,所述pldmos晶体管为高压晶体管。3.根据权利要求1所述的高耐压防反灌保护电路,其特征在于:所述pmos晶体管的漏极与源极通过第一体二极管连接,所述第一体二极管的阳极与pmos晶体管的漏极连接,阴极与pmos晶体管的源极连接。4.根据权利要求1所述的高耐压防反灌保护电路,其特征在于:所述pldmos晶体管的漏极与源极通过第二体二极管连接,所述第二体二极管的阳极与pldmos晶体管的漏极连接,阴极与pldmos晶体管的源极连接。5.根据权利要求1所述的高耐压防反灌保护电路,其特征在于:所述保护电路的输入端与电压源连接,输出端与低压差线性稳压器或线性锂电池充电管理芯片的输出端连接。

技术总结

本实用新型公开了一种高耐压防反灌保护电路,低压PMOS晶体管的漏极与保护电路的输入端相连,其源极连接到高压PLDMOS晶体管的源极,高压PLDMOS晶体管的漏极与保护电路的输出端相连,其栅极跟低压PMOS的栅极连接之后接入外部控制信号。本实用新型提出的高耐压防反灌保护电路在高压PLDMOS晶体管的上方串了一个低压PMOS晶体管,利用二者衬底间背靠背的二极管可以避免输入端掉电后输出端电压反灌到输入端。由于低压PMOS晶体管的内阻跟版图面积远小于高压PLDMOS晶体管,本实用新型提出的高耐压防反灌保护电路的版图面积在同等内阻下仅为传统方案两个高压PLDMOS晶体管串联结构的40%~45%,大大降低了高耐压防反灌保护电路的成本。成本。成本。

技术研发人员:黄九洲 夏炎

受保护的技术使用者:江苏硅国微电子有限公司

技术研发日:2021.03.15

技术公布日:2021/12/10

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1