半导体装置的制作方法

本发明涉及一种半导体装置(semiconductor device(也称“半导体器件”))。

背景技术:

1、已知一种设置在半导体装置中以保护半导体装置的内部电路免受静电放电(esd:electro-static discharge)的影响的esd保护电路。例如,esd保护电路具有配置在外部端子和接地线之间的晶体管、以及响应于被施加至外部端子的esd事件(event)而提高esd保护电路的晶体管的栅极电压的控制电路。在这种esd保护电路中,有时还具有响应于esd事件而生成控制电压的rc电路(resistor-capacitance circuit)。

2、[引证文件]

3、[专利文件]

4、[专利文件1]美国专利第11056880号说明书

5、[专利文件2]美国专利申请公开第2014/0307354号说明书

6、[专利文件3]美国专利第10535647号说明书

技术实现思路

1、[要解决的技术问题]

2、近年来,随着晶体管等半导体元件的微细化(小型化)和半导体装置的低电力化(低功耗化),搭载(安装/设置/布置)于半导体装置的晶体管等的元件的耐压性(耐压能力)日益降低。例如,在esd保护电路中使用低耐压型晶体管的情况下,需要控制栅极电压,以在抑制晶体管被破坏(例如,击穿)的同时提高esd保护电路的能力(性能)。

3、本发明是鉴于上述问题而提出的,其目的在于,即使在esd保护电路中设置低耐压型晶体管的情况下,也能抑制晶体管被破坏,同时还能提高esd保护电路的性能。

4、[技术方案]

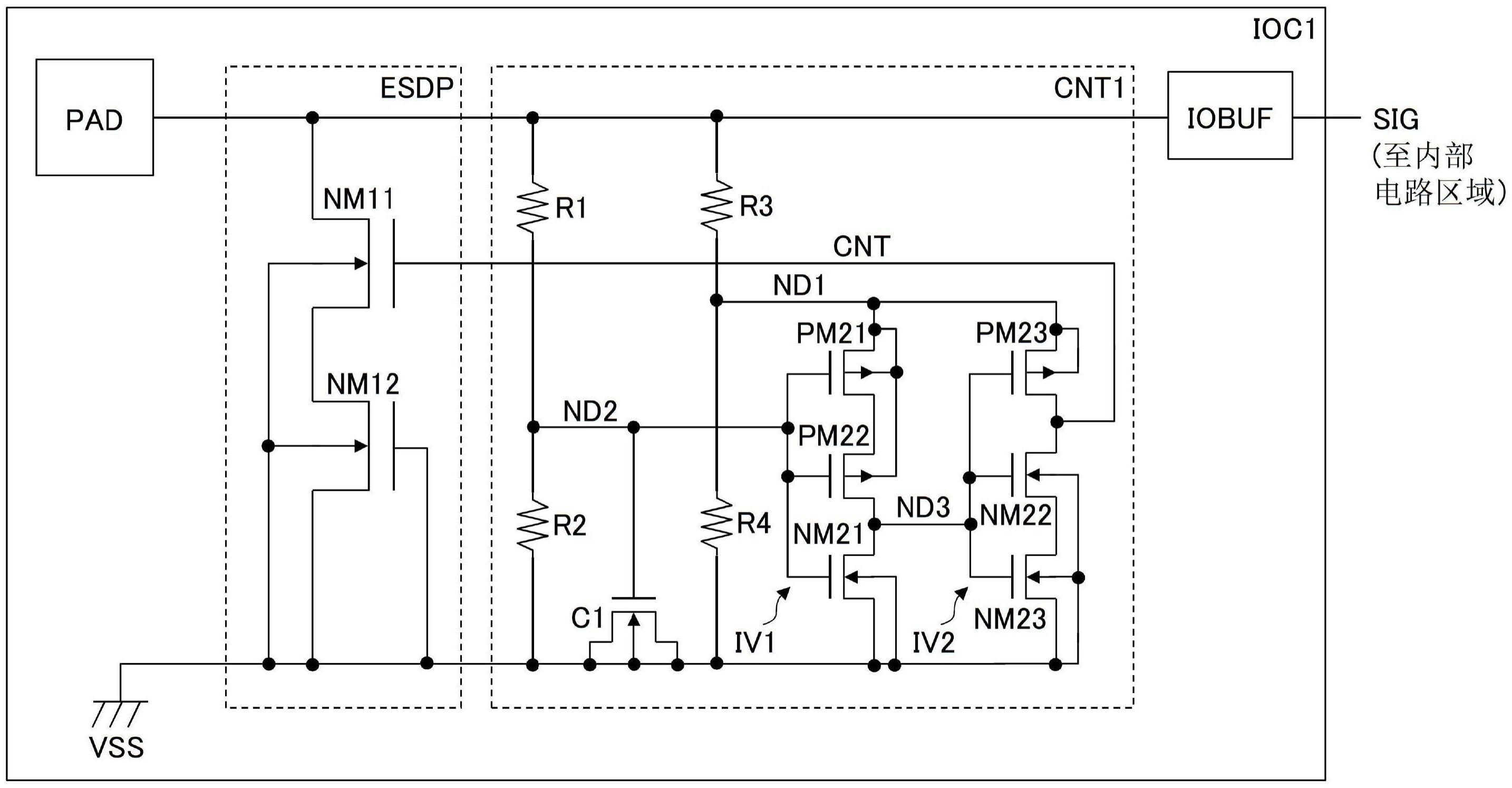

5、根据本发明的一个侧面,提供一种半导体装置,其具有:esd保护电路,具备设置在信号端子和接地线之间的第一n沟道mos晶体管;及控制电路,与所述信号端子电连接。其中,当高电平的信号被供给至所述信号端子时,所述控制电路将通过对所述信号的高电平电压进行降压而获得的第一电压输出到所述第一n沟道mos晶体管的栅极,当由esd引起的浪涌被输入至所述信号端子时,所述控制电路将低于所述第一电压的第二电压输出到所述第一n沟道mos晶体管的所述栅极。

6、[有益效果]

7、根据公开的技术,即使在esd保护电路中设置低耐压型晶体管的情况下,也能抑制晶体管被破坏,同时还能提高esd保护电路的性能。

技术特征:

1.一种半导体装置,具有:

2.如权利要求1所述的半导体装置,其中,

3.一种半导体装置,具有:

4.如权利要求2或3所述的半导体装置,其中,

5.如权利要求2或3所述的半导体装置,其中,

6.如权利要求2或3所述的半导体装置,其中,

7.如权利要求2或3所述的半导体装置,其中,

8.如权利要求2或3所述的半导体装置,其中,

技术总结

本发明提供一种半导体装置,其具有:ESD保护电路,具备设置在信号端子和接地线之间的第一N沟道MOS晶体管;及控制电路,与所述信号端子电连接。其中,当高电平的信号被供给至所述信号端子时,所述控制电路将通过对所述信号的高电平电压进行降压而获得的第一电压输出到所述第一N沟道MOS晶体管的栅极,当由ESD引起的浪涌被输入至所述信号端子时,所述控制电路将低于所述第一电压的第二电压输出到所述第一N沟道MOS晶体管的所述栅极。

技术研发人员:小岛正誉

受保护的技术使用者:株式会社索思未来

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!