基于小数分频的PWM设计实现高精度实时数字DCDC电路的制作方法

本发明涉及电子,尤其涉及一种基于小数分频的pwm设计实现高精度实时数字dcdc电路。

背景技术:

1、在既有的dcdc设计电路中,数字pwm模块采用整数pwm设计,整数占空比的分辨率不能达到精准调制的需求,需要软件反复调整占空比系数,调制效果差,并且会出现输出抖动。因此,势必需要一种带小数占空比的更高分辨率的pwm设计因此,如何提供一种带小数占空比的更高分辨率的pwm设计,并以此实现一种高精度dcdc电路,对提高dc/dc效率、精度具有重要意义。

技术实现思路

1、本发明描述了一种基于小数分频的pwm设计实现高精度实时数字dcdc电路,以实现一种高精度实时数字dcdc电路。

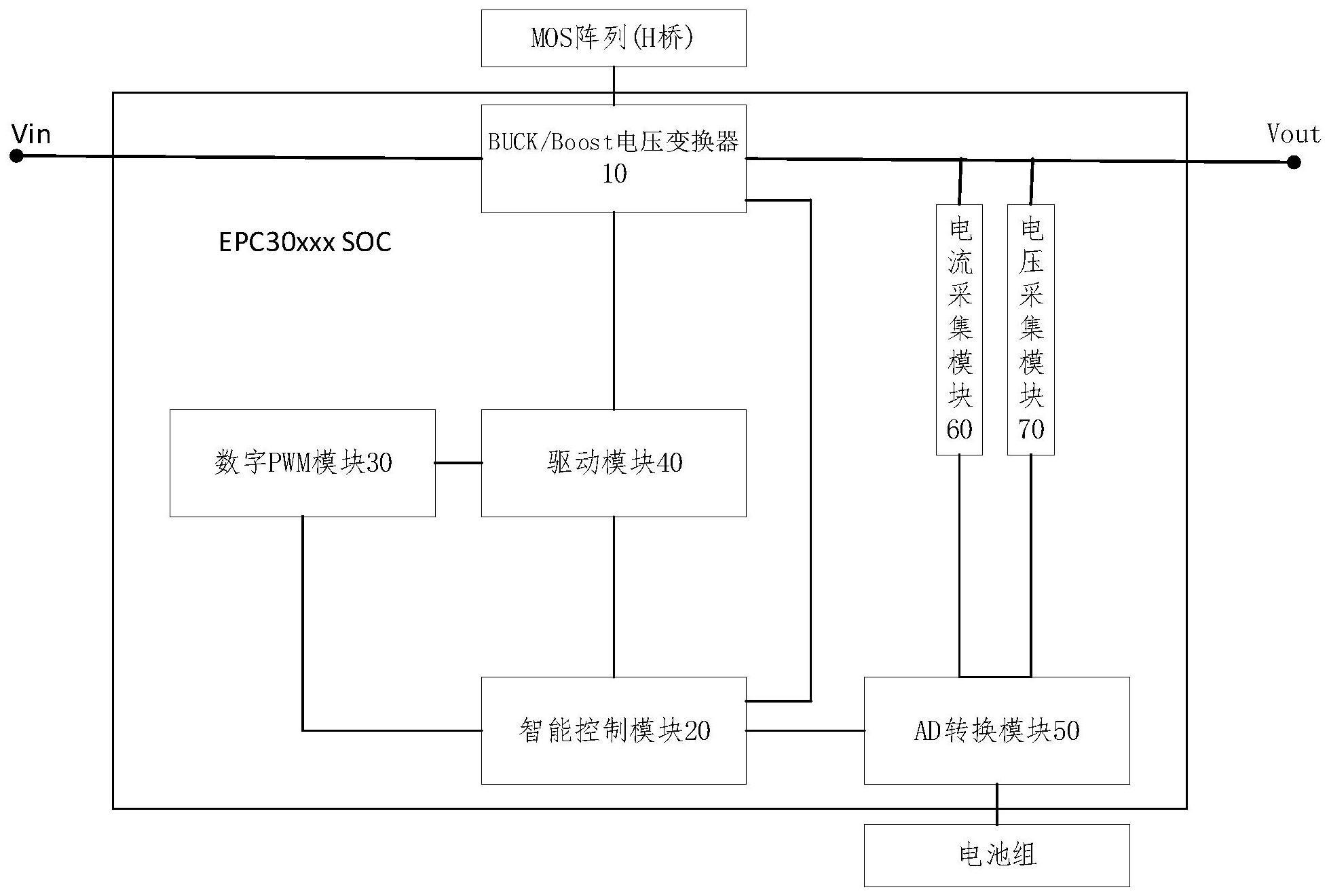

2、本发明的一个方面,提供了一种基于小数分频的pwm设计实现高精度实时数字dcdc电路,包括集成设计的buck/boost电压变换器、智能控制模块、数字pwm模块以及驱动模块,其中:

3、智能控制模块,基于与buck/boost电压变换器连接的mos阵列的实时电压、电流参数,电池soc参数,驱动模块产生的死区配置参数,通过预设算法模型动态生成数字pwm模块的小数分频配置参数,通过soc的集成设计实现低延时动态闭环自学习能力,实现实时高精度数字dcdc功能,达到数字dcdc的最高转换效率;

4、buck/boost电压变换器,对负载充放电支路进行升降压调整;

5、数字pwm模块,电连接于所述智能控制模块与驱动模块之间,数字pwm模块支持小数分频功能,用于根据智能控制模块输出的小数分频配置参数产生pwm信号并传输到驱动模块;

6、驱动模块,电连接于所述数字pwm模块与所述buck/boost电压变换器之间,根据所述数字pwm模块的pwm信号控制所述buck/boost电压变换器的工作参数以实现对负载充放电支路的升降压控制。

7、进一步地,所述的基于小数分频的pwm设计实现高精度实时数字dcdc电路,还包括ad转换模块、电流采集模块和电压采集模块;

8、ad转换模块的输出端与智能控制模块连接,ad转换模块的第一输入端分别连接电流采集模块的输出端以及电压采集模块的输出端连接,以采集buck/boost电压变换器实时输出的电压信号和电流信号,所述ad转换模块的第二输入端与电池组连接,以采集电池组的电池soc参数。

9、进一步地,所述数字pwm模块产生的pwm信号的脉宽的计算保留整数部分和小数部分。

10、本发明的第二方面,提供一种快充装置,包括至少一路如上所述的基于小数分频的pwm设计实现高精度实时数字dcdc电路。

11、本发明实施例提供的基于小数分频的pwm设计实现高精度实时数字dcdc电路,给整数pwm添加小数占空比的功能,极大的增加了pwm的精度,以此实现dc/dc控制,可以在快速响应的同时提高dcdc输出精度,而且通过soc的集成设计实现低延时动态闭环自学习能力,实现实时高精度数字dcdc功能,达到数字dcdc的最高转换效率。

12、上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其它目的、特征和优点能够更明显易懂,以下特举本发明的具体实施方式。

技术特征:

1.一种基于小数分频的pwm设计实现高精度实时数字dcdc电路,其特征在于,包括集成设计的buck/boost电压变换器、智能控制模块、数字pwm模块以及驱动模块,其中:

2.根据权利要求1所述的基于小数分频的pwm设计实现高精度实时数字dcdc电路,其特征在于,还包括ad转换模块、电流采集模块和电压采集模块;

3.根据权利要求1-2任一项所述的基于小数分频的pwm设计实现高精度实时数字dcdc电路,其特征在于,所述数字pwm模块产生的pwm信号的脉宽的计算保留整数部分和小数部分。

4.一种快充装置,其特征在于,包括至少一路如权利要求1-3任一项所述的基于小数分频的pwm设计实现高精度实时数字dcdc电路。

技术总结

本发明提供一种基于小数分频的PWM设计实现高精度实时数字DCDC电路,包括:智能智能控制模块,基于MOS阵列的实时电压、电流参数,电池SOC参数,驱动模块产生的死区配置参数,通过预设算法模型动态生成数字PWM模块的小数分频配置参数;BUCK/Boost电压变换器,对负载充放电支路进行升降压调整;数字PWM模块支持小数分频功能,根据智能控制模块输出的小数分频配置参数产生PWM信号并传输到驱动模块;驱动模块,连接于数字PWM模块与BUCK/BOOST电压变换器之间,根据数字PWM模块的PWM信号控制BUCK/BOOST电压变换器的工作参数以实现对负载充放电支路的升降压控制。本发明通过SOC的集成设计实现低延时闭环自学习能力,实现实时高精度数字DCDC功能,达到数字DCDC的最高转换效率。

技术研发人员:张富彬,王诺,刘浩淼,钟裕捷,李仕胜

受保护的技术使用者:北京鸿智电通科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!