一种应用于RS-485驱动级电流的可调电路结构的制作方法

本发明涉及集成电路i/o端口,特别涉及一种应用于rs-485驱动级电流的可调电路结构。

背景技术:

1、随着工业领域控制技术的不断发展和计算机网络技术的广泛应用,需要一种能够满足远距离数字通信的总线技术。由电子工业协会制定于1983年的rs-485总线标准能够满足远距离传输的要求。另外,相比与其他总线技术,rs-485使用平衡双线传输,具有抗噪声能力强、数据传输速率高效、数据传输可靠性高的优点,同时能够支持多节点、远距离通信。由于rs-485传输距离远的特点,发送端与接收端的地电位差,使得共模输出电压满足-7v~+12v的范围。这就需要驱动电路能够满足端口耐压的同时,还需要在-7v~+12v电压范围内获得稳定的驱动电流,而过大的端口电流将会出现烧坏电路的情况。

2、一个典型的驱动器的输出端口,上拉使用高压pmos进行驱动,下拉使用高压nmos进行驱动。当上拉开启时,随着端口从vcc~-7v的变化过程中,驱动电流会持续增加;下拉情况也是如此,当下拉开启时,随着端口从0~12v的变化过程中,驱动电流会持续增加。上述过程可能出现驱动级电流过大,超过应用的允许范围。常用的设计使用两路并联驱动,当电流超过一定范围后,关闭其中一路,从而减小驱动级电流。也有对电压进行检测的设计,以上拉通道举例,当端口电压低于0v时,检测电路输出数字逻辑,关闭一路驱动。但是上述的方法存在较大的问题是,由于工艺的偏差,会使得关闭一路后的驱动电流往往无法满足电路的设计要求,而且电路与电路之间存在一定偏差。

技术实现思路

1、本发明的目的在于提供一种应用于rs-485驱动级电流的可调电路结构,以解决现有的驱动电路端口电流随工艺偏差过大的问题。

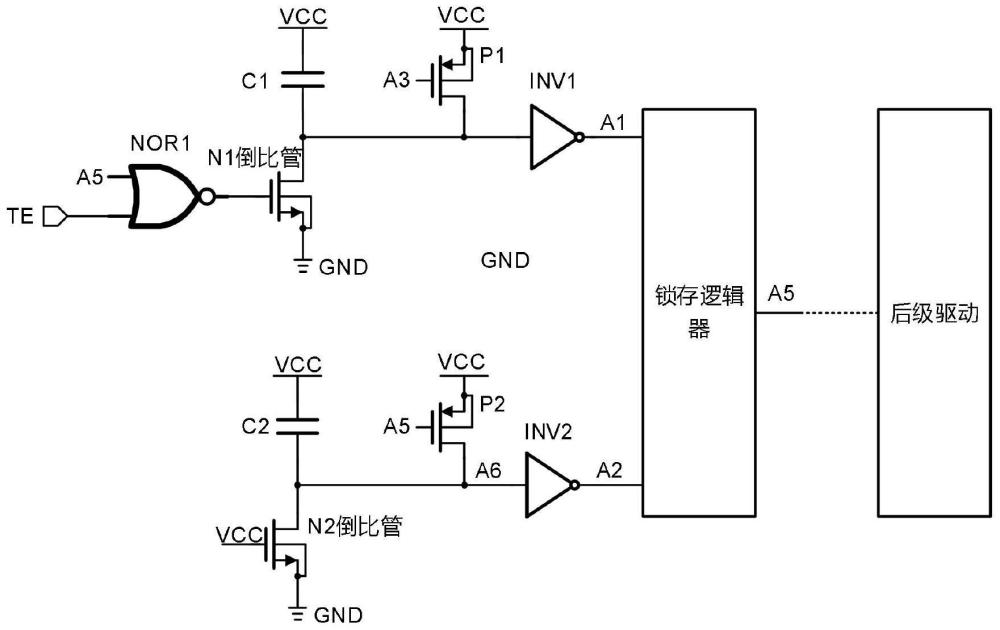

2、为解决上述技术问题,本发明提供了一种应用于rs-485驱动级电流的可调电路结构,包括输入端te、nmos管n1~n2、pmos管p1~p2、电容c1~c2、反相器inv1~inv2、或非门nor1和锁存逻辑器;

3、或非门nor1的第一输入端接输入端te,第二输入端接锁存逻辑器的输出端,输出端接nmos管n1的栅端;nmos管n1的漏端同时接电容c1的第一端、pmos管p1的漏端和反相器inv1的输入端,电容c1的第二端接电源vcc,pmos管p1的栅端接节点a3;反相器inv1的输出端接锁存逻辑器的第一输入端;

4、电容c2的第一端接vcc,第二端同时接nmos管n2的漏端、pmos管p2的漏端和反相器inv2的输入端;nmos管n2的栅端接电源vcc,pmos管p2的栅端接锁存逻辑器的输出端;反相器inv2的输出端接锁存逻辑器的第二输入端;

5、锁存逻辑器的输出端接后端的后级驱动。

6、在一种实施方式中,所述锁存逻辑器包括或非门nor2、nor3和反相器inv3;

7、或非门nor2的第一输入端接反相器inv1的输出端,第二输入端接或非门nor3的输出端,或非门nor2的输出端接节点a3,节点a3接或非门nor3的第一输入端,或非门nor3的第二输入端接反相器inv2的输出端;反相器inv3的输入端接节点a3,输出端接后端的后级驱动。

8、在一种实施方式中,所述nmos管n1~n2的源端和衬底相连并连接gnd;所述pmos管p1~p2的源端和衬底相连并连接vcc。

9、在一种实施方式中,所述电容c1和c2具有可调特性。

10、本发明提供的一种应用于rs-485驱动级电流的可调电路结构,实现驱动器开闭控制信号时间的比例可调,从而可以获得可调节的驱动电流。另外该电路设计实现简单,本发明使用外部检测电路的输出信号te,控制锁存逻辑器的状态翻转,从而控制后级驱动的开闭时间,实现对驱动器驱动电流的可调,有效避免由于过流而烧坏电路和影响总线信号。

技术特征:

1.一种应用于rs-485驱动级电流的可调电路结构,其特征在于,包括输入端te、nmos管n1~n2、pmos管p1~p2、电容c1~c2、反相器inv1~inv2、或非门nor1和锁存逻辑器;

2.如权利要求1所述的应用于rs-485驱动级电流的可调电路结构,其特征在于,所述锁存逻辑器包括或非门nor2、nor3和反相器inv3;

3.如权利要求1所述的应用于rs-485驱动级电流的可调电路结构,其特征在于,所述nmos管n1~n2的源端和衬底相连并连接gnd;所述pmos管p1~p2的源端和衬底相连并连接vcc。

4.如权利要求1所述的应用于rs-485驱动级电流的可调电路结构,其特征在于,所述电容c1和c2具有可调特性。

技术总结

本发明公开一种应用于RS‑485驱动级电流的可调电路结构,属于集成电路I/O端口领域,包括输入端TE、NMOS管N1~N2、PMOS管P1~P2、电容C1~C2、反相器INV1~INV2、或非门NOR1和锁存逻辑器;本发明实现驱动级端口电流的可调节,需要结合检测电路,在触发检测时对锁存逻辑器进行写入,检测后,锁存逻辑器状态恢复。利用电容可调,实现锁存逻辑器写入和恢复状态的时间可调,从而实现了后级驱动开闭时间的可调,获得可调的驱动电流;另外电路结构简单,应用范围广,适用于驱动器芯片设计中。

技术研发人员:喻丹,高国平,万瑞,李贤章

受保护的技术使用者:中国电子科技集团公司第五十八研究所

技术研发日:

技术公布日:2024/3/21

- 还没有人留言评论。精彩留言会获得点赞!