超低漏电的ESD保护电路及芯片的制作方法

本申请实施例涉及保护电路,尤其涉及一种超低漏电的esd保护电路及芯片。

背景技术:

1、随着电器在生活中的运用,静电放电也成为了一种常见现象。在电器的制造或使用中,都有可能发生静电放电(electrostatic discharge,esd)。由于静电放电的瞬间电压通常非常高(>几千伏),静电放电对元器件的损伤是毁灭性和永久性的,会造成集成电路直接烧毁。因此,预防静电损伤是所有集成电路设计和制造的头号难题。

2、目前针对静电放电现象的解决办法是,在制造设备时对电路设置硬件防护。常用的防护硬件例如二极管,利用电路正常工作时处于截止状态,不影响电路正常工作,当电路出现异常过压并达到其击穿电压时,迅速导通使瞬间电流流出,同时把异常高压箝制在一个安全水平之内,从而保护被保护的集成电路或线路。

3、但二极管在反向截止的时候,并不是完全理想的截止,依旧会有漏电流流出。大的漏电流会给电路带来较大的损耗,特别在高压应用场合。因此,如何降低电路中的漏电流,成为一个亟待解决的问题。

技术实现思路

1、鉴于上述问题,本申请实施例提供了一种超低漏电的esd保护电路及芯片,可以降低电路中的漏电流。

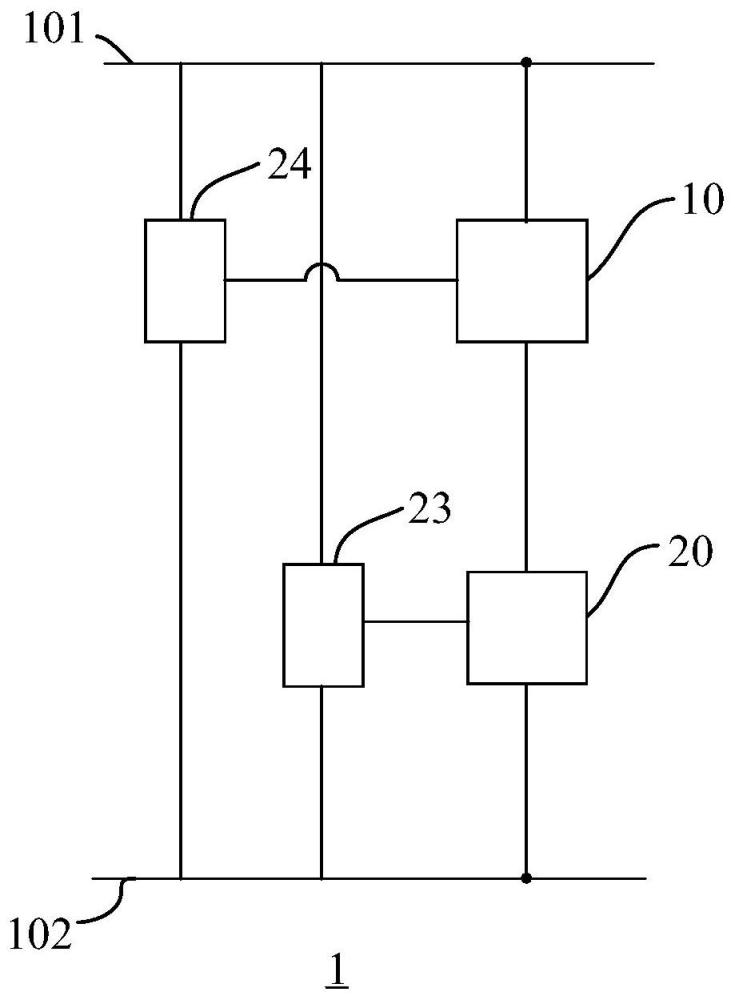

2、第一方面,本申请实施例提供了一种超低漏电的esd保护电路,输入端与第一pin脚连接,输出端与第二pin脚连接;超低漏电的esd保护电路包括串联的esd模块和漏电控制模块,漏电控制模块的阻断电阻大于esd模块的阻断电阻,以阻止第一pin脚的电流经过esd保护电路流出第二pin脚。

3、在一种可能的实现方式中,当第一pin脚与第二pin脚之间的电压大于或等于第一阈值时,esd模块和漏电控制模块导通,以使第一pin脚的电流经过esd保护电路传导至第二pin脚。

4、在一种可能的实现方式中,漏电控制模块包括相连接的低漏电开关和第一电压控制模块。

5、第一电压控制模块,用于控制低漏电开关的两端电压,以调节低漏电开关的关闭程度。

6、在一种可能的实现方式中,低漏电开关包括第一mos管,第一电压控制模块的输入端连接第一mos管的漏极,第一电压控制模块的第一输出端连接第一mos管的栅极,第一电压控制模块的第二输出端连接第一mos管的源极。

7、第一电压控制模块,用于将第一mos管的漏极电压转化为第一输出电压和第二输出电压,并通过第一输出端输出第一输出电压,通过第二输出端输出第二输出电压。其中,第一输出电压大于第二输出电压,以使第一mos管的栅极电压大于第一mos管的源极电压。

8、在一种可能的实现方式中,esd模块包括第二mos管,第二mos管的源极与第一pin脚连接,第二mos管的漏极与第一mos管的源极连接。

9、在一种可能的实现方式中,电路还包括第二电压控制模块和第三电压控制模块。第二电压控制模块分别连接第一pin脚、第二pin脚和第一mos管的栅极,第三电压控制模块分别连接第一pin脚、第二pin脚和第二mos管的栅极。

10、第二电压控制模块用于控制第一mos管的栅极电压,第三电压控制模块用于控制第二mos管的栅极电压,以控制第一pin脚与第二pin脚之间的电压。

11、在一种可能的实现方式中,第二电压控制模块包括第一电容,第一pin脚和第一mos管的栅极均与第一电容的输入端连接,第二pin脚与第一电容的输出端连接;第三电压控制模块包括第二电容,第一pin脚和第二mos管的栅极均与第二电容的输入端连接,第二pin脚与第二电容的输出端连接。

12、在一种可能的实现方式中,还包括二次漏电保护模块,二次漏电保护模块与低漏电开关串联,二次漏电保护模块包括电阻、二极管、双极性晶体管和可控硅中的至少一项。

13、第二方面,本申请实施例提供了一种芯片,包括如第一方面中任一项的超低漏电的esd保护电路。

14、在一种可能的实现方式中,第一pin脚为电源端,第二pin脚为pad。或,第一pin脚为pad,第二pin脚为接地端。

15、本申请实施例提供的超低漏电的esd保护电路及芯片,通过将esd模块和漏电控制模块串联,增加了静电流从电路中经过esd模块和漏电控制模块后流出的阻碍,降低了静电流流出电路的可能性,并通过使漏电控制模块的阻断电阻大于esd模块的阻断电阻,在电流从esd模块流出的路径上增设阻碍,阻止静电从esd模块流出,从而可以进一步地加强电路的静电保护,降低电路中的漏电流。上述说明仅是本申请实施例技术方案的概述,为了能够更清楚了解本申请实施例的技术手段,而可依照说明书的内容予以实施,并且为了让本申请实施例的上述和其它目的、特征和优点能够更明显易懂,以下特举本申请的具体实施方式。

技术特征:

1.一种超低漏电的esd保护电路,其特征在于,所述esd保护电路的输入端与第一pin脚连接,所述esd保护电路的输出端与第二pin脚连接;

2.根据权利要求1所述的电路,其特征在于,当所述第一pin脚与所述第二pin脚之间的电压大于或等于第一阈值时,所述esd模块和所述漏电控制模块导通,以使所述第一pin脚的电流经过所述esd保护电路传导至所述第二pin脚。

3.根据权利要求1所述的电路,其特征在于,所述漏电控制模块包括相连接的低漏电开关和第一电压控制模块;

4.根据权利要求3所述的电路,其特征在于,所述低漏电开关包括第一mos管,所述第一电压控制模块的输入端连接所述第一mos管的漏极,所述第一电压控制模块的第一输出端连接所述第一mos管的栅极,所述第一电压控制模块的第二输出端连接所述第一mos管的源极;

5.根据权利要求4所述的电路,其特征在于,所述esd模块包括第二mos管,所述第二mos管的源极与所述第一pin脚连接,所述第二mos管的漏极与所述第一mos管的源极连接。

6.根据权利要求5所述的电路,其特征在于,所述电路还包括第二电压控制模块和第三电压控制模块;所述第二电压控制模块分别连接所述第一pin脚、所述第二pin脚和所述第一mos管的栅极,所述第三电压控制模块分别连接所述第一pin脚、所述第二pin脚和所述第二mos管的栅极;

7.根据权利要求6所述的电路,其特征在于,所述第二电压控制模块包括第一电容,所述第一pin脚和所述第一mos管的栅极均与所述第一电容的输入端连接,所述第二pin脚与所述第一电容的输出端连接;

8.根据权利要求3所述的电路,其特征在于,还包括二次漏电保护模块,所述二次漏电保护模块与所述低漏电开关串联,所述二次漏电保护模块包括电阻、二极管、双极性晶体管和可控硅中的至少一项。

9.一种芯片,其特征在于,包括如权利要求1至8中任一项所述的超低漏电的esd保护电路。

10.根据权利要求9所述的芯片,其特征在于,所述第一pin脚为电源端,所述第二pin脚为pad;或,所述第一pin脚为pad,所述第二pin脚为接地端。

技术总结

本申请实施例提供一种超低漏电的ESD保护电路及芯片。其中,超低漏电的ESD保护电路的输入端与第一PIN脚连接,所述ESD保护电路的输出端与第二PIN脚连接;所述ESD保护电路包括串联的ESD模块和漏电控制模块,所述漏电控制模块的阻断电阻大于所述ESD模块的阻断电阻,以阻止所述第一PIN脚的电流经过所述ESD保护电路流出所述第二PIN脚。本申请实施例提供的超低漏电的ESD保护电路可以降低电路中的漏电流。

技术研发人员:陈原,王建

受保护的技术使用者:上海类比半导体技术有限公司

技术研发日:

技术公布日:2024/2/29

- 还没有人留言评论。精彩留言会获得点赞!