一种高性能高耐压的副边同步整流控制电路的制作方法

本技术涉及同步整流控制芯片,尤其涉及一种高性能高耐压的副边同步整流控制电路。

背景技术:

1、同步整流控制芯片,适用于隔离型的同步整流应用,尤其适用于正激和反激系统,支持dcm,bcm,ccm和qr多种工作模式。但是,现有的同步整流控制芯片无法避免以下问题:1、因激磁振荡引起的驱动芯片误动作;2、在ccm工作条件下,纯电压判定的关断延迟造成的效率损失。

技术实现思路

1、本实用新型所要解决的技术问题是针对现有的同步整流控制芯片因激磁振荡引起的驱动芯片误动作以及在ccm工作条件下,纯电压判定的关断延迟造成的效率损失的缺陷,提供一种高性能高耐压的副边同步整流控制电路。

2、本实用新型解决上述技术问题所采用的技术方案如下:

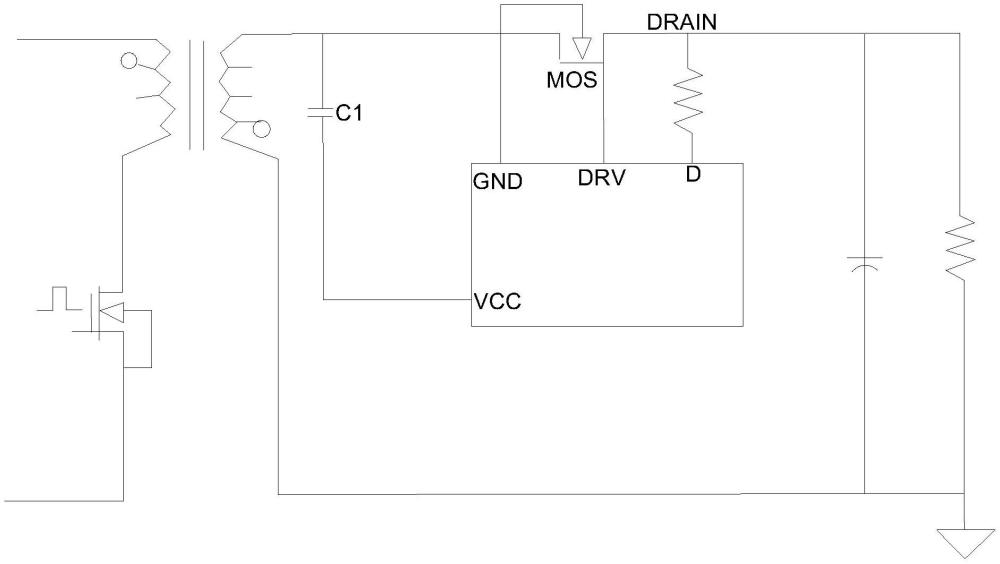

3、提供一种高性能高耐压的副边同步整流控制电路,包括副边同步整流控制芯片,所述副边同步整流控制芯片包括同步整流驱动脚位drv、同步整流驱动器的芯片地gnd、同步整流管的供电脚位vcc、同步整流驱动器的漏极电压检测脚d及nc悬空端,所述同步整流驱动脚位drv和mos管的栅极连接,所述同步整流驱动器的芯片地gnd和mos管的源极连接,所述同步整流管的供电脚位vcc接旁路电容到所述同步整流驱动器的芯片地gnd,所述同步整流驱动器的漏极电压检测脚d接mos管漏极。

4、进一步地,所述同步整流驱动器的漏极电压检测脚d用于供电给所述同步整流管的供电脚位vcc。

5、进一步地,所述mos管的drain与芯片的d脚之间电阻取值为5ω~20ω。

6、进一步地,所述旁路电容紧靠所述同步整流管的供电脚位vcc和所述同步整流驱动器的芯片地gnd。

7、与现有技术相比较,采用本实用新型提供的高性能高耐压的副边同步整流控制电路,包括副边同步整流控制芯片,所述副边同步整流控制芯片包括同步整流驱动脚位drv、同步整流驱动器的芯片地gnd、同步整流管的供电脚位vcc、同步整流驱动器的漏极电压检测脚d及nc悬空端,所述同步整流驱动脚位drv和mos管的栅极连接,所述同步整流驱动器的芯片地gnd和mos管的源极连接,所述同步整流管的供电脚位vcc接旁路电容到所述同步整流驱动器的芯片地gnd,所述同步整流驱动器的漏极电压检测脚d接mos管漏极,这样,当系统上电后,通过内置mos管的体二极管对输出电容充电,输出电压上升,通过同步整流驱动器的漏极电压检测脚d连接输出电压,当输出电压上升时,经过芯片内部供电电路,给同步整流管的供电脚位vcc电容充电,当同步整流管的供电脚位vcc的电压充到开启阈值电压时,芯片内部控制电路开始工作,mos管正常的导通和关断,mos管正常的导通时,电流不再从体二极管流过,而从mos管的沟道流过,芯片正常工作时,所需的工作电流仍然会通过同步整流驱动器的漏极电压检测脚d给同步整流管的供电脚位vcc供电,在不需要辅助绕组供电的情况下,保证同步整流管的供电脚位vcc供电脚都不会欠压,可以有效避免因激磁振荡引起的驱动芯片误动作以及在ccm工作条件下纯电压判定的关断延迟造成的效率损失。

技术特征:

1.一种高性能高耐压的副边同步整流控制电路,其特征在于,包括副边同步整流控制芯片,所述副边同步整流控制芯片包括同步整流驱动脚位drv、同步整流驱动器的芯片地gnd、同步整流管的供电脚位vcc、同步整流驱动器的漏极电压检测脚d及nc悬空端,所述同步整流驱动脚位drv和mos管的栅极连接,所述同步整流驱动器的芯片地gnd和mos管的源极连接,所述同步整流管的供电脚位vcc接旁路电容到所述同步整流驱动器的芯片地gnd,所述同步整流驱动器的漏极电压检测脚d接mos管漏极。

2.如权利要求1所述的高性能高耐压的副边同步整流控制电路,其特征在于,所述同步整流驱动器的漏极电压检测脚d用于供电给所述同步整流管的供电脚位vcc。

3.如权利要求1所述的高性能高耐压的副边同步整流控制电路,其特征在于,所述mos管的drain与芯片的d脚之间电阻取值为5ω~20ω。

4.如权利要求1所述的高性能高耐压的副边同步整流控制电路,其特征在于,所述旁路电容紧靠所述同步整流管的供电脚位vcc和所述同步整流驱动器的芯片地gnd。

技术总结

一种高性能高耐压的副边同步整流控制电路,包括副边同步整流控制芯片,副边同步整流控制芯片包括同步整流驱动脚位DRV、同步整流驱动器的芯片地GND、同步整流管的供电脚位VCC、同步整流驱动器的漏极电压检测脚D及NC悬空端,同步整流驱动脚位DRV和MOS管的栅极连接,同步整流驱动器的芯片地GND和MOS管的源极连接,同步整流管的供电脚位VCC接旁路电容到同步整流驱动器的芯片地GND,同步整流驱动器的漏极电压检测脚D接MOS管漏极,可以有效避免因激磁振荡引起的驱动芯片误动作以及在CCM工作条件下纯电压判定的关断延迟造成的效率损失。

技术研发人员:曾长春

受保护的技术使用者:贵州中芯微电子科技有限公司

技术研发日:20230901

技术公布日:2024/4/22

- 还没有人留言评论。精彩留言会获得点赞!