高频电路以及通信装置的制作方法

1.本发明广泛涉及高频电路以及通信装置,更详细地,涉及具备放大电路的高频电路以及具备该高频电路的通信装置。

背景技术:

2.以往,已知具备功率放大电路和偏置电路的功率放大模块(例如,参照专利文献1)。

3.放大电路具备放大器。放大器具备发射极接地形式的晶体管。晶体管的集电极通过电感元件而与电源电压连接。

4.偏置电路具备发射极跟随器晶体管和控制ic。控制ic具备第1电流源和第2电流源。第1电流源将跟随控制电压的变化而变化的控制电流供给至发射极跟随器晶体管的集电极。第1电流源将控制电流限制在上限值以下。第2电流源将恒定电流供给至发射极跟随器晶体管的基极。

5.在先技术文献

6.专利文献

7.专利文献1:jp特开2018-152714号公报

技术实现要素:

8.发明要解决的问题

9.专利文献1记载的功率放大模块在电源电压高于额定电源电压的情况下,例如,由于发射极跟随器的h

fe

(输出短路电流增益)的偏差的影响,有时供给至放大器的晶体管的基极的偏置电流或偏置电压会产生偏差。因此,在专利文献1记载的功率放大模块中,有时放大电路和输入由放大电路放大后的高频信号的电子部件中的至少一者的特性会劣化。

10.本发明的目的在于,提供一种能够更高精度地限制放大电路的输出功率的高频电路以及通信装置。

11.用于解决问题的技术方案

12.本发明的一个方式涉及的高频电路具备放大电路、偏置电路、偏置控制电路、比较部、可变电阻电路和控制部。所述放大电路包含特定的晶体管。所述特定的晶体管具有输入端子以及输出端子,将输入到所述输入端子的高频信号放大并从所述输出端子输出。所述偏置电路向所述特定的晶体管的所述输入端子供给偏置电流或偏置电压。所述偏置控制电路向所述偏置电路供给控制电流或控制电压。所述比较部对与所述特定的晶体管的所述输出端子连接的电源端子的电源电压和阈值电压进行比较。所述可变电阻电路连接在所述电源端子与所述输出端子之间。所述可变电阻电路包含电阻元件和开关元件的并联电路。所述控制部根据所述比较部的比较结果对所述可变电阻电路的电阻值进行变更。

13.本发明的一个方式涉及的通信装置具备所述高频电路和信号处理电路。所述信号处理电路与所述高频电路连接。

14.发明效果

15.本发明的上述方式涉及的高频电路以及通信装置能够更高精度地限制放大电路的输出功率。

附图说明

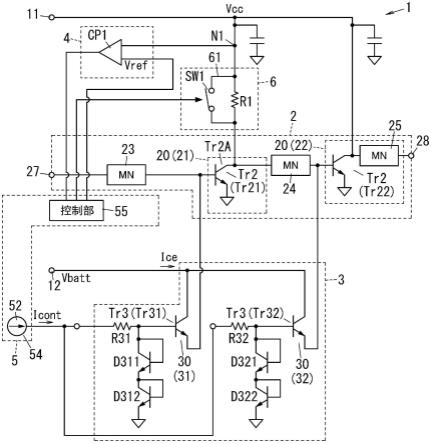

16.图1是具备实施方式涉及的高频电路的通信装置的电路图。

17.图2是同上的高频电路的电路图。

18.图3是具备实施方式的变形例1涉及的高频电路的通信装置的电路图。

具体实施方式

19.以下,参照图1以及图2对实施方式涉及的高频电路100以及通信装置300进行说明。

20.(1)高频电路以及通信装置

21.(1.1)高频电路以及通信装置的电路结构

22.高频电路100例如用于通信装置300。通信装置300例如是便携式电话(例如,智能电话),但不限于此,例如,也可以是可穿戴终端(例如,智能手表)。高频电路100例如是能够应对4g(第4代移动通信)标准、5g(第5代移动通信)标准的电路。4g标准例如是3gpp(third generation partnership project,第三代合作伙伴计划)lte(long term evolution,长期演进)标准。5g标准例如是5g nr(new radio,新空口)。高频电路100也可以是能够应对载波聚合以及双连接的电路。

23.高频电路100例如构成为能够将从信号处理电路301输入的发送信号放大并输出到天线310。信号处理电路301不是高频电路100的构成要素,而是具备高频电路100的通信装置300的构成要素。高频电路100例如通过通信装置300所具备的信号处理电路301来控制。通信装置300具备高频电路100和信号处理电路301。通信装置300还具备天线310。信号处理电路301例如包含rf信号处理电路302和基带信号处理电路303。rf信号处理电路302例如是rfic(radio frequency integrated circuit,射频集成电路),进行对高频信号的信号处理。rf信号处理电路302例如对从基带信号处理电路303输出的高频信号(发送信号)进行上变频等信号处理,并输出进行了信号处理的高频信号。基带信号处理电路303例如是bbic(baseband integrated circuit,基带集成电路)。基带信号处理电路303从基带信号生成i相信号以及q相信号。基带信号例如是从外部输入的声音信号、图像信号等。基带信号处理电路303通过对i相信号和q相信号进行合成来进行iq调制处理,输出发送信号。此时,发送信号被生成为调制信号(iq信号),该调制信号(iq信号)是对给定频率的载波信号以比该载波信号的周期长的周期进行了振幅调制而获得的信号。高频电路100在天线310与信号处理电路301的rf信号处理电路302之间传递高频信号(发送信号)。

24.高频电路100具备功率放大电路1。高频电路100还具备输出匹配电路101、第1开关102、滤波器103、第2开关104和天线端子105。

25.功率放大电路1具备放大电路2。放大电路2例如将从信号处理电路301经由高频电路100的信号输入端子13而输入的输入信号放大并输出。输入信号是给定频带的高频信号(发送信号)。给定频带例如包含相互不同的多个通信频段。放大电路2具有多个(例如,两

个)放大器20。

26.多个放大器20各自包含放大用的晶体管tr2(参照图2)。多个晶体管tr2各自具有输入端子以及输出端子。此外,多个晶体管tr2各自具有输入输出的公共端子。多个晶体管tr2各自例如为双极晶体管。在该情况下,晶体管tr2的输入端子、输出端子以及公共端子分别为双极晶体管的基极、集电极以及发射极。在放大电路2中,各晶体管tr2的公共端子(发射极)与接地连接(被接地)。

27.在放大电路2中,多个放大器20被多级连接。因此,在放大电路2中,多个晶体管tr2被多级连接。以下,为了方便说明,有时也将多个放大器20之中初级(驱动级)的放大器20称为初级放大器21,将最终级的放大器20称为最终级放大器22。此外,有时也将多个晶体管tr2之中初级(驱动级)的晶体管tr2称为初级晶体管tr21,将最终级(输出级)的晶体管tr2称为最终级晶体管tr22。

28.放大电路2还具备:设置在输入端子27与初级放大器21之间的匹配电路23、和设置在初级放大器21与最终级放大器22之间的匹配电路24。匹配电路23是用于取得初级放大器21和信号处理电路301的阻抗匹配的电路。匹配电路24是用于取得初级放大器21和最终级放大器22的阻抗匹配的电路(级间匹配电路)。

29.输出匹配电路101设置于放大电路2与第1开关102之间的信号路径。输出匹配电路101是用于取得放大电路2和滤波器103的阻抗匹配的电路。输出匹配电路101例如包含一个电感器,但不限于此,例如,也存在包含多个电感器以及多个电容器的情况。

30.第1开关102设置在输出匹配电路101与滤波器103之间。第1开关102具有公共端子和多个选择端子。第1开关102的公共端子经由输出匹配电路101而与放大电路2连接。第1开关102的多个选择端子之中的一个选择端子与滤波器103连接。第1开关102例如是能够将多个选择端子之中的至少一个以上连接于公共端子的开关。在此,第1开关102例如是能够进行一对一以及一对多的连接的开关。第1开关102是能够对通信频段相互不同的多个发送信号用的信号路径进行切换的开关。第1开关102例如按照从信号处理电路301输入的控制信号,对公共端子和多个选择端子的连接状态进行切换。第1开关102例如是开关ic(integrated circuit,集成电路)。

31.滤波器103是将上述的多个通信频段之中的至少一个通信频段(例如,band3)的发送频带作为通带的滤波器。滤波器103例如是单芯片的弹性波滤波器,多个串联臂谐振器以及多个并联臂谐振器各自由弹性波谐振器构成。弹性波滤波器例如是利用声表面波的声表面波滤波器。在声表面波滤波器中,多个串联臂谐振器以及多个并联臂谐振器各自例如是saw(surface acoustic wave,声表面波)谐振器。

32.第2开关104设置在滤波器103与天线端子105之间。第2开关104是与天线端子105连接的开关。第2开关104具有公共端子和多个选择端子。在第2开关104中,公共端子与天线端子105连接。在第2开关104的多个选择端子之中的一个选择端子连接了滤波器103。第2开关104例如按照从信号处理电路301输入的控制信号,对公共端子和多个选择端子的连接状态进行切换。第2开关104例如是开关ic。

33.天线端子105与天线310连接。

34.在高频电路100中,从放大电路2输出的发送信号通过输出匹配电路101、第1开关102、滤波器103、第2开关104以及天线端子105而从天线310被发送。

35.(1.2)功率放大电路的电路结构

36.如图2所示,功率放大电路1具备放大电路2、偏置电路3、偏置控制电路54、比较部4、可变电阻电路6和控制部55。放大电路2包含特定的晶体管tr2a(例如,初级的晶体管tr2)。特定的晶体管tr2a具有输入端子以及输出端子,将输入到输入端子的高频信号放大并从输出端子输出。偏置电路3向特定的晶体管tr2a的输入端子供给偏置电流,但不限于此,也可以是向特定的晶体管tr2a的输入端子供给偏置电压的结构。偏置控制电路54向偏置电路3供给控制电流icont,但不限于此,也可以是向偏置电路3供给控制电压的结构。比较部4对与特定的晶体管tr2a的输出端子连接的电源端子11的电源电压vcc和阈值电压(基准电压)vref进行比较。可变电阻电路6连接在电源端子11与特定的晶体管tr2a的输出端子之间。控制部55对可变电阻电路6进行控制。

37.放大电路2包含多个(例如,两个)放大用的晶体管tr2。

38.在放大电路2中,如上所述,多个晶体管tr2被多级连接。

39.放大电路2具有输入端子27以及输出端子28。在放大电路2中,初级晶体管tr21的输入端子(基极)经由匹配电路23而与放大电路2的输入端子27连接。初级晶体管tr21的输出端子(集电极)与电源端子11连接。此外,初级晶体管tr21的输出端子(集电极)经由匹配电路24而与最终级晶体管tr22的输入端子(基极)连接。初级晶体管tr21的公共端子(发射极)被接地。初级晶体管tr21将输入到输入端子的输入信号放大并从输出端子输出。

40.最终级晶体管tr22的输入端子(基极)经由匹配电路24而与初级晶体管tr21的输出端子(集电极)连接。最终级晶体管tr22的端子(集电极)与电源端子11连接。此外,最终级晶体管tr22的输出端子经由匹配电路24而与放大电路2的输出端子28连接。最终级晶体管tr22的公共端子(发射极)被接地。

41.放大电路2也可以具有设置在最终级晶体管tr22的输出端子与放大电路2的输出端子28之间的匹配电路25。

42.放大电路2将输入的发送信号利用初级晶体管tr21进行放大,进而利用最终级晶体管tr22进行放大并输出。也就是说,最终级晶体管tr22将由初级晶体管tr21放大后的发送信号进一步放大并输出。

43.偏置电路3具有与多个(在此为两个)晶体管tr2一一对应的多个(在此为两个)发射极跟随器30。两个发射极跟随器30各自包含双极晶体管tr3。两个发射极跟随器30各自向两个晶体管tr2之中对应的晶体管tr2的基极供给偏置电流。两个双极晶体管tr3是偏置用晶体管。

44.以下,关于两个发射极跟随器30,有时也将与初级晶体管tr21对应的发射极跟随器30称为第1发射极跟随器31,将与最终级晶体管tr22对应的发射极跟随器30称为第2发射极跟随器32。此外,关于两个双极晶体管tr3,有时也将包含于第1发射极跟随器31的双极晶体管tr3称为第1双极晶体管tr31,将包含于第2发射极跟随器32的双极晶体管tr3称为第2双极晶体管tr32。

45.第1双极晶体管tr31的基极经由电阻r31而与包含于偏置控制电路54的电流源52连接。第1双极晶体管tr31的发射极与初级晶体管tr21的输入端子(基极)连接。第1双极晶体管tr31的集电极与高频电路100所具有的电池端子12连接。第2双极晶体管tr32的基极经由电阻r32而与包含于偏置控制电路54的电流源52连接。第2双极晶体管tr32的发射极与最

终级晶体管tr22的输入端子(基极)连接。第2双极晶体管tr32的集电极与电池端子12连接。在偏置电路3中,来自电池端子12的电流ice被供给到多个双极晶体管tr3的集电极彼此的连接点。

46.如上所述,偏置控制电路54包含电流源52。电流源52输出控制电流icont。在功率放大电路1中,控制电流icont被供给到第1双极晶体管tr31的基极与第2双极晶体管tr32的基极的连接点。控制电流icont是恒定电流。

47.第1发射极跟随器31将作为对初级晶体管tr21的偏置点(动作点)进行控制的偏置信号的偏置电流从第1双极晶体管tr31的发射极供给到初级晶体管tr21的输入端子(基极)。

48.第2发射极跟随器32将作为对最终级晶体管tr22的偏置点(动作点)进行控制的偏置信号的偏置电流从第2双极晶体管tr32的发射极供给到最终级晶体管tr22的输入端子(基极)。

49.在包含于第1发射极跟随器31的第1双极晶体管tr31的基极与接地之间串联连接有两个二极管d311、d312。两个二极管d311、d312各自通过将npn型晶体管的基极和集电极连接而构成。

50.在包含于第2发射极跟随器32的第2双极晶体管tr32的基极与接地之间串联连接有两个二极管d321、d322。两个二极管d321、d322各自通过将npn型晶体管的基极和集电极连接而构成。

51.放大电路2以及偏置电路3例如包含于单芯片的ic芯片。包含放大电路2以及偏置电路3的ic芯片例如是gaas系ic芯片。在该情况下,两个晶体管tr2各自例如是hbt(heterojunction bipolar transistor,异质结双极晶体管)。

52.包含放大电路2以及偏置电路3的ic芯片不限于gaas系ic芯片,例如,也可以是具有放大电路2的si系ic芯片或者具有放大电路2的sige系ic芯片。

53.偏置控制电路54向偏置电路3供给控制电流icont。高频电路100具有包含偏置控制电路54的控制电路5。控制电路5例如是对放大电路2以及偏置电路3进行控制的控制ic(integrated circuit,集成电路)。在偏置电路3具有多个(在此为两个)发射极跟随器30的情况下,来自电池端子12的电流ice被分流到多个发射极跟随器30。来自偏置控制电路54的控制电流icont被分流到偏置电路3的两个双极晶体管tr3的基极。

54.比较部4对与特定的晶体管tr2a(在此为初级晶体管tr21)的输出端子(集电极)连接的电源端子11的电源电压vcc和阈值电压vref进行比较。电源端子11例如是与通信装置300(参照图1)所具备的电源ic(integrated circuit,集成电路)330连接并从电源ic330被供给电源电压vcc的端子。

55.比较部4包含对电源端子11的电源电压vcc和阈值电压vref进行比较的比较器cp1。比较器cp1具有第1输入端子以及第2输入端子、和输出端子。比较器cp1的第1输入端子连接在电源端子11与可变电阻电路6之间的节点n1。比较器cp1的第1输入端子不经由电路元件地与电源端子11连接。因此,在电源端子11与节点n1之间未设置电阻元件等产生电压降的电路元件。由此,在比较器cp1的第1输入端子施加电源电压vcc。在比较器cp1的第2输入端子从控制电路5所具有的控制部55施加阈值电压vref。比较器cp1的输出端子与控制部55连接。

56.在比较器cp1中,例如,第1输入端子是非反相输入端子,第2输入端子是反相输入端子。在比较部4中,在电源电压vcc未超过阈值电压vref的情况下,来自比较器cp1的输出端子的输出信号的信号电平(电压电平)是第1电平(也称为低电平)。此外,在比较部4中,在电源电压vcc超过了阈值电压vref的情况下,来自比较器cp1的输出端子的输出信号的信号电平成为比第1电平高的第2电平(也称为高电平)。

57.可变电阻电路6连接在电源端子11与特定的晶体管tr2a(初级晶体管tr21)的输出端子(集电极)之间。更详细地,可变电阻电路6连接在上述的节点n1与特定的晶体管tr2a的输出端子之间。

58.可变电阻电路6例如包含电阻元件r1和开关元件sw1的并联电路61。可变电阻电路6根据比较部4的比较结果来变更可变电阻电路6的电阻值。可变电阻电路6通过控制部55来控制。开关元件sw1例如是具有控制端子和一对主端子的半导体开关元件,在控制端子连接了控制部55,一对主端子之中的一个主端子与电阻元件r1的一端连接,另一个主端子与电阻元件r1的另一端连接。半导体开关元件例如是常导通型的mosfet(metal-oxide-semiconductor field effect transistor,金属氧化物半导体场效应晶体管)。

59.如上所述,控制电路5还具有对可变电阻电路6进行控制的控制部55。控制部55根据比较部4的比较结果对可变电阻电路6进行控制。也就是说,控制部55根据比较器cp1的输出信号对可变电阻电路6的开关元件sw1进行控制。控制部55在电源电压vcc大于阈值电压vref的情况下,与电源电压vcc小于阈值电压vref的情况相比,增大可变电阻电路6的电阻值。在高频电路100中,在比较器cp1的输出信号的信号电平为第1电平的情况下,控制部55将可变电阻电路6的开关元件sw1设为接通状态,在比较器cp1的输出信号的信号电平为第2电平的情况下,将可变电阻电路6的开关元件sw1控制为断开状态。因此,在可变电阻电路6中,在电源电压vcc小于阈值电压vref的情况下,可变电阻电路6的电阻值为大致零(开关元件sw1的导通电阻程度),在电源电压vcc大于阈值电压vref的情况下,可变电阻电路6的电阻值成为电阻元件r1的电阻值。电阻元件r1的电阻值大于开关元件sw1的导通电阻。阈值电压vref是比电源电压vcc的额定电源电压高给定电压(例如,0.1v以上且0.2v以下)的电压。

60.控制电路5以及比较器cp1例如包含于单芯片的ic芯片。包含控制电路5和比较器cp1的ic芯片例如是si系ic芯片。

61.控制电路5例如与信号处理电路301连接。控制电路5基于从信号处理电路301获取到的控制信号对放大电路2以及偏置电路3进行控制。控制电路5按照来自信号处理电路301的rf信号处理电路302的控制信号对放大电路2以及偏置电路3进行控制。

62.(1.3)高频电路的动作

63.在高频电路100中,功率放大电路1例如将来自信号处理电路301的发送信号放大并输出。在功率放大电路1中,放大电路2将输入的给定频带的发送信号即输入信号放大并输出。

64.在功率放大电路1中,在电源端子11的电源电压vcc为额定电源电压的情况下,电源电压vcc不超过阈值电压vref,比较器cp1的输出信号的信号电平成为第1电平。控制部55在比较器cp1的输出信号为第1电平的情况下,将可变电阻电路6的开关元件sw1设为接通状态。由此,在特定的晶体管tr2a施加与电源电压vcc大致相等的电压(比电源电压vcc小电源端子11与特定的晶体管tr2a的输出端子之间的路径中的电压降的量的电压)。

65.在功率放大电路1中,若电源端子11的电源电压vcc成为比额定电源电压高给定电压(例如,0.1v以上且0.2v以下)以上的电压,则电源电压vcc超过阈值电压vref,比较器cp1的输出信号的信号电平成为第2电平。若比较器cp1的输出信号成为第2电平,则控制部55将可变电阻电路6的开关元件sw1设为断开状态。由此,在特定的晶体管tr2a的输出端子(集电极)施加比电源电压vcc小电阻元件r1中的电压降的量的电压。因而,在功率放大电路1中,初级晶体管tr21的饱和输出功率受到限制,最终级晶体管tr22的输出功率受到限制。因此,在功率放大电路1中,放大电路2的输入功率-输出功率特性根据电源电压vcc和阈值电压vref的大小关系而不同。

66.(2)总结

67.(2.1)高频电路

68.实施方式涉及的高频电路100具备放大电路2、偏置电路3、偏置控制电路54、比较部4、可变电阻电路6和控制部55。放大电路2包含特定的晶体管tr2a。特定的晶体管tr2a具有输入端子以及输出端子,将输入到输入端子的高频信号放大并从输出端子输出。偏置电路3向特定的晶体管tr2a的输入端子供给偏置电流或偏置电压。控制电路5向偏置电路3供给控制电流icont或控制电压。比较部4对与特定的晶体管tr2a的输出端子连接的电源端子11的电源电压vcc和阈值电压vref进行比较。可变电阻电路6连接在电源端子11与特定的晶体管tr2a的输出端子之间。可变电阻电路6包含电阻元件r1和开关元件sw1的并联电路61。控制部55根据比较部4的比较结果对可变电阻电路6的电阻值进行变更。

69.实施方式涉及的高频电路100能够更高精度地限制放大电路2的输出功率。

70.此外,实施方式涉及的高频电路100在电源电压vcc大于阈值电压vref的情况下,限制向放大电路2的特定的晶体管tr2a的输出端子施加的电压,因此例如不易受到偏置电路3的特性的偏差的影响,能够更高精度地限制放大电路2的输出功率。偏置电路3的特性的偏差例如包含发射极跟随器30的h

fe

(输出短路电流增益)的偏差。

71.此外,实施方式涉及的高频电路100将包含于放大电路2的多个晶体管tr2之中初级的晶体管tr2作为特定的晶体管tr2a,并在特定的晶体管tr2a连接有可变电阻电路6,因此与在初级的晶体管tr21以外的晶体管tr2(在此为最终级的晶体管tr2)连接有可变电阻电路6的情况相比,能够抑制开关元件sw1为接通状态时的放大电路2的特性(输出功率、动作效率等)的下降。

72.具备高频电路100的高频模块具备包含于高频电路100的多个电路元件(功率放大电路1的gaas系ic芯片以及si系ic芯片、第1开关102、滤波器103、第2开关104等)和安装这些多个电路元件的安装基板。在高频模块中,在谋求高频模块的小型化的情况下,有时谋求多个电路元件之中安装基板上的占有面积容易变大的滤波器103的小型化。在此,滤波器103的耐电力处于随着滤波器103的芯片尺寸变小而下降的倾向。在实施方式涉及的高频电路100中,能够高精度地限制放大电路2的输出功率,因此例如能够抑制滤波器103的特性劣化,容易扩展滤波器103的设计余量(margin)。

73.(2.2)通信装置

74.实施方式涉及的通信装置300具备高频电路100和信号处理电路301。信号处理电路301与高频电路100连接。

75.实施方式涉及的通信装置300具备高频电路100,因此能够更高精度地限制放大电

路2的输出功率。

76.(3)变形例

77.(3.1)变形例1

78.参照图3对实施方式的变形例1涉及的高频电路100a以及通信装置300a进行说明。关于变形例1涉及的高频电路100a以及通信装置300a,对于与实施方式涉及的高频电路100以及通信装置300分别相同的构成要素,标注相同的符号并省略说明。

79.变形例1涉及的高频电路100a与实施方式涉及的高频电路100的不同点在于,取代实施方式涉及的高频电路100的功率放大电路1而具备功率放大电路1a。此外,变形例1涉及的通信装置300a与实施方式涉及的通信装置300的不同点在于,取代实施方式涉及的通信装置300所具备的高频电路100而具备高频电路100a。

80.功率放大电路1a取代功率放大电路1的可变电阻电路6而具备可变电阻电路6a。以下,为了方便说明,也将包含于可变电阻电路6a的、电阻元件r1和开关元件sw1的并联电路61中的电阻元件r1称为第1电阻元件r1,将并联电路61中的开关元件sw1称为第1开关元件sw1。可变电阻电路6a还包含至少一个与并联电路61并联连接的、第2开关元件sw2和第2电阻元件r2的串联电路62。作为一例,可变电阻电路6a包含n个(n为2以上的整数)串联电路62。以下,为了方便说明,有时也将n个第2开关元件sw2称为n个第2开关元件sw21~sw2n,将n个第2电阻元件r2称为n个第2电阻元件r21~r2n。因此,可变电阻电路6a具有n个第2开关元件sw21~sw2n和n个第2电阻元件r21~r2n。在可变电阻电路6a中,第1电阻元件r1的电阻值和n个第2电阻元件r21~r2n各自的电阻值设定为相同的值,但不限于此。此外,在可变电阻电路6a中,第1开关元件sw1的导通电阻和n个第2开关元件sw21~sw2n各自的导通电阻设定为相同的值,但不限于此。

81.在变形例1涉及的高频电路100a中,放大电路2与实施方式1涉及的高频电路100的放大电路2同样地,能够在相互不同的多个(例如,3个)通信频段(第1通信频段、第2通信频段、第3通信频段)中分别进行动作。因此,特定的晶体管tr2a能够在相互不同的多个通信频段中分别进行动作。在变形例1涉及的高频电路100a中,控制部55根据多个通信频段之中特定的晶体管tr2a进行动作的通信频段对可变电阻电路6a的电阻值进行变更。控制部55能够从信号处理电路301获取与特定的晶体管tr2a进行动作的通信频段相关的信息。控制部55例如能够基于比较部4的比较结果和来自信号处理电路301的包含与通信频段相关的信息的控制信号使可变电阻电路6a的电阻值变化。

82.在变形例1涉及的高频电路100a中,控制部55例如基于比较部4的比较结果,在电源电压vcc小于阈值电压vref的情况下,将第1开关元件sw1设为接通状态,将n个第2开关元件sw21~sw2n设为断开状态。控制部55例如基于比较部4的比较结果,在电源电压vcc大于阈值电压vref的情况下,如果根据第1通信频段将可变电阻电路6a的电阻值设定为最大值,则将第1开关元件sw1以及n个第2开关元件sw21~sw2n设为断开状态。此外,控制部55在电源电压vcc大于阈值电压vref的情况下,如果根据第2通信频段将可变电阻电路6a的电阻值设定为最小值,则将第1开关元件sw1设为断开状态,将n个第2开关元件sw21~sw2n设为接通状态。此外,控制部55在电源电压vcc大于阈值电压vref的情况下,如果根据第3通信频段将可变电阻电路6a的电阻值设定为最大值与最小值之间的值,则将第1开关元件sw1设为断开状态,仅将n个第2开关元件sw21~sw2n之中的一部分第2开关元件sw2设为接通状态。

83.变形例1涉及的高频电路100a在特定的晶体管tr2a进行动作的多个通信频段的任意一个中都能够更高精度地限制放大电路2的输出功率。

84.(3.2)变形例2

85.关于变形例2涉及的高频电路100,由于是与实施方式涉及的高频电路100相同的电路结构,因此参照图1以及2进行说明。

86.在变形例2涉及的高频电路100中,控制部55获取与施加于电源端子11的电源电压vcc的额定电源电压相关的信息,并基于该信息对阈值电压vref进行变更。控制部55例如从信号处理电路301获取与电源电压vcc的额定电源电压相关的信息。更详细地,控制部55获取包含于来自信号处理电路301的控制信号(指令)的、与电源电压vcc的额定电源电压相关的信息。

87.在变形例2涉及的高频电路100中,控制部55例如基于获取到的额定电源电压的信息,额定电源电压越大,则越增大阈值电压vref。

88.在变形例2涉及的高频电路100中,例如,在施加于电源端子11的电源电压vcc的额定电源电压的规格发生了变更的情况下,能够根据额定电源电压对阈值电压vref进行变更。

89.(其他的变形例)

90.上述的实施方式只不过是本发明的各种各样的实施方式之一。上述的实施方式只要能够达成本发明的目的,就能够根据设计等进行各种变更。

91.例如,在高频电路100、100a中,将放大电路2中的晶体管tr2的连接级数设为了2,但不限于此,晶体管tr2的连接级数也可以设为3以上。此外,放大电路2不限定于具有多个晶体管tr2的结构,只要具有至少一个晶体管tr2即可。总之,在高频电路100、100a中,晶体管tr2的数量可以为一个,在该情况下,偏置电路3的发射极跟随器30以及双极晶体管tr3的数量也可以为一个。在高频电路100、100a中,将初级晶体管tr21作为特定的晶体管tr2a,但不限于此,也可以将最终级晶体管tr22作为特定的晶体管tr2a,还可以将初级晶体管tr21以及最终级晶体管tr22分别作为特定的晶体管tr2a。此外,在晶体管tr2的连接级数为3以上的情况下,也可以将初级晶体管tr21和最终级晶体管tr22这两者以外的晶体管tr2作为特定的晶体管tr2a。

92.此外,放大电路2中的晶体管tr2不限于双极晶体管,也可以是fet(field effect transistor,场效应晶体管)。在晶体管tr2为fet的情况下,栅极、漏极以及源极分别成为输入端子、输出端子以及公共端子。

93.在高频电路100、100a中,例如,第1开关102、滤波器103以及第2开关104并不是必须的构成要素,而是附加的构成要素。

94.此外,在高频电路100中,滤波器103是利用声表面波的弹性波滤波器,但不限于此,例如,也可以是利用声边界波、板波等的弹性波滤波器。

95.在弹性波滤波器中,多个串联臂谐振器以及多个并联臂谐振器各自不限于saw谐振器,例如,也可以是baw(bulk acoustic wave,体声波)谐振器。

96.高频电路100、100a也可以具备接收电路,该接收电路包含对从天线端子105输入的接收信号进行放大的低噪声放大器以及与低噪声放大器连接的滤波器。

97.此外,滤波器103不限于发送滤波器,也可以是双工器。

98.此外,在高频电路100、100a中,第1开关102以及第2开关104例如也可以是应对gpio(general purpose input/output,通用输入/输出)的开关ic。

99.(方式)

100.在本说明书中公开了以下的方式。

101.第1方式涉及的高频电路(100;100a)具备放大电路(2)、偏置电路(3)、偏置控制电路(54)、比较部(4)、可变电阻电路(6;6a)和控制部(55)。放大电路(2)包含特定的晶体管(tr2a)。特定的晶体管(tr2a)具有输入端子以及输出端子,将输入到输入端子的高频信号放大并从输出端子输出。偏置电路(3)向特定的晶体管(tr2a)的输入端子供给偏置电流或偏置电压。偏置控制电路(54)向偏置电路(3)供给控制电流(icont)或控制电压。比较部(4)对与特定的晶体管(tr2a)的输出端子连接的电源端子(11)的电源电压(vcc)和阈值电压(vref)进行比较。可变电阻电路(6;6a)连接在电源端子(11)与输出端子之间。可变电阻电路(6;6a)包含电阻元件(r1)和开关元件(sw1)的并联电路(61)。控制部(55)根据比较部(4)的比较结果对可变电阻电路(6;6a)的电阻值进行变更。

102.第1方式涉及的高频电路(100;100a)能够更高精度地限制放大电路(2)的输出功率。

103.在第2方式涉及的功率放大电路(100;100a)中,在第1方式中,控制部(55)在电源电压(vcc)大于阈值电压(vref)的情况下,与电源电压(vcc)小于阈值电压(vref)的情况相比,增大可变电阻电路(6;6a)的电阻值。

104.在第2方式涉及的高频电路(100;100a)中,在电源电压(vcc)大于阈值电压(vref)的情况下,能够高精度地限制放大电路(2)的输出功率。

105.在第3方式涉及的高频电路(100a)中,在第2方式中,将并联电路(61)的电阻元件(r1)作为第1电阻元件,将并联电路(61)的开关元件(sw1)作为第1开关元件。可变电阻电路(6a)还包含至少一个与并联电路(61)并联连接的、第2开关元件(sw2)和第2电阻元件(r2)的串联电路(62)。

106.在第3方式涉及的高频电路(100a)中,在电源电压(vcc)大于阈值电压(vref)的情况下,能够更高精度地限制放大电路(2)的输出功率。

107.在第4方式涉及的高频电路(100a)中,在第1方式~第3方式的任一者中,特定的晶体管(tr2a)能够在相互不同的多个通信频段中分别进行动作。控制部(55)根据多个通信频段之中特定的晶体管(tr2a)进行动作的通信频段对可变电阻电路(6a)的电阻值进行变更。

108.在第4方式涉及的高频电路(100a)中,能够根据特定的晶体管(tr2a)进行动作的通信频段来更高精度地限制放大电路(2)的输出功率。

109.在第5方式涉及的高频电路(100;100a)中,在第1方式~第4方式的任一者中,控制部(55)获取与电源端子(11)的额定电源电压相关的信息并基于上述信息对阈值电压(vref)进行变更。

110.在第5方式涉及的高频电路(100;100a)中,例如,在施加于电源端子(11)的电源电压(vcc)的额定电源电压的规格发生了变更的情况下,能够根据额定电源电压对阈值电压(vref)进行变更。

111.在第6方式涉及的高频电路(100;100a)中,在第1方式~第5方式的任一者中,比较部(4)包含对电源端子(11)的电源电压(vcc)和阈值电压(vref)进行比较的比较器(cp1)。

控制部(55)根据比较器(cp1)的输出对可变电阻电路(6;6a)的电阻值进行变更。

112.在第6方式涉及的高频电路(100;100a)中,相比于利用电阻分压电路对电源端子(11)的电源电压(vec)进行电阻分压并与阈值电压进行比较的情况,能够减少电源端子(11)与特定的晶体管(tr2a)的输出端子之间的电压降,能够抑制放大电路(2)的输出功率的下降以及动作效率的下降。

113.在第7方式涉及的高频电路(100;100a)中,在第1方式~第6方式的任一者中,放大电路(2)包含特定的晶体管(tr2a)在内具有多个晶体管(tr2)。在放大电路(2)中,多个晶体管(tr2)被多级连接。

114.在第7方式涉及的高频电路(100;100a)中,能够增大放大电路(2)的输出功率。

115.在第8方式涉及的高频电路(100;100a)中,在第7方式中,特定的晶体管(tr2a)是多个晶体管(tr2)之中除了最终级的晶体管(tr2)以外的一个晶体管(tr2)。

116.在第8方式涉及的高频电路(100;100a)中,与在最终级的晶体管(tr2)连接有可变电阻电路(6;6a)的情况相比,能够抑制开关元件(sw1)为接通状态时的放大电路(2)的特性(输出功率、动作效率等)的下降。

117.在第9方式涉及的高频电路(100;100a)中,在第8方式中,特定的晶体管(tr2)是多个晶体管(tr2)之中初级的晶体管(tr2)。

118.在第9方式涉及的高频电路(100;100a)中,与在初级的晶体管(tr2)以外的晶体管(tr2)连接有可变电阻电路(6;6a)的情况相比,能够抑制开关元件(sw1)为接通状态时的放大电路(2)的特性(输出功率、动作效率等)的下降。

119.第10方式涉及的通信装置(300;300a)具备第1方式~第9方式的任一个高频电路(100;100a)和信号处理电路(301)。信号处理电路(301)与高频电路(100;100a)连接。

120.第10方式涉及的通信装置(300;300a)能够更高精度地限制放大电路(2)的输出功率。

121.符号说明

122.1、1a 功率放大电路;

123.2 放大电路;

124.20 放大器;

125.21 初级放大器;

126.22 最终级放大器;

127.23 匹配电路;

128.24 匹配电路;

129.25 匹配电路;

130.27 输入端子;

131.28 输出端子;

132.3 偏置电路;

133.30 发射极跟随器;

134.31 第1发射极跟随器;

135.32 第2发射极跟随器;

136.4 比较部;

137.5 控制电路;

138.52 电流源;

139.54 偏置控制电路;

140.55 控制部;

141.6、6a 可变电阻电路;

142.61 并联电路;

143.62 串联电路;

144.11 电源端子;

145.12 电池端子;

146.100、100a 高频电路;

147.101 输出匹配电路;

148.102 第1开关;

149.103 滤波器;

150.104 第2开关;

151.105 天线端子;

152.300、300a 通信装置;

153.301 信号处理电路;

154.302 rf信号处理电路;

155.303 基带信号处理电路;

156.310 天线;

157.330 电源ic;

158.cp1 比较器;

159.d311、d312、d321、d322 二极管;

160.ice 电流;

161.icont 控制电流;

162.r1 电阻元件(第1电阻元件);

163.r2、r21~r2n 第2电阻元件;

164.r31 电阻;

165.r32 电阻;

166.sw1 开关元件(第1开关元件);

167.sw2 第2开关元件;

168.tr2 晶体管;

169.tr21 初级晶体管;

170.tr22 最终级晶体管;

171.tr2a 特定的晶体管;

172.tr3 双极晶体管;

173.tr31 第1双极晶体管;

174.tr32 第2双极晶体管;

175.vcc 电源电压;

176.vbatt 电池电压;

177.vref 阈值电压。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1