一种基于小范围死区产生模块架构的亚采样锁相环

1.本发明涉及新一代信息技术,尤其涉及一种基于小范围死区产生模块架构的亚采样锁相环。

背景技术:

2.锁相环广泛应用于众多高端、高性能的集成电路芯片比如中央处理器,高速高精度模数数模转换器,高性能光通信及无线射频通信芯片。在传统的锁相环系统中,由于反馈回路中分频器的存在,来自鉴频鉴相器和电荷泵的噪声被乘以n2,其中n为分频器的分频比,从而导致锁相环系统整体的噪声性能变差。

3.相对于传统的锁相环系统,亚采样锁相环基于一个亚采样原理的鉴相器,用低频的参考时钟信号去采样高频的压控振荡器输出信号来获得二者之间的相位差。由于亚采样能等效的把参考时钟信号的频率放大n倍,这个全新的锁相环在反馈回路中不再需要分频器来维持参考时钟信号和压控振荡器输出信号之间的频率关系,由于反馈回路中不存在分频器,则来自鉴相器和电荷泵的噪声不会被乘以n2,从而提升系统噪声性能。

4.虽然亚采样锁相环具有非常优越的相位噪声性能,但是在亚采样鉴相器中,参考时钟信号对压控振荡器的输出信号进行直接采样。由于压控振荡器输出信号本身正弦曲线的特性,则亚采样鉴相器的鉴相范围为(-t

vco

/2,t

vco

/2),其中t

vco

为压控振荡器输出信号的周期。在时间域,压控振荡器的输出频率一般都很高,所以周期很短,因此亚采样鉴相器的捕获范围非常小。在外部干扰的作用下,干扰通常来自于压控振荡器的电源或者衬底的耦合作用,通常会超出亚采样鉴相器的捕获范围。由于亚采样鉴相器本身的缺陷,并不能分辨所需锁定频率以及其谐波分量,不能锁定在正确的频率上。由于频率锁定回路中死区的存在,需要一定时间去积累相位误差,当相位误差超出死区范围后,此时频率锁定回路开启,由于频率锁定回路的作用,系统最终还是可以恢复锁定状态。但是由于死区的必然存在,需要较长的时间积累相位误差以打开死区,导致重新锁定需要较长的时间,这在许多的应用中是不可接受的。

5.现有技术中出现了文件cn 114978160 a《一种快速锁定的亚采样锁相环及锁相方法》对重新锁定时间进行缩减,但其也只能将时间控制在0.4μs的水平,仍然不能满足要求日益提高的高精度系统使用。

技术实现要素:

6.本发明目的在于提供一种基于小范围死区产生模块架构的亚采样锁相环,以解决上述现有技术存在的问题。

7.本发明中所述一种基于小范围死区产生模块架构的亚采样锁相环,包括:

8.压控振荡器,用于生成振荡信号f

vco

;

9.参考时钟,用于生成参考信号f

ref

;

10.亚采样回路,接收所述振荡信号f

vco

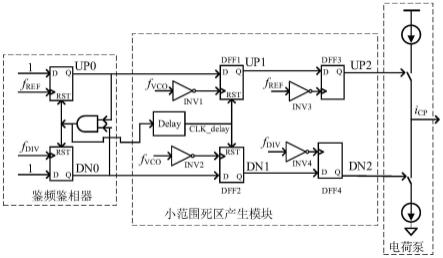

和参考信号f

ref

并对环路滤波器输出锁相信

号;

11.频率锁定回路,用于接收所述振荡信号f

vco

并进行初始频率锁定;包括鉴频鉴相器、小范围死区产生模块、电荷泵和分频器,所述分频器输入端连接所述压控振荡器输出端,分频器的分频信号f

div

连接所述鉴频鉴相器,所述鉴频鉴相器的输出端连接所述小范围死区产生模块后再经过所述电荷泵连接环路滤波器;

12.当所述振荡信号f

vco

和参考信号f

ref

之间的相位误差大于等于阈值时,所述小范围死区产生模块对环路滤波器输出锁频信号;当所述振荡信号f

vco

和参考信号f

ref

之间的相位误差小于阈值时,所述小范围死区产生模块不使能;

13.环路滤波器,用于接收所述锁相信号和所述锁频信号并控制所述压控振荡器振荡;

14.所述小范围死区产生模块还接收所述振荡信号f

vco

以缩减死区的时间跨度。

15.所述小范围死区产生模块包括第一d触发器dff1、第二d触发器dff2、第三d触发器dff3、第四d触发器dff4、第一反相器inv1、第二反相器inv2、第三反相器inv3、第四反相器inv4和延时单元delay;

16.所述第一d触发器dff1的置数信号输入端连接所述鉴频鉴相器的充电信号输出端,所述第一d触发器dff1的控制时钟信号输入端连接所述第一反相器inv1的信号输出端,所述第一d触发器dff1的信号输出端连接所述第三d触发器dff3的置数信号输入端,所述第三d触发器dff3的控制时钟信号输入端连接所述第三反相器inv3的信号输出端,所述第三d触发器dff3的信号输出端连接电荷泵的充电信号输入端;

17.所述第二d触发器dff2的置数信号输入端连接所述鉴频鉴相器的放电信号输出端,所述第二d触发器dff2的控制时钟信号输入端连接所述第二反相器inv2的信号输出端,所述第二d触发器dff2的信号输出端连接所述第四d触发器dff4的置数信号输入端,所述第四d触发器dff4的控制时钟信号输入端连接所述第四反相器inv4的信号输出端,所述第四d触发器dff4的信号输出端连接电荷泵的放电信号输入端;

18.所述第一反相器inv1和第二反相器inv2的输入端均连接所述振荡信号f

vco

,所述第三反相器inv3的输入端连接所述参考信号f

ref

,所述第四反相器inv4的输入端连接所述分频信号f

div

;

19.所述延时单元delay的输入端连接所述鉴频鉴相器的复位信号,输出端分别连接所述第一d触发器dff1的复位输入端和所述第二d触发器dff2的复位输入端。

20.所述延时单元delay的延时时间为m*t

vco

;其中t

vco

表示压控振荡器的信号周期,m为正数。

21.所述阈值为π*(n-2*m)/n,其中n是分频器的分频比。

22.本发明中所述一种基于小范围死区产生模块架构的亚采样锁相环,其优点在于,引入振荡信号f

vco

和延时复位作为调整参数,使得死区的时间长度大大缩减,重新锁定过程可以低至0.14μs。

附图说明

23.图1是本发明中所述亚采样锁相环的结构示意图。

24.图2是本发明中所述小范围死区产生模块的结构示意图。

25.图3是本发明中所述亚采样锁相环在参考时钟信号上升沿领先分频器信号上升沿不小于阈值时的时序图。

26.图4是本发明中所述亚采样锁相环在参考时钟信号上升沿领先分频器信号上升沿小于阈值时的时序图。

27.图5是本发明中所述亚采样锁相环的锁定过程示意图。

具体实施方式

28.如图1、图2所示,本发明中所述一种基于小范围死区产生模块架构的亚采样锁相环主要包括压控振荡器、参考时钟、亚采样回路、频率锁定回路和环路滤波器

29.压控振荡器,用于生成振荡信号f

vco

。

30.参考时钟,用于生成参考信号f

ref

。

31.亚采样回路,接收所述振荡信号f

vco

和参考信号f

ref

并对环路滤波器输出锁相信号。

32.频率锁定回路,用于接收所述振荡信号f

vco

并进行初始频率锁定。包括鉴频鉴相器、小范围死区产生模块、电荷泵和分频器,所述分频器输入端连接所述压控振荡器输出端,分频器的分频信号f

div

连接所述鉴频鉴相器,所述鉴频鉴相器的输出端连接所述小范围死区产生模块后再经过所述电荷泵连接环路滤波器。

33.当所述振荡信号f

vco

和参考信号f

ref

之间的相位误差大于等于阈值时,所述小范围死区产生模块对环路滤波器输出锁频信号。当所述振荡信号f

vco

和参考信号f

ref

之间的相位误差小于阈值时,所述小范围死区产生模块不使能。

34.环路滤波器,用于接收所述锁相信号和所述锁频信号并控制所述压控振荡器振荡。

35.所述小范围死区产生模块还接收所述振荡信号f

vco

以缩减死区的时间跨度。

36.所述小范围死区产生模块包括第一d触发器dff1、第二d触发器dff2、第三d触发器dff3、第四d触发器dff4、第一反相器inv1、第二反相器inv2、第三反相器inv3、第四反相器inv4和延时单元delay。

37.所述第一d触发器dff1的置数信号输入端连接所述鉴频鉴相器的充电信号输出端,所述第一d触发器dff1的控制时钟信号输入端连接所述第一反相器inv1的信号输出端,所述第一d触发器dff1的信号输出端连接所述第三d触发器dff3的置数信号输入端,所述第三d触发器dff3的控制时钟信号输入端连接所述第三反相器inv3的信号输出端,所述第三d触发器dff3的信号输出端连接电荷泵的充电信号输入端。

38.所述第二d触发器dff2的置数信号输入端连接所述鉴频鉴相器的放电信号输出端,所述第二d触发器dff2的控制时钟信号输入端连接所述第二反相器inv2的信号输出端,所述第二d触发器dff2的信号输出端连接所述第四d触发器dff4的置数信号输入端,所述第四d触发器dff4的控制时钟信号输入端连接所述第四反相器inv4的信号输出端,所述第四d触发器dff4的信号输出端连接电荷泵的放电信号输入端。

39.所述第一反相器inv1和第二反相器inv2的输入端均连接所述振荡信号f

vco

,所述第三反相器inv3的输入端连接所述参考信号f

ref

,所述第四反相器inv4的输入端连接所述分频信号f

div

。

40.所述延时单元delay的输入端连接所述鉴频鉴相器的复位信号,输出端分别连接所述第一d触发器dff1的复位输入端和所述第二d触发器dff2的复位输入端。

41.本发明中所述一种基于小范围死区产生模块架构的亚采样锁相环工作原理如下:

42.所述小范围死区产生模块根据参考信号f

ref

与分频信号f

div

之间的相位差,来控制输出信号up2和dn2的状态,进而控制后级电荷泵进行充电或者放电操作。

43.如图3所示,当参考信号f

ref

的上升沿领先分频信号f

div

的上升沿大于等于时,此时相应的相位误差为:

[0044][0045]

式中δt表示参考信号f

ref

上升沿与分频信号f

div

上升沿之间的时间差,t

ref

表示参考信号的周期,t

vco

表示压控振荡器的信号周期。此时相位误差大于等于在δt时间内,up0信号置1,dn0信号置0。第一d触发器dff1中f

vco

信号的下降沿采集到up0信号的1状态,使第一d触发器dff1的输出up1信号置1。第三d触发器dff3中f

ref

信号的下降沿采集到up1信号的1状态,使第三d触发器dff3的输出up2信号置1。第二d触发器dff2中f

vco

信号的下降沿采集到dn0信号的0状态,使第二d触发器dff2的输出dn1信号置0。第四d触发器dff4中f

div

信号的下降沿采集到dn1信号的0状态,使第四d触发器dff4的输出dn2信号置0。此时小范围死区产生模块控制后级电荷泵进行充电操作,即开启频率锁定回路,确保系统锁定到正确频率。

[0046]

同理,当分频信号f

div

的上升沿领先参考信号f

ref

的上升沿大于等于时,即相位误差大于等于此时up2信号置0,dn2信号置1,小范围死区产生模块控制后级电荷泵进行放电操作,即开启频率锁定回路,确保系统锁定到正确频率。

[0047]

如图4所示,当参考信号f

ref

的上升沿领先分频信号f

div

的上升沿小于时,即相位误差小于在δt时间内,up0信号置1,dn0信号置0。但是由于相位误差小于第一d触发器dff1中f

vco

信号的下降沿只能采集到up0信号的0状态,使第一d触发器dff1的输出up1信号置0。第三d触发器dff3中f

ref

信号的下降沿采集到up1信号的0状态,使第三d触发器dff3的输出up2信号置0。第二d触发器dff2中f

vco

信号的下降沿采集到dn0信号的0状态,使第二d触发器dff2的输出dn1信号置0。第四d触发器dff4中f

div

信号的下降沿采集到dn1信号的0状态,使第四d触发器dff4的输出dn2信号置0。此时up2信号和dn2信号都为0,后级电荷泵不产生充放电电流,频率锁定回路关闭。

[0048]

同理,当分频信号f

div

的上升沿领先参考信号f

ref

的上升沿小于时,即相位误差小于此时up2和dn2信号同样都置0,后级电荷泵不产生充放电电流,频率锁定回路关闭。

[0049]

图5展示了本发明中所述亚采样锁相环的锁定过程,当受到外部干扰时,其死区范

围为只需要很短的时间,约0.14μs就可以开启频率锁定回路,确保系统锁定在正确频率,重新锁定时间大大减小。

[0050]

对于本领域的技术人员来说,可根据以上描述的技术方案以及构思,做出其它各种相应的改变以及形变,而所有的这些改变以及形变都应该属于本发明权利要求的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1