光检测装置的制作方法

光检测装置

1.本技术是中国专利申请第201780001823.8号的分案申请,第201780001823.8号的专利申请的申请日是2017年2月27日,发明名称是“固态摄像元件、电子设备和固态摄像元件的控制方法”。

技术领域

2.本发明涉及固态摄像元件、电子设备和该固态摄像元件的控制方法。具体地,本发明涉及差分放大型固态摄像元件、电子设备和该固态摄像元件的控制方法。

背景技术:

3.自从过去以来,已在摄像器件中使用通过对光进行光电转换来产生图像数据的固态摄像元件。例如,已提出了一种为增加灵敏度而利用一对晶体管来放大差分信号的差分放大型(differntial amplification

‑

type)固态摄像元件(例如,参照专利文献1)。在这种差分放大型固态摄像元件中布置有单位像素和虚设像素,从单位像素读取像素信号,且不从虚设像素读取信号。另外,包含在固态摄像元件中的读出电路读取被差分对(differential pair)差分放大的像素信号,并且对其执行相关双重采样处理(cds:correlated double sampling),其中,差分对由包含在单位像素中的放大晶体管和包含在虚设像素中的放大晶体管形成。

4.此处,cds处理是通过从像素中读取两次信号并获取这些信号的电平之间的差值作为像素数据来减少固定模式噪声的处理。将第一次读取的信号电平称为p相电平,且将第二次读取的信号电平称为d相电平。

5.引用列表

6.专利文献

7.专利文献1:jp 2008

‑

271280a

技术实现要素:

8.技术问题

9.在上述的相关技术中,读出电路输出p相电平和d相电平之间的差值的数据,以作为具有与曝光量对应的值的像素数据。然而,对于相关技术,存在着在强光入射的情况下出现黑点现象(black dot phenomenon)的可能性,在这种情况下,尽管存在入射光,光的像素数据依然趋近于靠近“0”(黑色电平)的值。出现黑点现象的原因在于,由于强光而在光电二极管中产生了大量的电荷,并且电荷可能泄露到浮动扩散层中,由此导致p相电平增加并因此在p相位和d相电平之间大体上不存在差值。

10.考虑到上述情况,本发明旨在防止在差分放大型固态摄像元件中产生黑点现象。

11.技术方案

12.本发明用于解决上述问题,并且本发明的第一个方面涉及固态摄像元件及其控制方法,固态摄像元件包括:信号侧放大晶体管,其用于通过将与一对差分输入电压中的一者

相对应的信号电流从输出节点提供至公共相位节点来产生与信号电流相对应的输出电压;参考侧放大晶体管,其用于将与一对差分输入电压中的另一者相对应的参考电流提供至公共相位节点;恒定电流源,其用于恒定地控制在公共相位节点处汇合的信号电流和参考电流的总和;和旁路控制单元,旁路控制单元用于连接输出节点和公共相位节点,且在输出电压达到预定的限制电压的情况下将具有与限制电压相对应的值的信号电流提供至公共相位节点。于是,在输出电压达到预定的限制电压的情况下表现出连接输出节点和公共相位节点的效果。

13.此外,根据第一方面,还可以包括信号处理单元,信号处理单元用于通过读取来自有效像素电路和虚设像素电路之中的有效像素电路的信号来执行预定的信号处理。信号侧放大晶体管布置在有效像素电路中,且参考侧放大晶体管布置在虚设像素电路中。于是,在有效像素电路的输出电压达到预定的限制电压时表现出连接输出节点和公共相位节点的效果。

14.另外,根据第一方面,虚设像素电路可以被遮光。于是,在没有被遮光的有效像素电路的输出电压达到预定的限制电压时表现出连接输出节点和公共相位节点的效果。

15.另外,根据第一方面,虚设像素电路可以不被遮光且可以设置成邻近有效像素电路。于是,在邻近虚设像素电路的有效像素电路的输出电压达到预定的限制电压时表现出连接输出节点和公共相位节点的效果。

16.另外,根据第一方面,旁路控制单元可以旁路晶体管,旁路晶体管的源极连接到输出节点。于是,表现出通过旁路晶体管连接输出节点和公共相位节点的效果。

17.另外,根据第一方面,所述信号侧放大晶体管可以输出作为输出电压的p相电平,并然后输出作为输出电压的不同于p相电平的d相电平。限制电压可以包括用于限制p相电平的p相限制电压和用于限制d相电平的d相限制电压。于是,表现出限制p相电平和d相电平的效果。

18.另外,根据第一方面,旁路控制单元还可以包括并联地与旁路晶体管连接的第一电阻元件和第二电阻元件。旁路晶体管的栅极和漏极可以短接。第一电阻元件的电阻值可以是对应于p相限制电压的值,且第二电阻元件的电阻值可以是对应于d相限制电压的值。于是,表现出使用对应于第一和第二电阻元件的电阻值的限制电压来限制p相电平和d相电平的效果。

19.另外,根据第一方面,旁路晶体管可以包括具有不同的阈值电压的第一旁路晶体管和第二旁路晶体管。所述第一旁路晶体管的栅极和漏极可以短接,且所述第二旁路晶体管的栅极和漏极可以短接。第一旁路晶体管的阈值电压可以是对应于p相限制电压的值,并且第二旁路晶体管的阈值电压可以是对应于d相限制电压的值。于是,表现出利用对应于第一和第二旁路晶体管的阈值电压的限制电压来限制p相电平和d相电平的效果。

20.另外,根据第一方面,旁路控制单元还可以包括选择器,选择器用于选择电源电压、第一偏置电压和第二偏置电压中的一者,且将所选择的电压提供至旁路晶体管的栅极,第一偏置电压和第二偏置电压彼此不同。第一偏置电压可以是对应于p相限制电压的值,且第二偏置电压可以是对应于d相限制电压的值。于是,表现出利用对应于第一和第二偏置电压的限制电压来限制p相电平和d相电平的效果。

21.另外,本发明的第二方面涉及电子设备,该电子设备包括:信号侧放大晶体管,其

用于通过将与一对差分输入电压中的一者相对应的信号电流从输出节点提供至公共相位节点来产生与信号电流相对应的输出电压;参考侧放大晶体管,其用于将与一对差分输入电压中的另一者相对应的参考电流提供至公共相位节点;恒定电流源,其用于恒定地控制在公共相位节点处汇合的信号电流和参考电流的总和;旁路控制单元,其用于连接输出节点和公共相位节点,并且在输出电压达到预定的限制电压的情况下将具有与限制电压相对应的值的信号电流提供至公共相位节点;和图像信号处理单元,其用于对根据输出电压的信号产生的图像数据执行预定的图像处理。于是,在输出电压达到预定的限制电压的情况下表现出连接输出节点和公共相位节点的效果。

22.技术效果

23.根据本发明,差分放大型固态摄像元件表现出良好的防止黑点现象的效果。同时,此处描述的效果没有必要是限制性的,并且可以是本技术中描述的效果。

附图说明

24.图1是示出根据本发明的第一实施例的电子设备的构造示例的框图。

25.图2是示出根据本发明的第一实施例的固态摄像元件的构造示例的框图。

26.图3是示出根据本发明的第一实施例的像素阵列单元的构造示例的框图。

27.图4是示出根据本发明的第一实施例的差分放大电路的构造示例的电路图。

28.图5是示出根据本发明的第一实施例的列信号处理单元的构造示例的框图。

29.图6是示出根据本发明的第一实施例的在限制之前在差分放大电路中流动的电流的示例的示图。

30.图7是示出根据本发明的第一实施例的在限制之后在差分放大电路中流动的电流的示例的示图。

31.图8是示出根据本发明的第一实施例的像素电路的驱动操作的示例的时序图。

32.图9是示出根据本发明的第一实施例的固态摄像元件的操作示例的流程图。

33.图10是示出根据本发明的第一实施例的第一变形例的差分放大电路的构造示例的电路图。

34.图11是示出根据本发明的第一实施例的第二变形例的差分放大电路的构造示例的图。

35.图12是示出根据本发明的第一实施例的第二变形例的像素电路的驱动操作的示例的时序图。

36.图13是示出根据本发明的第二实施例的固态摄像元件的构造示例的框图。

37.图14是示出根据本发明的第二实施例的像素阵列单元的构造示例的框图。

38.图15是示出根据本发明的第二实施例的差分放大电路的构造示例的电路图。

39.图16是示出根据本发明的第二实施例的奇数行像素电路的驱动操作的示例的时序图。

40.图17是示出根据本发明的第二实施例的偶数行像素电路的驱动操作的示例的时序图。

具体实施方式

41.下面将描述用于实施本发明的示例性实施例(以下将被称为实施例)。将按以下顺序提供说明。

42.1.第一实施例(连接输出节点和公共相位节点的示例)

43.2.第二实施例(通过使有效像素和虚设像素接近来连接输出节点和公共相位节点的示例)

44.<1.第一实施例>

45.[电子设备的构造示例]

[0046]

图1是示出根据第一实施例的电子设备100的构造示例的框图。电子设备100是产生图像数据的设备,并且包括摄像透镜110、固态摄像元件200、数字信号处理器120、帧存储器130、记录装置140、显示装置150、电源电路160、操作电路170以及总线180。可以将包括数字摄像机、摄像机模块等在内的移动设备视为电子设备100。

[0047]

摄像透镜110聚集光并将光引导到固态摄像元件200。固态摄像元件200将从摄像透镜110入射的光进行光电转换以在数字信号处理器120的控制下生成图像数据。该固态摄像元件200经由信号线209将图像数据提供至数字信号处理器120。

[0048]

数字信号处理器120对图像数据执行预定图像处理。数字信号处理器120控制固态摄像元件200,由此根据按下快门按钮等的操作来生成图像数据。然后,数字信号处理器120在必要时使用帧存储器130执行对图像数据的各种图像处理。图像处理包括去马赛克、白平衡、组合等。数字信号处理器120经由总线180将所处理的图像数据提供至记录装置140以在记录装置140中记录该图像数据。此外,数字信号处理器120根据用户的操作使图像数据显示在显示装置150上。注意,数字信号处理器120是权利要求中所述的图像处理单元的示例。

[0049]

帧存储器130保存图像数据(帧)。记录装置140记录图像数据。显示装置150显示图像数据。电源电路160将电能提供至在电子设备100中安装的电路。

[0050]

操作电路170根据用户的操作产生操作信号,并且将信号提供至数字信号处理器120。总线180是在数字信号处理器120、帧存储器130、记录装置140、显示装置150、电源电路160以及操作电路170之间彼此交换信号的公共路径。

[0051]

[固态摄像元件的构造示例]

[0052]

图2是示出根据第一实施例的固态摄像元件200的构造示例的框图。固态摄像元件200包括电源单元210、垂直扫描电路230、像素阵列单元240、列信号处理单元270、水平扫描电路280以及时序控制单元285。

[0053]

像素阵列单元240具有布置为二维网格形状的多个像素电路。在下文中将在预定方向上布置的一组像素电路称为“行”,且在下文中将在与行垂直的方向上布置的一组像素电路称为“列”。此外,行的数量将由m表示(m为整数),并且列的数量将由n表示(n为整数)。

[0054]

电源单元210将电能提供至像素阵列单元240。垂直扫描电路230在时序控制单元285的控制下顺序地选择并驱动行。

[0055]

列信号处理单元270对来自像素阵列单元240的像素信号执行预定信号处理。作为信号处理,执行模拟数字(a/d)转换和cds处理。列信号处理单元270保存所处理的信号作为像素信号并且将信号输出至数字信号处理器120。注意,列信号处理单元270是权利要求中描述的信号处理单元的示例。

[0056]

水平扫描电路280控制列信号处理单元270并且在时序控制单元285的控制下顺序地输出行的像素数据。

[0057]

时序控制单元285在数字信号处理器120的控制下驱动垂直扫描电路230、列信号处理单元270和水平扫描电路280。

[0058]

注意,尽管帧存储器130设置在固态摄像元件200的外部,但帧存储器也可以设置在固态摄像元件200的内部。此外,安装在固态摄像元件200中的每个电路可以设置在同一芯片上,或者分布地设置在多个层叠的芯片上。在这种情况下,例如,电源单元210、垂直扫描电路230以及像素阵列单元240设置在层叠的芯片中的一个芯片上,并且列信号处理单元270、水平扫描单路280和时序控制单元285设置在另一芯片上。

[0059]

[像素阵列单元的构造示例]

[0060]

图3是示出根据第一实施例的像素阵列单元240的构造示例的框图。像素阵列单元240具有布置为二维网格形状的多个像素电路。这些像素电路被分类为有效像素电路250和虚设像素电路260。每个有效像素电路250是没有被遮光的电路,并且其像素信号被列信号处理单元270读取。另一方面,每个虚设像素电路260是被遮光的电路,并且其像素信号没有被列信号处理单元270读取。

[0061]

有效像素电路250设置在例如第1至第m

‑

1行,并且虚设像素电路260设置在第m行。注意,设置有虚设像素电路的位置不限制于第m行。虚设像素电路260可以设置在例如第一行或者第n列。

[0062]

此外,第m行(m是从1至m的整数)中的像素电路连接至包括三条信号线的水平信号线组239

‑

m。第n列(n是从1至n的整数)中的像素电路连接至包括5条信号线的垂直信号线组219

‑

n。

[0063]

[差分放大电路的构造示例]

[0064]

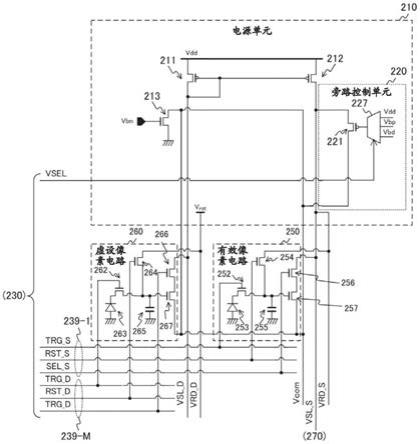

图4是示出根据第一实施例的差分放大电路的构造示例的电路图。针对每列,电源单元210包括p型晶体管211和212、恒定电流源213和旁路控制单元220。旁路控制单元220包括旁路晶体管221、电阻元件222和224以及开关223和225。

[0065]

此外,每个有效像素电路250包括传输晶体管252、光电二极管253、复位晶体管254、浮动扩散层255、选择晶体管256以及放大晶体管257。

[0066]

同时,每个虚设像素电路260包括传输晶体管262、光电二极管263、复位晶体管264、浮动扩散层265、选择晶体管266以及放大晶体管267。注意,图4中表示电容器的图形符号代表浮动扩散层255和265的寄生电容,并且电容没有作为电容组件设置。

[0067]

光电二极管253对光进行光电转换以产生电荷(例如,电子)。传输晶体管252根据传输信号trg_s将由光电二极管253产生的电荷传输至浮动扩散层255。

[0068]

浮动扩散层255累积电荷以产生对应于电荷量的电压。复位晶体管254根据复位信号rst_s将浮动扩散层255的电压设定为初始值。

[0069]

选择晶体管256根据选择信号sel_s打开或者闭合信号线vsl_s和放大晶体管257之间的路径。放大晶体管257提供与浮动扩散层255的电压对应的电流以作为信号电流。输出电压利用该信号电流来产生并且被从信号线vsl_s输出。注意,放大晶体管257是权利要求中描述的信号侧放大晶体管的示例。

[0070]

另外,复位晶体管254的漏极连接至信号线vrd_s,并且选择晶体管256的漏极连接

至信号线vsl_s。

[0071]

包括在虚设像素电路260中的组成元件的构造与有效像素电路的组成元件相似。但是,放大晶体管267的源极以及放大晶体管257的源极连接至信号线vcom。另外,复位晶体管264的漏极连接至施加有复位电压v

rst

的信号线vrd_d,并且选择晶体管266的漏极连接至信号线vsl_d。另外,利用传输信号trg_d、复位信号rst_d和选择信号sel_d来控制包括在虚设像素电路260中的传输晶体管、复位晶体管和选择晶体管。注意,放大晶体管267是权利要求中描述的参考侧放大晶体管的示例。

[0072]

另外,电源单元210的p型晶体管211的栅极连接至p型晶体管212的栅极。p型晶体管211的源极连接至p型晶体管211的栅极和信号线vsl_d,并且其漏极连接至电源电压vdd的电源。同时,p型晶体管212的源极连接至信号线vsl_s,并且其漏极连接至该电源。利用这种构造,p型晶体管211输出来自其源极的参考电流,并且p型晶体管212输出具有接近来自其源极的参考电流的值的信号电流。上述的电路也称为电流镜像电路。

[0073]

在每一列中设置有包括信号线vrd_s、vsl_s、vcom、vrd_d和vsl_d的垂直信号线组219

‑

n。

[0074]

恒定电流源213执行控制以使来自信号线vcom的电流保持恒定。恒流电流源213由例如n型晶体管实现,该n型晶体管的栅极被施加预定偏置电压vbn。

[0075]

通过上述的电流镜像电路、放大晶体管267和257以及恒流电流源213来构造用于放大一对差分输出电压的差分放大电路。一对差分输入电压中的一者被输入至放大晶体管257,并且一对差分输入电压中的另一者被输入至放大晶体管267。然后,通过放大差分输入电压获得的输出电压经由放大晶体管257的漏极侧的信号线vsl_s被输出至列信号处理单元270。

[0076]

这种差分放大电路通常比不执行差分放大的源极跟随电路具有更高的放大率。例如,假设源级跟随电路的像素的转换率为100μv/e

‑

,假设放大晶体管的输出噪声为100μvrms(均方根),且假设在a/d转换中发生的噪声为100μvrms。在这种配置中,总噪声为141μvrms,并且输入转换噪声为1.02e

‑

rms。同时,假设差分放大电路的像素的转换率为500μv/e

‑

,假设放大晶体管的输出噪声为500μvrms,并且假设在a/d转换中发生的噪声为500μvrms。在这种配置中,总噪声是510μvrms,并且输入转换噪声是1.02e

‑

rms。

[0077]

另外,旁路控制单元220的旁路晶体管221是例如p型mos晶体管,并且旁路晶体管221的栅极和漏极短接(即,二极管连接)。另外,旁路晶体管221的源极连接至信号线vsl_s。注意,旁路晶体管221可以是n型晶体管。

[0078]

每个电阻元件222和224的一端连接至旁路型晶体管221的漏极。此外,电阻元件222的另一端连接至开关223,且电阻元件224的另一端连接至开关225。此外,电阻元件222和224的电阻值彼此不同。注意,电阻元件222和224是权利要求中描述的第一和第二电阻元件的示例。

[0079]

开关223按照切换信号swp打开和闭合电阻元件222和信号线vcom之间的路径。开关225根据切换信号swd打开和闭合电阻元件224和信号线vcom之间的路径。

[0080]

垂直扫描电路230同时选择有效像素电路250的任一行和虚设像素电路260的行以利用复位信号、传输信号和选择信号驱动电路。所选择的行中的有效像素电路250和与有效像素电路处于同一列的虚设像素电路260成对地作为差分放大电路运行以产生像素信号。

下面将详细说明旁路控制单元220的功能。

[0081]

[列信号处理单元的构造示例]

[0082]

图5是示出根据第一实施例的列信号处理单元270的构造示例。列信号处理单元270包括斜坡信号生成电路271、n个电容272、n个电容器273、n个比较器274、n个计数器275以及数据保存单元276。在每一列中设置有每个电容272、电容器273、比较器274以及计数器275。

[0083]

斜坡信号生成电路271产生斜坡信号,该斜坡信号具有根据时序控制单元285的控制以恒定的速度增加的电平。

[0084]

电容器272保存斜坡信号。电容器273保存来自相应列的像素信号。这些电容器实现了自动调零功能(autozero function)。

[0085]

比较器274比较斜坡信号和相应列的像素信号。这些比较器274将比较结果提供至相应列的计数器275。

[0086]

计数器275对基于比较器274的比较结果的值进行计数。每个计数器275接收作为来自时序控制单元285的输入数据的时钟信号clk以及复位信号rstp和rstd。当复位信号rstp被输入时,计数器275将计数值设定为初始值。然后,计数器275以与时钟信号clk同步的方式使计数值递增,直至斜坡信号的电平超过像素信号的电平。于是,测量出p相电平。

[0087]

另外,当复位信号strd被输入时,计数器275反转计数值的符号。然后,计数器275以与时钟信号clk同步的方式使计数值递增,直至斜坡信号的电平超过像素信号的电平。于是,测量出p相电平和d相电平之间的差值。计数器275将差值数据作为像素数据输出至数据保存单元276。将获得p相电平和d相电平之间的差值的处理称为cds处理。电容器272和273执行模拟cds处理,并且计数器275执行数字cds处理。

[0088]

数据保存单元276保存n条像素数据。数据保存单元276根据水平扫描电路280的控制顺序地输出所保存的像素数据。

[0089]

图6是示出根据第一实施例的在限制之前在差分放大电路中流动的电流的实施例的示图。当要测量p相电平时,垂直扫描电路230执行控制使得利用切换信号swp使开关223处于闭合状态并且利用切换信号swd使开关225处于打开状态。

[0090]

此处,处于p型晶体管212的源极侧的节点的电压作为差分放大电路的输出电压vo被输出至列信号处理单元270。在下文中将该节点称为输出节点501。另外,恒流电流源213的处于放大晶体管侧的节点具有公共相位电压。在下文中将该节点称为公共相位节点502。放大晶体管267的栅极接收作为输入的一个差分输入电压v

in_r

,并且放大晶体管257的栅极接收作为输入的另一个差分输入电压v

in_s

。输入电压v

in_r

是虚设像素电路260的浮动扩散层的电压,并且输入电压v

in_s

是有效像素电路250的浮动扩散层的电压。

[0091]

垂直扫描电路230控制所选择行的选择晶体管256以及包括在虚设像素260中的选择晶体管266,使得晶体管处于接通状态。然后,垂直扫描电路230将复位晶体管264和254设定为接通状态以初始化输入电压v

in_r

和v

in_s

。

[0092]

电流镜像电路的p型晶体管211提供参考电流ir,并且p型晶体管212提供具有接近参考电流ir的值的信号电流is。这些电流由例如以下公式表示。

[0093]

ir=i+δi

…ꢀꢀ

公式1

[0094]

is=i

‑

δi

…ꢀꢀ

公式2

[0095]

参考电流ir和信号电流is在公共相位节点502汇合,并且它们的总和被恒流电流源213控制为恒定。由恒流电流源213引起的从公共相位节点502朝向接地节点流动的电流i

const

由以下公式表示。

[0096]

i

const

=is+ir

…ꢀꢀ

公式3

[0097]

基于公式1和2,公式3的i

const

是2i。在输入电压v

in_r

和v

in_s

被初始化后,参考电流ir和信号电流is立刻相等。例如,如果i

const

被设定为20微安(μa),参考电流ir和信号电流is都为10微安(μa)。

[0098]

然后,由于有效像素电路250没有被遮光,而虚设像素电路260被遮光,所以包含在有效像素电路250中的光电二极管253产生电荷。

[0099]

在读取p相电平时,垂直扫描电路230使包括在有效像素电路250中的传输晶体管252为断开状态。因此,光电二极管253的电荷没有被传输至浮动扩散层,并且输入电压v

in_s

仍然正常地具有初始值。

[0100]

然而,当非常大量的光入射时,例如当在阳光下摄像时,光电二极管253可产生大量的电荷,并且电荷泄露到超过传输晶体管252的电位的浮动扩散层。由此,存在着(具有p相电平的)输出电压vo的值增加的可能性。

[0101]

在输出电压vo低于由下述公式表示的限制电压v

clip_p

的情况下,旁路晶体管221的栅极

‑

源极电压低于阈值电压,并且因此旁路晶体管221处于断开状态。

[0102]

v

clip_p

=vc+rp

×

is’+|v

th

|

[0103]

上述公式的vc表示公共相位节点502的公共电压,并且其单位为例如伏特(v)。rp表示电阻元件222的电阻值,并且其电阻的单位是例如欧姆(ω)。is’表示对应于v

clip_p

的信号电流,并且其单位是例如安培(a)。v

th

表示旁路晶体管221的阈值电压,并且其单位是例如伏特(v)。

[0104]

在旁路晶体管221处于断开状态(p相电平低于限制电压v

clip_p

)的情况下,没有电流在旁路控制单元220中流动,并且信号电流is经由放大晶体管257从输出节点501流向公共相位节点502。

[0105]

图7是示出根据第一实施例的在限制之后在差分放大电路中流动的电流的示例的示图。当输出电压vo达到限制电压v

clip_p

时,旁路晶体管221的栅极

‑

源极电压超过阈值电压,并且旁路晶体管221过渡至接通状态。于是,输出节点501和公共相位节点502经由旁路晶体管221连接(旁路),并且信号电流is’在旁路控制单元220中流动。此时,p型晶体管211提供ir’(=2i

–

is’)。

[0106]

由于在恒流电压源213中流动的电流(=is’+ir’)是恒定的,所以在放大晶体管257中无电流流动。因此,输出电压vo的增加停止并且固定于限制电压v

clip_p

(换句话说,被限幅)。

[0107]

然后,当在p相电平之后读取d相电平时,垂直扫描电路230使开关223处于打开状态并且使开关225处于闭合状态。于是,d相电平固定于由下述公式表达的限制电压v

clip_d

。注意,期望的是,限制电压v

clip_p

和v

clip_d

等于或低于如下的上限电压,在该上限电压处,放大晶体管在饱和区域中运行。

[0108]

v

clip_d

=vc+rd

×

is’+|vth|

[0109]

上述公式中的rd表示电阻元件224的电阻值,且其单位是欧姆(ω)。由于上述的rp

和rd是不同的,所以d相电平被限幅在与p相电平的值不同的值处。

[0110]

此处,假设不具有旁路控制单元220的构造为比较示例。同样在该比较示例中,当强光入射时,光电二极管253产生大量的电荷,并且这些电荷可能泄露到超过传输晶体管252的电位的浮动扩散层。于是,输出电压(p相电平)增加。

[0111]

然而,由于在没有设置旁路控制单元220的比较示例中没有限制p相电平,所以p相电平可以增加成直到接近电源电压vdd的值。尽管在p相电平之后产生d相电平,但例如在高照度的环境中同样产生具有接近电源电压vdd的值的d相电平。如果p相电平和d相电平如上所述地相等,它们的差值在cds处理中接近“0”,尽管有强入射光,仍然输出黑电平的像素数据。换句话说,黑点现象产生。

[0112]

另一方面,在固态摄像元件200中,由于旁路控制单元220使输出节点和公共相位节点采用旁路以将p相电平限制为限制电压v

clip_p

以下,所以即使在强光入射时,p相电平和d相电平也不具有相同的数值。于是,这可以解决黑点现象。

[0113]

此外,如果限制电压v

clip_p

和v

clip_d

不被设定为允许放大晶体管在饱和区域中运行的上限电压以下,当强光入射时存在着输出电压vo的幅值显著增加的可能性。如果输出电压vo的幅值较大,放大晶体管257可以在饱和区域之外的区域(线性区域或者截止区域)的范围内运行。在这种情况下,需要允许放大晶体管257在接下来的读出开始之前返回到饱和区域的稳定时间(settling time)。当获得多个图像数据时,帧速率由于稳定时间而降低。

[0114]

然而,在固态摄像元件200中,由于相位电平被限制成饱和区域的上限电压以下,所以可以抑制输出电压vo的幅值,并且可以使放大晶体管257在饱和区域中运行。因此,稳定时间不是必要的并且帧速率可以相应地提高。

[0115]

注意,尽管固态摄像元件200限制d相电平和p相电平二者,但在利用溢流栅极等来限制p相电平的情况下可以采用不限制p相电平的构造。在不限制p相电平的情况下,p相侧的电阻元件224和开关225不是必要的。

[0116]

[像素电路的操作示例]

[0117]

图8是示出根据本发明的第一实施例的像素电路的驱动操作的示例的时序图。时序控制单元285在曝光之前复位每个计数器275的计数值cnt。此外,垂直扫描电路230将所选行的选择信号sel_s和选择信号sel_d设定为高电平,并且在从这些行的曝光的开始时间起的预定脉冲时段中将这些行的复位信号rst_s和rst_d设定为高电平。

[0118]

在复位时,浮动扩散层由于差分放大电路的电压跟随功能而被初始化,并且差分放大电路的信号线vsl_s的输出电压vo具有接近复位电压v

rst

(低电平)的值。尽管在信号线rst_s和rst_d处于低电平时由于开关馈通(switch feethrough)而降低了浮动扩散层265和255的电压,但由于差分放大电路的公共相位相消作用而抑制了信号线rst_s和rst_d的电压的变化。

[0119]

此外,在紧接着时刻tr之后的时刻tswp处,垂直扫描电路230执行控制使得通过将切换信号swp设定为高电平使p相侧的开关223处于闭合状态。于是,p相电平被限制为限制电压v

clip_p

以下。

[0120]

然后,在时刻tr之后的从时刻tps至时刻tpe的时段中,斜坡信号增加,并且计数器275计数p相电平的计数值cnt

p

。即,列信号处理单元270读取p相电平。在强光射入的情况下,电荷从光电二极管泄露到浮动扩散层,信号线vsl_s的输出电压vo(p相电平)可以连续

地增加(即使在复位之后)。由于在未设置旁路控制单元220的比较示例中没有限制p相电平,所以p相电平可以达到接近电源电压vdd的值。图8中的粗虚线代表比较示例中的输出电压vo的变化的示例。如果设置旁路控制单元220,如附图中的实线所示,p相电平被限制。

[0121]

此外,在从浮动扩散层的复位开始经过曝光时间之后的时刻tswd处,垂直扫描电路230在脉冲时段中将传输信号trg_s设定为高电平。于是,电荷被传送至浮动扩散层,并且开始输出d相电平。此外,垂直扫描电路230将切换信号swp设定为低电平并将转换信号swd设定为高电平,并且由此控制d相侧的开关225以使其处于闭合状态。于是,d相电平被限制成限制电压v

clip_d

以下。此外,时序控制单元285将计数器275的计数值的符号反转为

‑

cnt

p

。

[0122]

此处,限制电压v

clip_p

和限制电压v

clip_d

之间的电位差被设定成使得例如对应于该电位差的计数值cnt

d

‑

p

超过像素数据的完整代码(full code)。例如,在a/d转换的量化位数为12并且计数值“0”至“4095”被计数的情况下,将电位差设定为超过对应于“4095”的电平。在此设置中,固态摄像元件200可在强光入射时输出具有完整代码(白色)的像素数据。

[0123]

在从时刻tswd后的时刻tds到时刻tde的时段内,斜坡信号增加,并且计数器计数对应于p相电平和d相电平之间的差值的计数值cnt

d

‑

p

。该差值的数据被读取为像素数据。

[0124]

在未设置旁路控制单元220的比较示例中也未限制d相电平,并且因此d相电平也增加至接近电源电压vdd的值。由此,p相电平和d相电平之间的差值实际上变为“0”,输出的像素数据具有接近黑电平的电平。换句话说,出现了黑点现象。

[0125]

另一方面,由于旁路控制单元220限制了固态摄像元件200中的p相电平,所以可以抑制黑点现象。另外,由于p相电平和d相电平被限制为饱和运行区域的上限电压以下,所以可以抑制输出电压vo的辐值并且放大晶体管257可以被设定为在饱和区域中运行。于是,稳定时间是不需要的,并且可以相应地提高帧速率。

[0126]

图9是示出根据第一实施例的固态摄像元件200的操作的实施例的流程图。例如,当执行用于产生图像数据的操作(按下快门按钮等)时,操作开始。

[0127]

垂直扫描电路230选择还未被选择的行(步骤s901),复位该行的浮动扩散层的电压(步骤s902)。另外,差分放大电路输出被限制为限制电压v

clip_p

以下的p相电平(步骤s903),并且然后在经过曝光时间之后输出被限制为限制电压v

clip_d

以下的d相电平(步骤s904)。列信号处理单元270输出p相电平和d相电平之间的差值以作为像素信号(步骤s905)。

[0128]

垂直扫描电路230确定所选择的行是否为最终行(步骤s906)。在该行不是最终行(步骤s906中的“否”)的情况下,垂直扫描电路230重复地执行从步骤s901起的过程。另一方面,在该行是最终行(步骤s906中的“是”)的情况下,垂直信号扫描电路230终止摄像过程。注意,当产生多条图像数据时,重复执行步骤s901至s906的过程直至摄像终止。

[0129]

如上所述,根据本发明的第一实施例,当p相电平达到限制电压时,旁路控制单元220连接输出节点和公共相位节点以使信号电流在旁路控制单元中流动,即使在强光入射时,p相电平仍可以被限制成限制电压以下。于是,可以防止由具有接近值的p相电平和d相电平以及具有该差值“0”(黑电平)的像素数据引起的黑点现象。

[0130]

[第一变形例]

[0131]

在上述的第一实施例中,旁路控制单元220利用两个电阻元件(222和224)将输出电压vo限制为两个不同的限制电压。然而,可以在没有设置电阻元件的情况下将输出电压

限制为两个限制电压。第一实施例的第一变形例的旁路控制单元220和第一实施例中的旁路控制单元的不同在于通过不具有电阻元件的旁路控制单元220来实现利用两个限制电压的限制。

[0132]

图10是示出根据第一实施例的第一变形例的差分放大电路的构造示例的电路图。与第一实施例的旁路控制单元相比,第一变形例的旁路控制单元220的不同在于包括旁路晶体管226以取代电阻元件222和224。

[0133]

旁路晶体管226是例如p型mos晶体管,其栅极和漏极被短接,并且其源极连接至信号线vsl_s。此外,旁路晶体管226的阈值电压不同于旁路晶体管221的阈值电压。注意,旁路晶体管221和226是权利要求中描述的第一和第二晶体管的示例。另外,旁路晶体管226可以是n型晶体管。

[0134]

此外,开关223连接至旁路晶体管221的漏极,并且开关225连接至旁路晶体管226的漏极。

[0135]

另外,如果旁路晶体管221和226的阈值电压分别被设定为v

thp

和v

thd

,利用下述的公式表示限制电压v

clip_p

和v

clip_d

。

[0136]

v

clip_p

=vc+|v

thp

|

[0137]

v

clip_d

=vc+|v

thd

|

[0138]

如上所述,根据本发明的第一实施例的第一变形例,具有不同阈值电压的旁路晶体管221和226限制阈值电压,并且因此可以在没有设置电阻元件的情况下实现两个限制电压的限制。

[0139]

[第二变形例]

[0140]

在上述的第一实施例中,旁路控制单元220利用两个不同的电阻元件(222和224)将输出电压vo限制为两个不同的限制电压。然而,可以在没有设置电阻元件的情况下将输出电压限制为两个限制电压。与第一实施例的旁路控制单元相比,根据第一实施例的第二变形例的旁路控制单元220的不同在于可以通过没有设置电阻元件的旁路控制单元220来实现利用两个限制电压的限制。

[0141]

图11是示出根据第一实施例的第二变形例的构造示例的电路图。与第一实施例的旁路控制单元相比,根据第二变形例的旁路控制单元220的不同在于包括选择器227以替代开关223、开关225以及电阻元件222和224。

[0142]

选择器227根据选择信号vsel选择电源电压vdd、偏置电压vbp和另一偏置电压vbd中的一者,并且将该所选择的电压输出至旁路晶体管221的栅极。偏置电压vbp和偏置电压vbd具有不同的电压值。另外,将偏置电压vbp和偏置电压vbd的电压值设定为电源电压vdd和公共电压vc之间的电压。期望的是,将这些偏置电压设定为高于公共电压vc。通过将偏置电压设定为高于公共电压vc,放大晶体管257可以在饱和运行区域中运行。

[0143]

垂直扫描电路230利用选择信号vsel在p相电平的读出时段中将偏置电压vbp输出,并且在d相电平的读出时段中将偏置电压vbd输出。另外,垂直扫描电路230在这些时段之外的时段中将电源电压vdd输出。

[0144]

另外,限制电压v

clip_p

和v

clip_d

可以用以下公式表达。

[0145]

v

clip_p

=vc+vbp

‑

|v

th

|

[0146]

v

clip_d

=vc+vbd

‑

|v

th

|

[0147]

图12是示出根据第一实施例的第二变形例的像素电路的驱动操作的示例的时序图。图中的点划线表示由选择器227输出的电压的变化。

[0148]

垂直扫描电路230利用选择信号vsel在p相电平读出之前的时刻tswp处将选择器227输出的电压从电源电压vdd改变为偏置电压vbp。然后,垂直扫描电路230利用选择信号vsel在d相电平读出之前的时刻tswd处将选择器227输出的电压改变为偏置电压vbd。

[0149]

如上所述,根据本发明的第一实施例的第二变形例,旁路控制单元220通过施加两个不同的偏置电压将输出电压限制为两个不同的限制电压,并且由此可以在不设置电阻元件的情况下实现利用两个限制电压的限制。

[0150]

<2.第二实施例>

[0151]

尽管虚设像素电路260在上述实施例中仅布置在第m行中,但在该布置中,第m

‑

1行之外的行中的有效像素电路250和虚设像素电路260之间的距离较大。安装在有效像素电路250和虚设像素电路260彼此不邻近的差分放大器电路中的元件的特性的不均匀性比在有效像素电路250和虚设像素电路260彼此邻近的情况下的元件特性的不均匀性更显著,这可以是在图像数据中发现的噪声的源。为此,期望的是,在噪声减少方面,将虚设像素电路260布置在接近有效像素电路250的位置。第二实施例的固态摄像元件200与第一实施例的固态摄像元件200的不同在于虚设像素电路布置在有效像素电路附近。

[0152]

图13是示出根据第二实施例的固态摄像元件200的构造示例的框图。与第一实施例的固态传感器200相比,根据第二实施例的固态传感器200的不同在于还包括信号切换单元290。

[0153]

图14是示出根据第二实施例的像素阵列单元240的构造示例的框图。根据第二实施例的像素阵列单元240具有布置在奇数行中的奇数行像素电路251和布置在偶数行中的偶数行像素电路261。所有这些像素电路都不被屏蔽光。

[0154]

奇数行像素电路251是被列信号处理单元270读取信号的有效像素电路。另一方面,偶数行像素电路261是不被读取信号的虚设像素电路。

[0155]

注意,尽管以交替的方式每隔一行地布置有效像素和虚设像素,但构造并不限于此,只要有效像素和虚设像素彼此邻近。例如,有效像素可以布置在第4k和第4k+3(k是整数)行,并且虚设像素可以布置在第4k+1和第4k+2行。

[0156]

图15是示出根据第二实施例的差分放大电路的构造示例的电路图。与第一实施例的电源单元210相比,第二实施例的电源单元210的不同之处在于进一步包括差分输入限制单元300。

[0157]

差分输入限制单元300将偶数行像素电路261(虚设像素)侧的信号线vsl_e的输出电压限制为限制电压以下。虚设侧(即一对差分输出电压中的一者)的输出电压被限制为例如与用于一对差分输出电压中的另一者(vo)的p相电平的限制电压v

clip_d

相等的电压以下。差分输入限制单元300包括p型晶体管301、电阻元件302和开关303。

[0158]

p型晶体管301为二极管连接,并且插入在另一p型晶体管211的源极和电阻元件302之间。开关303根据切换信号swr打开或者闭合用于连接电阻元件302和恒流电源213的路径。

[0159]

另外,信号切换单元290包括开关291、292、293和294。开关291根据选择信号swr将选择晶体管266的漏极的连接目标切换为p型晶体管211和p型晶体管212中的一者。开关292

根据选择信号swr将选择晶体管256的漏极的连接目标切换为p型晶体管211和p型晶体管212中的一者。

[0160]

开关293根据选择信号swr将复位晶体管264的漏极的连接目标切换为复位电压v

rst

的电源和p型晶体管212中的一者。开关294根据选择信号swr将复位晶体管254的漏极的连接目标切换为复位电压v

rst

的电源和p型晶体管212中的一者。

[0161]

垂直信号电路230执行控制使得在驱动奇数行中的像素的情况下开关303根据选择信号swr进入闭合状态,选择晶体管266的连接目标指向p型晶体管211,并且选择晶体管256的连接目的地指向p型晶体管212。另外,垂直扫描电路230执行控制使得在驱动奇数行的像素时复位晶体管264的连接目的地指向复位电压vrst并且复位晶体管254的连接目的地指向p型晶体管212。该控制使差分放大电路的连接构造相似于第一实施例的差分放大电路的连接构造。

[0162]

另一方面,垂直扫描电路230执行控制使得在驱动偶数行的像素的情况下开关303根据选择信号swr进入打开状态,选择晶体管266的连接目的地指向p型晶体管212,并且选择晶体管256的连接目的地指向p型晶体管211。另外,垂直扫描电路230执行控制使得在驱动偶数行像素时复位晶体管264的连接目的地指向p型晶体管212并且复位晶体管254的连接目的地指向复位电压vrst。该控制使奇数行的选择晶体管和复位晶体管的连接目的地与偶数行的选择晶体管和复位晶体管的连接目的地交换。

[0163]

另外,根据传输信号trg_o、复位信号rst_o和选择信号sel_o控制奇数行像素电路251,并且根据传输信号trg_e、复位信号rst_e和选择信号sel_e控制偶数行像素单路261。

[0164]

图16是示出根据第二实施例的奇数行像素电路251的驱动操作的示例的时序图。当驱动奇数行像素时,垂直扫描电路230利用切换信号swr(其被设定为低电平)将开关303设定为闭合状态,以使差分放大电路的连接构造类似于第一实施例的差分放大电路的连接构造。由于将开关303设定为闭合状态,所以(偶数行中的)虚设像素的信号线vsl_e的电平被限制为用于(奇数行中的)有效像素的p相电平的限制电压以下。上述的对虚设侧的信号线vsl_e的电压的限制是因为虚设像素不被屏蔽光。不对虚设像素屏蔽光的原因在于,在上述的以交替的形式布置虚设像素和有效像素的构造中难以只对虚设像素屏蔽光。

[0165]

用于奇数行的传输信号trg_o、复位信号rst_o以及选择信号sel_o的传输时序类似于第一实施例的有效像素的传输时序。用于偶数行的传输信号trg_e、复位信号rst_e和选择信号sel_e的传输时序类似于第一实施例的虚设像素的传输时序。

[0166]

图17是示出根据第二实施例的偶数行像素电路261的驱动操作的示例的时序图。垂直扫描电路230利用被设定为高电平的切换信号swr使选择晶体管和复位晶体管的连接目的地相互切换。另外,垂直扫描电路230在从读出d相电平之前的传输时刻tswd起的脉冲时段内只将用于奇数行的传输信号trg_e设定为高电平。

[0167]

如上所述,由于根据本发明的第二实施例将有效像素和虚设像素以交替的方式布置为彼此互相邻近,所以可以降低元件特性的不均匀性并且由此相对于有效像素不邻近虚设像素的第一实施例可以减少噪声。

[0168]

另外,上述实施例是用于实施本发明的示例,并且实施例中的事项都与权利要求中的公开特定事项具有对应关系。同样地,由相同名称表示的实施例中的事项和权利要求中的公开特定事项具有对应关系。然而,本发明不限于这些实施例,并且在不脱离本发明的

范围的情况下,可以在本发明的范围内实现实施例的各种变形。

[0169]

同时,此处描述的效果没有必要受到限制,并且可能是本公开中所描述的效果。

[0170]

此外,本发明也可以进行如下构造。

[0171]

(1)一种固态摄像元件,其包括:

[0172]

信号侧放大晶体管,其用于通过将与一对差分输入电压中的一者相对应的信号电流从输出节点提供至公共相位节点来产生与所述信号电流相对应的输出电压;

[0173]

参考侧放大晶体管,其用于将与所述一对差分输入电压中的另一者相对应的参考电流提供至所述公共相位节点;

[0174]

恒定电流源,其用于恒定地控制在所述公共相位节点处汇合的所述信号电流和所述参考电流的总和;和

[0175]

旁路控制单元,其用于连接所述输出节点和所述公共相位节点,且在所述输出电压达到预定的限制电压的情况下将具有与所述限制电压相对应的值的所述信号电流提供至所述公共相位节点。

[0176]

(2)根据(1)的固态摄像元件,其还包括:

[0177]

信号处理单元,其用于通过读取来自有效像素电路和虚设像素电路之中的所述有效像素电路的信号来执行预定的信号处理,

[0178]

其中,所述信号侧放大晶体管布置在所述有效像素电路中,且所述参考侧放大晶体管布置在所述虚设像素电路中。

[0179]

(3)根据(2)的固态摄像元件,其中,所述虚设像素电路被遮光。

[0180]

(4)根据(2)的固态摄像元件,其中,所述虚设像素电路不被遮光,且布置为邻近所述有效像素电路。

[0181]

(5)根据(1)至(4)中任一项的固态摄像元件,其中,所述旁路控制单元包括旁路晶体管,所述旁路晶体管的源极连接到所述输出节点。

[0182]

(6)根据(5)的固态摄像元件,其中,

[0183]

所述信号侧放大晶体管输出作为所述输出电压的p相电平,并然后输出作为所述输出电压的不同于所述p相电平的d相电平,并且

[0184]

所述限制电压包括用于限制所述p相电平的p相限制电压和用于限制所述d相电平的d相限制电压。

[0185]

(7)根据(6)的固态摄像元件,其中,

[0186]

所述旁路控制单元还包括并联地与所述旁路晶体管连接的第一电阻元件和第二电阻元件,

[0187]

所述旁路晶体管的栅极和漏极短接,并且

[0188]

所述第一电阻元件的电阻值是对应于所述p相限制电压的值,且所述第二电阻元件的电阻值是对应于所述d相限制电压的值。

[0189]

(8)根据(6)的固态摄像元件,其中,

[0190]

所述旁路晶体管包括具有不同的阈值电压的第一旁路晶体管和第二旁路晶体管,

[0191]

所述第一旁路晶体管的栅极和漏极短接,且所述第二旁路晶体管的栅极和漏极短接,并且

[0192]

所述第一旁路晶体管的阈值电压是对应于所述p相限制电压的值,且所述第二旁

路晶体管的阈值电压是对应于所述d相限制电压的值。

[0193]

(9)根据(6)的固态摄像元件,其中,

[0194]

所述旁路控制单元还包括选择器,所述选择器用于选择电源电压、第一偏置电压和第二偏置电压中的一者,且将所选择的电压提供至所述旁路晶体管的栅极,所述第一偏置电压和所述第二偏置电压彼此不同,并且

[0195]

所述第一偏置电压是对应于所述p相限制电压的值,且所述第二偏置电压是对应于所述d相限制电压的值。

[0196]

(10)一种电子设备,其包括:

[0197]

信号侧放大晶体管,其用于通过将与一对差分输入电压中的一者相对应的信号电流从输出节点提供至公共相位节点来产生与所述信号电流相对应的输出电压;

[0198]

参考侧放大晶体管,其用于将与所述一对差分输入电压中的另一者相对应的参考电流提供至所述公共相位节点;

[0199]

恒定电流源,其用于恒定地控制在所述公共相位节点处汇合的所述信号电流和所述参考电流的总和;

[0200]

旁路控制单元,其用于连接所述输出节点和所述公共相位节点,并且在所述输出电压达到预定的限制电压的情况下将具有与所述限制电压相对应的值的所述信号电流提供至所述公共相位节点;和

[0201]

图像信号处理单元,其用于对根据所述输出电压的信号产生的图像数据执行预定的图像处理。

[0202]

(11)固态摄像元件的控制方法,所述控制方法包括:

[0203]

通过差分放大电路产生输出电压的输出电压产生步骤,所述差分放大电路包括信号侧放大晶体管、参考侧放大晶体管和恒定电流源,所述信号侧放大晶体管用于通过将与一对差分输入电压中的一者相对应的信号电流从输出节点提供至公共相位节点来产生与所述信号电流相对应的所述输出电压,所述参考侧放大晶体管用于将与所述一对差分输入电压中的另一者相对应的参考电流提供至所述公共相位节点,所述恒定电流源用于恒定地控制在所述公共相位节点处汇合的所述信号电流和所述参考电流的总和;和

[0204]

连接所述输出节点和所述公共相位节点并且在所述输出电压达到预定的限制电压的情况下将具有与所述限制电压相对应的值的所述信号电流提供至所述公共相位节点的旁路控制步骤。

[0205]

附图标记

[0206]

100

ꢀꢀ

电子设备

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

110

ꢀꢀ

摄像透镜

[0207]

120

ꢀꢀ

数字信号处理器

ꢀꢀꢀꢀꢀꢀꢀ

130

ꢀꢀ

帧存储器

[0208]

140

ꢀꢀ

记录装置

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

150

ꢀꢀ

显示装置

[0209]

160

ꢀꢀ

电源电路

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

170

ꢀꢀ

操作电路

[0210]

180

ꢀꢀ

总线

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

200

ꢀꢀ

固态摄像元件

[0211]

210

ꢀꢀ

电源单元

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

211、212、301

ꢀꢀ

p型晶体管

[0212]

213

ꢀꢀ

恒流电流源

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

220

ꢀꢀ

旁路控制单元

[0213]

221、226

ꢀꢀ

旁路晶体管

ꢀꢀꢀꢀꢀꢀꢀ

222、224、302

ꢀꢀ

电阻元件

[0214]

223、225、291、292、293、294、303

ꢀꢀ

开关

[0215]

227

ꢀꢀ

选择器

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

230

ꢀꢀ

垂直扫描电路

[0216]

240

ꢀꢀ

像素阵列单元

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

250

ꢀꢀ

有效像素电路

[0217]

251

ꢀꢀ

奇数行像素电路

ꢀꢀꢀꢀꢀꢀꢀ

252、262

ꢀꢀ

传输晶体管

[0218]

253、263

ꢀꢀ

光电二极管

ꢀꢀꢀꢀꢀꢀꢀ

254、264

ꢀꢀ

复位晶体管

[0219]

255、265

ꢀꢀ

浮动扩散层

ꢀꢀꢀꢀꢀꢀꢀ

256、266

ꢀꢀ

选择晶体管

[0220]

257、267

ꢀꢀ

放大晶体管

ꢀꢀꢀꢀꢀꢀꢀ

260

ꢀꢀ

虚设像素电路

[0221]

261

ꢀꢀ

偶数行像素电路

ꢀꢀꢀꢀꢀꢀꢀꢀ

270

ꢀꢀ

列信号处理单元

[0222]

271

ꢀꢀ

斜坡信号生成电路

ꢀꢀꢀꢀꢀꢀ

272、273

ꢀꢀ

电容器

[0223]

274

ꢀꢀ

比较器

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

275

ꢀꢀ

计数器

[0224]

276

ꢀꢀ

数据保存单元

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

280

ꢀꢀ

水平扫描电路

[0225]

285

ꢀꢀ

时序控制单元

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

290

ꢀꢀ

信号切换单元

[0226]

300

ꢀꢀ

差分输入限制单元

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1