符号和定时恢复设备及相关方法与流程

本说明大体来说涉及符号和定时恢复,且更特定来说涉及符号和定时恢复设备及相关方法。

背景技术:

1、一些无线和有线接收器(例如以太网物理层(phy))执行符号和定时恢复技术以促进装置之间的通信。一些以太网phy是过采样系统,其使用稳健的时钟同步技术来实现稳健的定时环路同步性能,所述性能是与改善的链接开启时间和位错误率(ber)性能相关联的参数。一些以太网phy利用每符号一个样本的系统架构来降低面积和功率方面的成本。一些此类以太网phy不具有稳健的定时环路同步性能。

技术实现思路

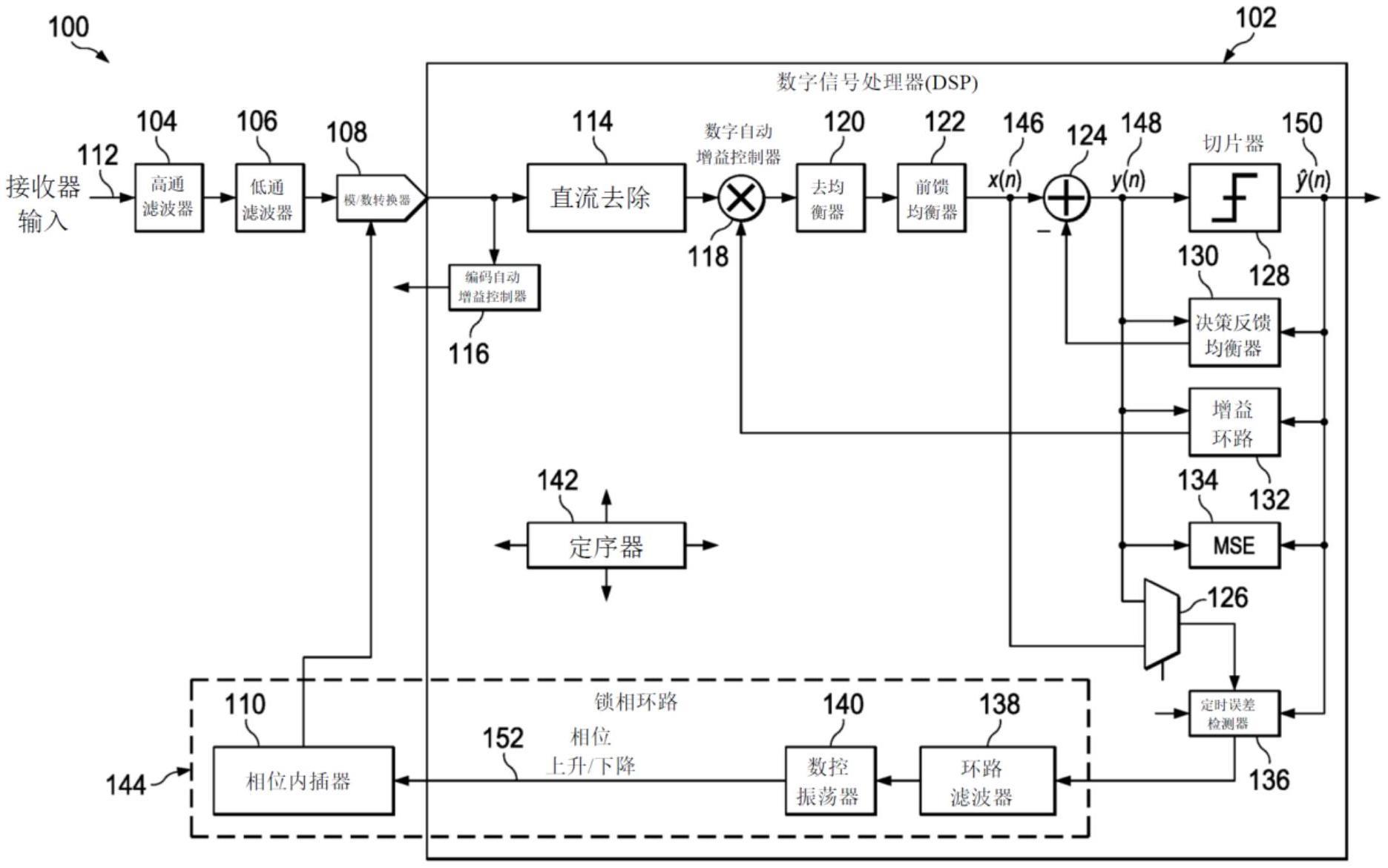

1、对于符号和定时恢复设备及相关方法,一种实例设备包含:前馈均衡器(ffe),其具有ffe输出;加法器电路,其具有第一加法器输入、第二加法器输入和第一加法器输出,所述第一加法器输入耦合到所述ffe输出;多路复用器(mux),其具有第一mux输入、第二mux输入和mux输出,所述第一mux输入耦合到所述第一加法器输出,所述第二mux输入耦合到所述ffe输出;决策反馈均衡器(dfe),其具有耦合到所述第二加法器输入的dfe输出;以及定时误差检测器(ted),其具有耦合到所述mux输出的第一ted输入。

技术特征:

1.一种设备,其包括:

2.根据权利要求1所述的设备,其中所述加法器电路具有第二加法器输出,所述dfe具有dfe输入,所述ted具有第二ted输入,并且所述设备进一步包含具有切片器输入、第一切片器输出和第二切片器输出的切片器电路,所述切片器输入耦合到所述第二加法器输出,所述第一切片器输出耦合到所述dfe输入,所述第二切片器输出耦合到所述第二ted输入。

3.根据权利要求1所述的设备,其中所述mux是第一mux,所述mux输出是第一mux输出,所述dfe具有第一dfe输出和第二dfe输出,并且所述ted包含:

4.根据权利要求3所述的设备,其中所述第一mux具有第一mux控制输入,所述第二mux具有第二mux控制输入,并且所述设备进一步包含定序器电路,所述定序器电路具有耦合到所述第一mux控制输入的第一定序器输出和耦合到所述第二mux控制输入的第二定序器输出。

5.根据权利要求3所述的设备,其中所述第二mux具有第三mux输出,并且所述设备进一步包含锁相环路(pll),所述pll具有耦合到所述第三mux输出的pll输入。

6.根据权利要求1所述的设备,其中所述ted具有ted输出,并且所述设备进一步包含:

7.根据权利要求6所述的设备,其中所述相位检测器具有相位检测器输出,并且所述设备进一步包含:

8.根据权利要求1所述的设备,其中所述ffe具有ffe输入,所述ted具有ted输出,并且所述设备进一步包含:

9.一种接收器,其可操作以接收包含多个符号的通信信号,所述接收器包括:

10.根据权利要求9所述的接收器,其中所述处理器用以基于所述电压满足所述阈值而识别定时环路锁定。

11.根据权利要求9所述的接收器,其中所述一或多个第一符号包含第三符号、第四符号和第五符号,并且所述处理器用以:

12.根据权利要求11所述的接收器,其中所述第三符号是切片器电路的当前决策,所述定时相位偏移是第二定时相位偏移,并且所述处理器用以响应于所述过零转变的所述检测,确定所述第二符号为所述当前决策的正负号和与所述第四符号对应的第一定时相位偏移的乘积。

13.根据权利要求9所述的接收器,其中所述一或多个第一符号包含第三符号、第四符号和第五符号,并且所述处理器用以:

14.根据权利要求13所述的接收器,其中所述第三符号是切片器电路的当前决策,所述定时相位偏移是第二定时相位偏移,并且所述处理器用以响应于所述过零转变的所述检测,确定所述第二符号为所述当前决策的正负号和与所述第四符号对应的第一定时相位偏移的乘积。

15.根据权利要求9所述的接收器,其中所述处理器用以:

16.根据权利要求9所述的接收器,其中所述定时相位偏移是在第二时间确定的第二定时相位偏移,并且所述处理器用以:

17.根据权利要求9所述的接收器,其中所述一或多个第一符号包含第三符号、第四符号和第五符号,并且所述处理器用以:

18.根据权利要求17所述的接收器,其中所述第三符号是切片器电路的当前决策,所述定时相位偏移是第二定时相位偏移,并且所述处理器用以响应于所述峰值符号点转变的所述检测:

19.根据权利要求9所述的接收器,其中所述一或多个第一符号包含第三符号、第四符号和第五符号,并且所述处理器用以:

20.根据权利要求19所述的接收器,其中所述第三符号是切片器电路的当前决策,所述定时相位偏移是第二定时相位偏移,并且所述处理器用以响应于所述峰值符号点转变的所述检测:

21.根据权利要求9所述的接收器,其中所述一或多个第一符号包含第三符号和第四符号,并且所述处理器用以:

22.至少一种非暂时性计算机可读存储媒体,其包括指令,所述指令在被执行时致使处理器至少:

23.根据权利要求22所述的至少一种非暂时性计算机可读存储媒体,其中所述一或多个第一符号包含第三符号和第四符号,所述定时相位偏移是第二定时相位偏移,并且所述指令在被执行时致使所述处理器:

24.根据权利要求22所述的至少一种非暂时性计算机可读存储媒体,其中所述一或多个第一符号包含第三符号、第四符号和第五符号,所述定时相位偏移是第二定时相位偏移,并且所述指令在被执行时致使所述处理器:

25.根据权利要求22所述的至少一种非暂时性计算机可读存储媒体,其中所述一或多个第一符号包含第三符号、第四符号和第五符号,所述定时相位偏移是第二定时相位偏移,并且所述指令在被执行时致使所述处理器:

技术总结

一种实例设备(102)包含:前馈均衡器(FFE)(122),其具有FFE输出;加法器电路(124),其具有第一加法器输入、第二加法器输入和第一加法器输出,所述第一加法器输入耦合到所述FFE输出;多路复用器(MUX)(126),其具有第一MUX输入、第二MUX输入和MUX输出,所述第一MUX输入耦合到所述第一加法器输出,所述第二MUX输入耦合到所述FFE输出;决策反馈均衡器(DFE)(130),其具有耦合到所述第二加法器输入的DFE输出;以及定时误差检测器(TED)(136),其具有耦合到所述MUX输出的第一TED输入。

技术研发人员:拉古·加内桑,S·拉达克里希南,G·阿加瓦尔

受保护的技术使用者:德州仪器公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!