改进的CMOS图像传感器的制作方法

本发明大体上涉及cmos图像传感器。

背景技术:

1、近几十年来,cmos图像传感器在空间分辨率和性能方面取得了非常显著的进步,这些进步主要由配备摄像头的智能手机市场推动。

2、如今,这些高分辨率传感器生成的图片质量极高,包含越来越多的数据。

3、如今,高质量的图像在图像压缩之前的大小约为2mb至10mb。

4、当用于计算机视觉时,此类图片需要增加处理量,这可能会产生问题。更具体地,很大一部分的计算资源用于处理图像中几乎没有意义或没有意义的部分。此外,高性能的计算资源潜在地需要昂贵硬件和高能耗。

5、如果可以关注图像中可能包含重要和有用信息的部分,则可以解决这些问题。

6、在许多应用中,场景中运动的存在构成了待处理的视觉事件。例如在视频监控系统、人员计数系统、手势控制系统等中就是这种情况。

7、为了解决这些问题,已开发了所谓的动态视觉传感器(dvs),其中传感器的每个像素包括亮度变化检测器。当检测到亮度变化时,就会生成对应的事件。该事件包括时间戳和图像矩阵中相关像素的x、y坐标。

8、这种已知的传感器进一步包括冲突管理器,其通常位于图像阵列的边缘,以便在生成多个事件时解决事件之间的冲突。

9、文件us10567679b2公开了这种动态视觉传感器的示例。

10、这种已知传感器的基本原理是其允许重新创建场景中移动对象的时空轨迹。

11、然而,这种已知传感器具有与常规图像计算环境不兼容的复杂架构。

技术实现思路

1、本发明基于以下发现:对于许多计算机视觉应用,两个连续图像帧之间的简单图像变化检测产生的事件可以是有效的。

2、因此,本发明提供了一种新的传感器架构,其允许检测连续图像之间的变化并以简单的数据格式对变化进行编码。

3、根据本发明,对于每一张所捕获的图像,都会生成与图像大小相同的位元矩阵,其中每一位指示对应像素是否发生变化,优选地亮度是否发生变化。可选地,位矩阵还编码变化的性质,即亮度增加或亮度降低。

4、更具体地,本发明提供一种cmos图像传感器,其包括像素矩阵和像素控制电路,每个像素具有包括光电检测器和存储单元的像素结构,该像素控制电路能够顺序写入代表曝光之后的光电检测值到所述像素的存储单元,该图像传感器进一步包括比较电路,该比较电路用于存储至少部分所述像素的顺序光电检测值、用于比较所述顺序光电检测值、用于根据所述像素的顺序光电检测值生成比较信号,并且用于生成从所述比较信号反映图像变化的比较矩阵。

5、本发明允许明显简化每个像素结构并且不需要提供冲突管理器。

6、此外,本发明能提供与现有图像处理环境兼容的输出。由于需要更少的电力,可以用于电池供电的视觉系统,例如用于物联网(iot)领域中。

7、图像传感器可以进一步包括以下单独的或以任何技术兼容的组合获得的可选特征:

8、-所述比较电路包括双存储单元,该双存储单元包括一组存储单元对,所述一组存储单元对在对应于与所述读取总线相关联的像素的两次连续曝光的不同时间选择性地连接到相应的读取总线,所述读取总线可选择性地能够连接到相关联的像素组的存储单元。

9、-所述比较电路包括双总线单元,该双总线单元用于选择性地将给定对的两个存储单元连接到能够生成所述比较信号的比较器的一对输入端。

10、-所述读取总线和存储单元对分别与像素矩阵的列或行相关联。

11、-图像传感器包括第一扫描单元,该第一扫描单元用于将所述双存储单元的所述像素存储单元对顺序连接到所述比较器。

12、-图像传感器包括用于将选定像素组的像素存储单元顺序连接到所述读取总线的第二扫描单元。

13、-所述顺序光电检测值之间的关系是具有死区的比较函数。

14、-所述具有死区的比较函数是通过具有偏置调整的cmos差分对来执行的。

15、-比较电路能够仅针对所述一部分像素生成比较信号,每个比较信号与相应像素组相关联。

16、-比较电路能够仅针对所述一部分像素生成比较信号,并且图像传感器进一步包括用于内插比较信号并且用于将内插的比较信号与相应像素相关联的内插电路。

17、-图像传感器进一步包括组合电路,该组合电路能够组合由像素矩阵生成的像素值并形成主像素图像和包含在所述比较矩阵中并且与相应像素或与相应像素组相关联的相应比较信号。

18、-图像传感器进一步包括用于从所述比较矩阵确定图像变化水平的检测电路,以及用于仅当所述图像变化水平高于阈值时存储至少一个主图像的存储电路。

技术特征:

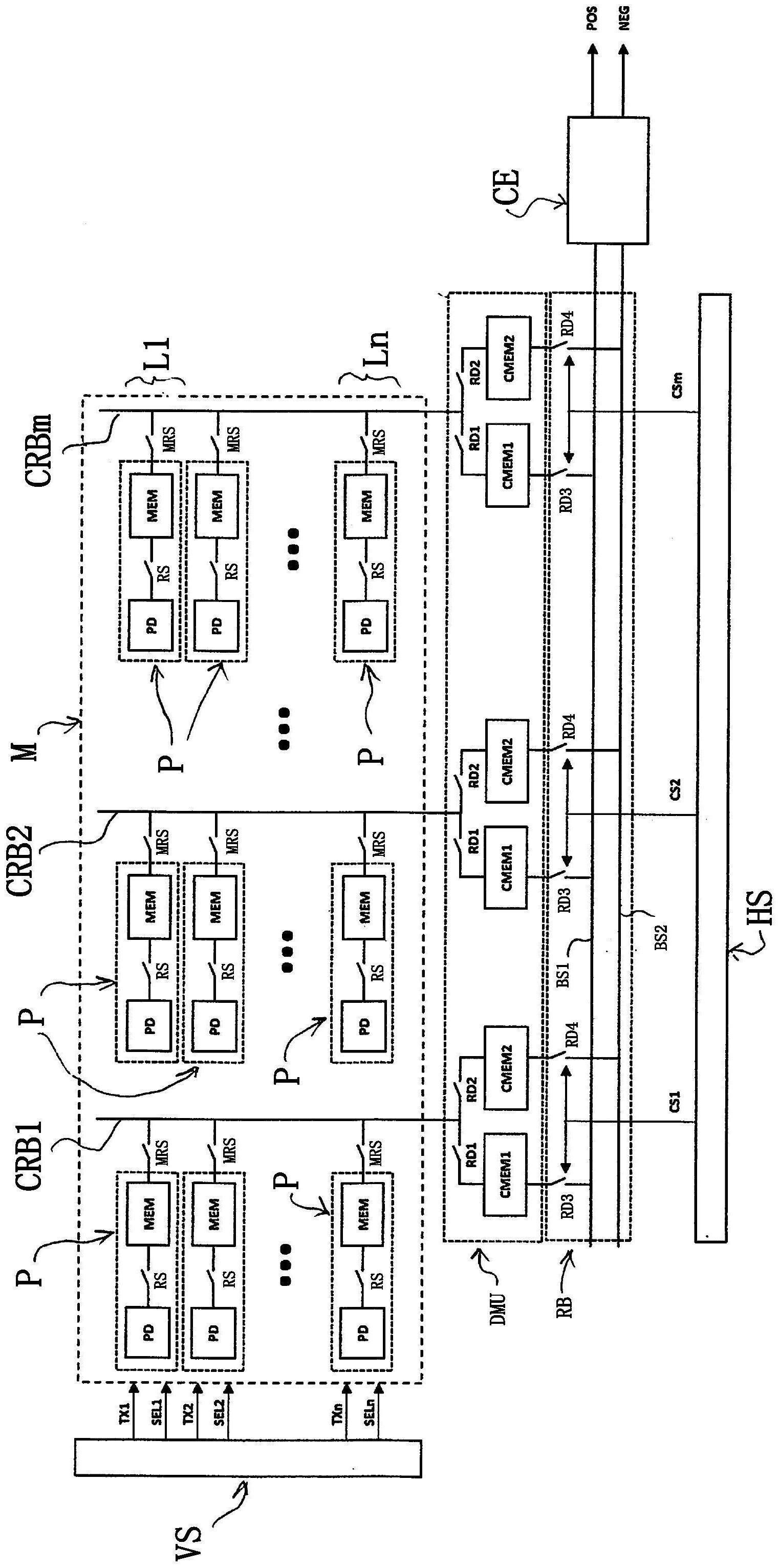

1.一种cmos图像传感器,其包括像素矩阵和像素控制电路(vs),每个像素具有包括光电检测器(pd)和存储单元(mem)的像素结构,所述像素控制电路能够顺序写入代表曝光之后的光电检测值到所述像素的存储单元(mem),所述图像传感器进一步包括比较电路(dmu、rb、ce),所述比较电路用于存储至少部分所述像素的顺序光电检测值、用于比较所述顺序光电检测值、用于根据所述像素的顺序光电检测值生成比较信号(nul、pos、neg),并且用于生成从所述比较信号反映图像变化的比较矩阵。

2.根据权利要求1所述的图像传感器,其中,所述比较电路包括双存储单元(dmu)和存储单元对相对应的读取总线(crbj),所述双存储单元(dmu)包括一组存储单元对(cmem1、cmem2),所述读取总线可选择性地将相关的像素组(li)的两次顺序曝光的光电检测值写入每个存储单元对中。

3.根据权利要求2所述的图像传感器,其中,所述比较电路包括双总线单元(rb),所述双总线单元用于选择性地将给定对的两个存储单元(cmem1、cmem2)连接到能够生成所述比较信号的比较器(ce)的一对输入端。

4.根据权利要求2或3所述的图像传感器,其中,所述读取总线(crbj)和存储单元对(cmem1、cmem2)分别与所述像素矩阵(m)的列或行相关联。

5.根据权利要求4所述的图像传感器,包括第一扫描单元(hs),所述第一扫描单元用于将所述双存储单元的所述像素存储单元对顺序连接到所述比较器。

6.根据权利要求5所述的图像传感器,包括第二扫描单元(vs),所述第二扫描单元用于将给定像素组(li)的像素存储单元(mem)顺序连接到所述读取总线(crbj)。

7.根据权利要求1至6中的任一项所述的图像传感器,其中,所述顺序光电检测值之间的关系是具有死区的比较函数。

8.根据权利要求7所述的图像传感器,其中,所述具有死区的比较函数是通过具有偏置调整的cmos差分对来执行的。

9.根据权利要求1至8中的任一项所述的图像传感器,其中,所述比较电路能够针对所述像素矩阵中仅一部分像素生成比较信号(nul、pos、neg),每个比较信号与相应的像素组相关联。

10.根据权利要求1至8中的任一项所述的图像传感器,其中,所述比较电路能够对所述像素矩阵中仅一部分像素生成比较信号(nul、pos、neg),并且进一步包括对比较信号进行内插并且用于将所内插的比较信号关联到各个像素的内插电路。

11.根据权利要求1至10中的任一项所述的图像传感器,进一步包括组合电路,所述组合电路能够组合由所述矩阵的所述像素生成的像素值并形成主像素图像和相应像素或像素组的比较矩阵中相应像素的比较信号。

12.根据权利要求11所述的图像传感器,进一步包括用于从所述比较矩阵确定图像变化水平的检测电路,以及仅当所述图像变化水平高于阈值时用于存储至少一个主图像的存储电路。

技术总结

本申请题为“改进的CMOS图像传感器”。一种CMOS图像传感器包括像素矩阵和像素控制电路(VS),每个像素具有包括光电检测器(PD)和存储单元(MEM)的像素结构,该像素控制电路能够顺序写入代表曝光之后的光电检测值到所述像素的存储单元(MEM)。根据本发明,图像传感器进一步包括比较电路(DMU、RB、CE),该比较电路用于:存储至少部分所述像素的顺序光电检测值;比较所述顺序光电检测值;根据所述像素的顺序光电检测值生成比较信号(NUL、POS、NEG);生成从所述比较信号反映图像变化的比较矩阵。

技术研发人员:倪扬

受保护的技术使用者:上海虹感微电子科技有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!