一种面向流控机制的无死锁可扩展互连裸芯架构的制作方法

1.本发明涉及数字集成电路技术领域,尤其是指一种面向片间virtual-cut-through流控机制的无死锁可扩展互连裸芯架构。

背景技术:

2.随着数字集成电路的发展,片上系统(system on chip,soc,指将多个功能模块集成到同一个硅片上)几乎已经成为了实现高性能系统的必要方案,生产厂商通过不断扩大soc的规模来满足用户对产品性能的需求。然而,受到加工工艺等因素的限制,摩尔定律(即集成电路上可容纳的晶体管数目每经约24个月增加一倍的规律)正在逐渐失效,这使得在单个硅片上扩大集成电路规模的成本和开发周期变得极高。

3.未来集成电路将朝多裸芯(die)集成方向发展,即将多个功能各异且已通过验证、未被封装的芯片组件互联组装起来,并封装为同一管壳中的芯片整体,形成多芯片模组(multi-chip module,mcm),这些组成mcm的裸芯被称为芯粒(chiplet),在同一个封装内的每个芯粒可以采用不同工艺、来自不同厂商,因此极大缩短和降低了开发周期和难度。目前主流的芯粒设计依赖的封装技术主要分为2d,2.5d和3d三类。其中,2d封装是指将多个芯粒以二维平面的排列方式、通过基板(substrate)上的物理总线互连集成到一起;2.5d封装中的芯粒可以通过中介层(interposer)中的物理链路互连;而3d封装除了具备2.5d封装的特点之外,其中介层内可以实现基于晶体管的数字电路,该中介层称为有源中介层。这些封装新技术为实现更复杂的多芯粒集成系统提供了物理基础。

4.然而,随着芯片中处理器(processor)和其他功能单元数量的爆炸式增长,为了充分发挥每个功能单元的作用,构建一个片上片间一体化的高性能网络,实现多个功能单元和多个芯粒之间的高效通信也尤为重要。在过去的20年里,片上网络(network-on-chip)技术取得了充分的研究和长足发展,尤其是在构建大型同构系统时,片上网络替代传统总线成为了不可或缺的系统部件。可以预见,片上网络理论在未来能够继续发挥其作用,并在一定程度上指导上述片上片间一体化网络的设计和构建。

5.流控(flowcontrol)机制是片上网络理论的重要概念,它代表着网络对数据流的资源分配方式与传输调度方式。virtual-cut-through是一种基于数据包的流控机制,在实现不确定路径(如传输延迟(latency)不确定的传输路径和跨时钟域传输路径等)的点对点传输,解决数据路由死锁问题上有着卓越的效果。在构建片上片间一体化网络,实现片间跨时钟域数据传输时,virtual-cut-through流控机制是一个不错的方案选择。

技术实现要素:

6.构建片上片间一体化网络的核心问题是通过优化片内设计,适应片间的互连结构和通信方式。一方面,为了适应片间互连结构,需要对传统的片上网络作出修改,通过调整结构布局以及增加功能组件使其具备片间互连通信的功能。另一方面,保证多片互连系统的数据传输路由无死锁是保证系统正常工作的首要条件之一,为了实现这一点,需要优化

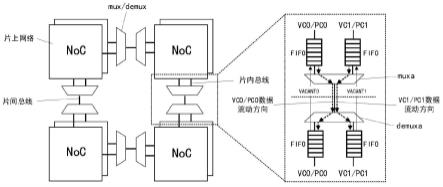

片内片间的路由方式和流控机制并实现片内片间全局无死锁。另外,由于不同的裸芯一般处于不同的时钟域,实现跨时钟高效片间无死锁控制也是一个重要的技术难题。

7.在3d封装中,由于物理结构的多层化,所述片上片间一体化的网络拥有更大的设计空间,通过提高网络的复杂程度,便可获得较高的性能。然而,在我国当今集成电路产业的发展条件下,受到技术成本的限制,实际生产中以2.5d甚至2d封装更为多见,在这种物理资源受限的情况下,设计出一个可靠且高效的片上片间一体化网络具有更高的技术难度和更大的现实意义。

8.为解决上述技术问题,本发明提供了一种面向流控机制的无死锁可扩展互连裸芯架构,旨在解决所述片上片间一体化网络在面临数据路由死锁、资源限制和跨时钟域片间传输等技术难题时缺少统一架构标准的问题。该架构包括内部的片上网络以及西、东两个扩展端口控制器,每个扩展端口控制器中包括一个旁路控制器、一个共享带宽的分配仲裁单元和一个同步控制器,可扩展裸芯级网络可以直接用于裸芯间互连,片上网络是系统的内部网络,可以采用任意拓扑的片上网络实现,且网络具有两个物理通道或虚通道;扩展端口控制器是系统内部片上网络与其他互连裸芯互连通信的接口,扩展端口控制器内部的旁路控制器用于管理一条跨过片上网络的双向的直连通路,所述旁路控制器与直连通路之间通讯互连;扩展端口控制器内部的共享带宽的分配仲裁单元管理着片间两个通道内的数据流动,即是所述virtual-cut-through流控机制的控制器;扩展端口控制器内部的同步控制器起到在片内时钟域和片间时钟域间同步数据传输。

9.本发明面向片间环形网络拓扑结构,即所述片上片间一体化网络总体上由多个片上网络相互连接成一个环形,在每个裸芯内部,采用双虚通道(virtual channel,vc)或双物理通道(physical channel,pc)的片上网络实现片内无死锁。多个裸芯之间的数据传输依靠片间的环形总线进行,当数据从一个裸芯传输至相邻裸芯时,首先在当前裸芯中经过一个双路复用单元(mux),该单元的作用是将两个虚拟或物理通道(下称通道)中的数据仲裁到一个片间物理链路上,然后该数据通过片间物理链路传输至相邻裸芯内,通过该裸芯内的分配单元(demux)被送入某一个通道。相邻裸芯间的物理链路是双向的,同一个裸芯的同一侧端口中既包含mux单元,又包含demux单元,所以图1中使用一个mux/demux单元来表示当前裸芯内的mux单元和demux单元组成的整体。

10.通过采用片间virtual-cut-through流控机制,可以消除片间互连潜在的数据路由死锁风险,实现全局无死锁。对于该流控机制,一般采用的对应的硬件电路结构如图1所示。在数据流的上游裸芯的发送端,设有两个fifo(first-in-first-out,先入先出队列)用于分别存储上游裸芯两个通道(vc0/pc0和vc1/pc1)内待发送的数据,在数据流的下游裸芯的接收端,设有两个fifo用于分别存储下由裸芯两个通道内待接收的数据。由于两个裸芯处于不同的时钟域,在图中muxa和demuxa之间,往往需要设置时钟域转换电路,如基于寄存器的同步电路或异步fifo,这些电路会在数据传输过程中引入流水级节拍,即传输延迟,这使得系统可能因所述流水级阻塞出现环形依赖,导致环形路由死锁。该问题可以通过采用virtual-cut-through流控机制解决,其大致方法为:上游发送端通过下游裸芯返回的信号指示位vacant判断下游的相应通道是否存在足够空位,以决定是否发送当前通道内的数据至下游。

附图说明

11.为了使本发明的内容更容易被清楚的理解,下面根据本发明的具体实施例并结合附图,对本发明作进一步详细的说明。

12.图1是本发明面向的网络总体拓扑结构以及virtual-cut-through硬件电路结构示意图;

13.图2是本发明所述可扩展高速互连裸芯通用架构框图;

14.图3是本发明所述互连裸芯中扩展端口控制器的具体结构图;

15.图4是本发明所述互连裸芯中的扩展端口控制器中的virtual-cut-through控制状态机的具体结构图。

具体实施方式

16.本发明面向片间环形网络拓扑结构,即所述片上片间一体化网络总体上由多个片上网络相互连接成一个环形,在每个裸芯内部,采用双虚通道(virtual channel,vc)或双物理通道(physical channel,pc)的片上网络实现片内无死锁。多个裸芯之间的数据传输依靠片间的环形总线进行,当数据从一个裸芯传输至相邻裸芯时,首先在当前裸芯中经过一个双路复用单元(mux),该单元的作用是将两个虚拟或物理通道(下称通道)中的数据仲裁到一个片间物理链路上,然后该数据通过片间物理链路传输至相邻裸芯内,通过该裸芯内的分配单元(demux)被送入某一个通道。相邻裸芯间的物理链路是双向的,同一个裸芯的同一侧端口中既包含mux单元,又包含demux单元,所以图1中使用一个mux/demux单元来表示当前裸芯内的mux单元和demux单元组成的整体。

17.通过采用片间virtual-cut-through流控机制,可以消除片间互连潜在的数据路由死锁风险,实现全局无死锁。对于该流控机制,一般采用的对应的硬件电路结构如图1所示。在数据流的上游裸芯的发送端,设有两个fifo(first-in-first-out,先入先出队列)用于分别存储上游裸芯两个通道(vc0/pc0和vc1/pc1)内待发送的数据,在数据流的下游裸芯的接收端,设有两个fifo用于分别存储下由裸芯两个通道内待接收的数据。由于两个裸芯处于不同的时钟域,在图中muxa和demuxa之间,往往需要设置时钟域转换电路,如基于寄存器的同步电路或异步fifo,这些电路会在数据传输过程中引入流水级节拍,即传输延迟,这使得系统可能因所述流水级阻塞出现环形依赖,导致环形路由死锁。该问题可以通过采用virtual-cut-through流控机制解决,其大致方法为:上游发送端通过下游裸芯返回的信号指示位vacant判断下游的相应通道是否存在足够空位,以决定是否发送当前通道内的数据至下游。

18.所提出的架构如图2所示,本实施例提供一种面向片间virtual-cut-through流控机制的无死锁可扩展互连裸芯架构,系统整体上包括内部的片上网络(或裸芯级网络,dualnod)以及西、东两个扩展端口控制器(west_port_controller和east_port_contorller),每个扩展端口控制器中包括一个旁路控制器(bypass_controller)、一个共享带宽的分配仲裁单元(allocarbiter_share)和一个同步控制器(sync_controller),系统总体上组成了可扩展裸芯级网络(extendualnod),可扩展裸芯级网络可以直接用于裸芯间互连,片上网络(或裸芯级网络)是系统的内部网络,可以采用任意拓扑的片上网络实现,但须保证网络具有两个物理通道或虚通道;

19.扩展端口控制器是系统内部片上网络与其他互连裸芯互连通信的接口,扩展端口控制器内部的旁路控制器用于管理一条跨过片上网络的双向的直连通路(旁路),每侧扩展端口控制器中的旁路控制器管理着一条通往另一侧扩展端口控制器中的旁路控制器的直连通路,所述旁路控制器与直连通路可以采用任意形式实现,扩展端口控制器内部的共享带宽的分配仲裁单元管理着片间两个通道内的数据流动,是所述virtual-cut-through流控机制的控制器,扩展端口控制器内部的同步控制器用于片内和片间的时钟域转换,起到在不同时钟域间同步数据传输。

20.而进一步地,分别以片内至片外和片外至片内两个方向的数据流为例展示本发明提出的扩展端口控制器的具体结构与功能:对于片内至片外的数据流,数据可能来自于旁路输入总线的两个通道(cdbpi_0和cdbpi_1),也可能来自于互连裸芯内部的片上网络的两个通道,即从cdi_0和cdi_1输入。来自于所述两路的数据首先进入旁路控制器,仲裁到一路的两个通道,然后进入共享带宽的分配仲裁单元,两个通道的数据分别被送至对应的两个fifo(fifo_o_0和fifo_o_1)中缓冲,两个fifo的输出经过一个数据选择器(mux)被仲裁到一条通道上,该通道进入同步控制器实现时钟域转换后作为输出总线表现在扩展端口控制器的片外输出端口上,即互连裸芯的片外输出端口上。

21.如图3所示,对于片外至片内的数据流,数据首先从互连裸芯的片外输入端口,即扩展端口控制器的片外输入端口进入同步控制器,经时钟域转换后进入共享带宽的分配仲裁单元,通过一个数据分配器(demux)被分配到其归属的某一个通道上,进入相应的fifo(fifo_i_0或fifo_i_1)缓冲,然后经fifo输出进入旁路控制器,并在旁路控制器的管理机制下或经输出总线cdo_0或cdo_1进入互连裸芯内部的片上网络,或经输出总线cdbpo_0或cdbpo_1进入旁路通路。

22.而进一步地,如图4所示,所述virtual-cut-through流控过程是在共享带宽的分配仲裁单元内部的状态机(finite state machine,fsm)的控制下完成的,该状态机的具体工作过程为:所述状态机根据其执行发送者角色或接收者角色被分为发送端状态机和接收端状态机两类,由于每个共享带宽的分配仲裁单元都负责管理输入和输出两个数据通路,所以其内部既设有一个发送端状态机,也设有一个接收端状态机。发送端状态机仅包括一个状态机实体,该状态机作为数据上游的控制节点,接收下游返回的vacant_i_0和vacant_i_1两个状态信号,分别用于指示下游的两个通道是否剩余足够空位。该状态机维护三个状态,分别为idle,send和conf,系统复位并释放后,该状态机进入idle状态。当数据上游的某一通道接收到上游传输请求,并同时检测下游返回的相应通道的vacant信号有效时,参与仲裁竞争。当某一个通道竞争成功后,状态机转换至send状态,同时该通道开始向下游传输数据。当该通道的数据包发送完毕后,状态机转换至conf状态。然后,当检测到下游返回的当前通道的vacant信号变为无效后,状态机返回到idle状态。接收端状态机包括两个状态机实体fsm_0和fsm_1,分别用于管理两个接收通道,两个状态机实体设有相同的状态init,vacant和occupy和状态转换逻辑,只是维护的通道不同。系统复位后,接收端状态机进入init状态,复位释放后,该状态机转换至vacant状态。当检测到当前通道有数据进入接收端fifo时,状态机切换至occupy状态。当检测到接收到的整个数据包离开当前通道的fifo时,状态机切换至vacant状态,如此反复。接收端作为数据下游,根据两个接收端状态机实体的是否处于vacant状态,分别将对应通道返回至数据上游的的vacant信号(vacant_o_0或

vacant_o_1)置为有效或无效。

23.本发明提出的互连裸芯的时钟域划分方式为:互连裸芯中划分有三个时钟域,分别为一个cdclk时钟域和两个cpclk时钟域。所述片上网络全部处于cdclk时钟域,扩展端口控制器横跨cdclk时钟域和cpclk时钟域,其具体划分方式为:旁路控制器和共享带宽的分配仲裁单元处于cdclk时钟域,同步控制器由于涉及时钟域转换,其一侧处于cdclk时钟域,另一侧处于cpclk时钟域,处于cpclk时钟域的一侧用于与片外互连。cpclk时钟域被划分为cpclk本地时钟域和cpclk接收时钟域。本地cpclk时钟由互连裸芯本地产生,并通过片外输出端口传送到其他裸芯;接收cpclk时钟通过片外输入端口从其他裸芯接收,是其他裸芯的本地cpclk时钟。

24.显然,上述实施例仅仅是为清楚地说明所作的举例,并非对实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引申出的显而易见的变化或变动仍处于本发明创造的保护范围之中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1