物理不可克隆函数的产生电路的制作方法

本发明涉及电路,更为具体地,涉及一种物理不可克隆函数的产生电路。

背景技术:

1、目前,物理不可克隆函数(physical unclonable function,puf)作为一种较为新型的电子技术,其主要用于产生于电路绑定的唯一识别码,并以此建立电路系统的安全信任根。

2、现有的puf是一种利用电路在生产制造过程中不可控的微小工艺误差产生唯一性的函数模块。例如金属导线的粗细,离子参杂浓度的不同等,由于误差很小,在工艺允许范围内,这些误差对器件本身的功能不造成影响,但确构成了不可预测,且无法复制的唯一性。使得相同的puf设计在不同的设备中,不同的芯片上,甚至不同的芯片上都完全不同,类似人类的指纹,因此可以用来作为芯片的唯一标识。

3、但是,现有的puf通常是易失性的,即在芯片上电后,用于产生puf的电路结构产生电信号,其在芯片下电后则会消失;此外,puf在每次生成的过程中往往会伴随一定的热噪声,电磁噪声等,也会导致最终获取的puf值存在一定的错误率。

技术实现思路

1、鉴于上述问题,本发明的目的是提供一种物理不可克隆函数的产生电路,以解决现有的电路存在的容易丢失,且错误率高等问题。

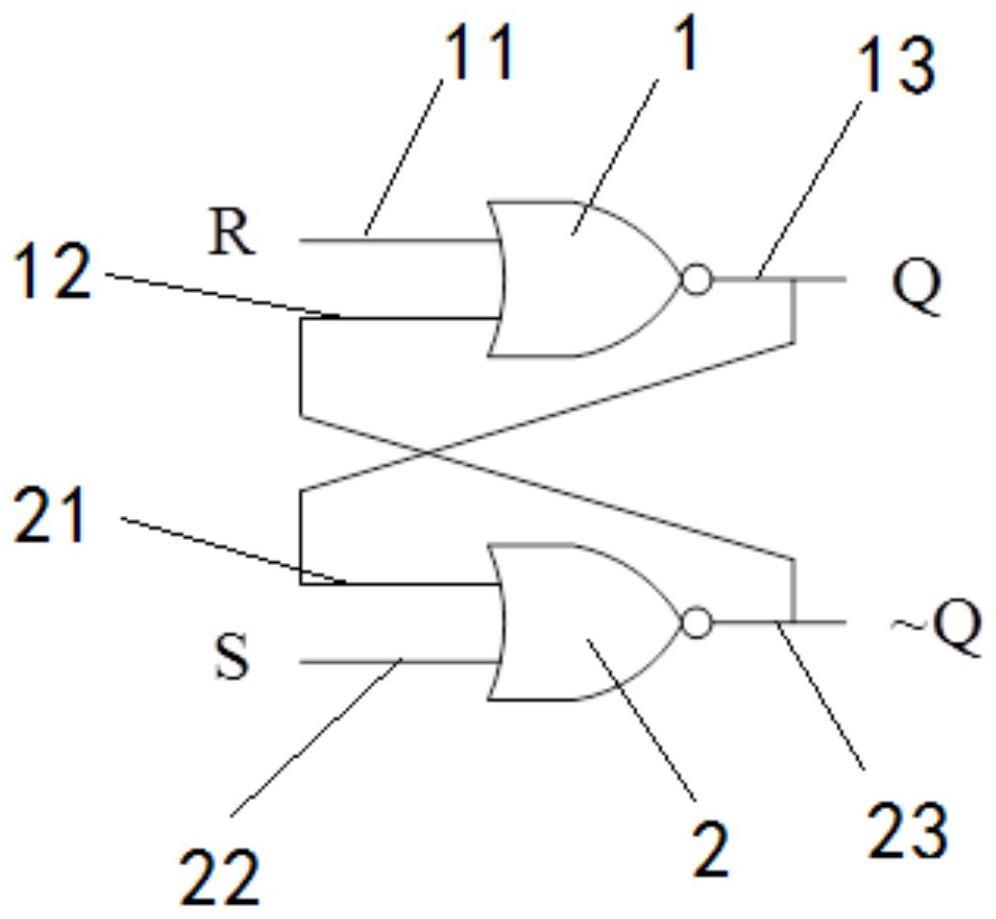

2、本发明提供的物理不可克隆函数的产生电路,包括两个或非门或两个与非门;其中,任意一个或非门/与非门的输出端与另外一个或非门/与非门的其中一个输入端连接;并且,两个或非门/与非门的另外一个输入端分别设置为异步置0端和异步置1端。

3、此外,可选的技术方案是,当包括两个或非门时,两个或非门包括第一或非门和第二或非门;其中,第一或非门的输出端与第二或非门的第一输入端连接;第二或非门的输出端与第一或非门的第二输入端连接;第一或非门的第一输入端与第二或非门的第二输入端连接。

4、此外,可选的技术方案是,还包括第一reram单元和第二reram单元;其中,第一reram单元和第二reram单元在物理不可克隆函数的产生电路中呈对称分布。

5、此外,可选的技术方案是,第一reram单元和第二reram单元分别包括低阻态和高阻态两种阻态。

6、此外,可选的技术方案是,当第一reram单元和第二reram单元的阻态相同。

7、此外,可选的技术方案是,基于第一或非门的输出端和第二或非门的输出端获取物理不可克隆函数。

8、此外,可选的技术方案是,当包括两个或非门时,两个与非门包括第一与非门和第二与非门;其中,第一与非门的输出端与第二与非门的第一输入端连接;第二与非门的输出端与第一与非门的第二输入端连接;第一与非门的第一输入端与第二与非门的第二输入端连接。

9、此外,可选的技术方案是,两个或非门或两个与非门形成rs锁存器。

10、利用上述物理不可克隆函数的产生电路,通过设置两个或非门或两个与非门,并使得任意一个或非门/与非门的输出端与另外一个或非门/与非门的其中一个输入端连接,此外两个或非门/与非门的另外一个输入端分别设置为异步置0端和异步置1端,该电路结构的不对称性更高,输出的物理不可克隆函数稳定性更高。

11、为了实现上述以及相关目的,本发明的一个或多个方面包括后面将详细说明的特征。下面的说明以及附图详细说明了本发明的某些示例性方面。然而,这些方面指示的仅仅是可使用本发明的原理的各种方式中的一些方式。此外,本发明旨在包括所有这些方面以及它们的等同物。

技术特征:

1.一种物理不可克隆函数的产生电路,其特征在于,包括:两个或非门或两个与非门;其中,

2.如权利要求1所述的物理不可克隆函数的产生电路,其特征在于,当包括两个或非门时,所述两个或非门包括第一或非门和第二或非门;其中,

3.如权利要求2所述的物理不可克隆函数的产生电路,其特征在于,还包括第一reram单元和第二reram单元;其中,

4.如权利要求3所述的物理不可克隆函数的产生电路,其特征在于,

5.如权利要求3所述的物理不可克隆函数的产生电路,其特征在于,

6.如权利要求2所述的物理不可克隆函数的产生电路,其特征在于,基于所述第一或非门的输出端和所述第二或非门的输出端获取所述物理不可克隆函数。

7.如权利要求1所述的物理不可克隆函数的产生电路,其特征在于,当包括两个或非门时,所述两个与非门包括第一与非门和第二与非门;其中,

8.如权利要求1所述的物理不可克隆函数的产生电路,其特征在于,

技术总结

本发明提供一种物理不可克隆函数的产生电路,包括两个或非门或两个与非门;其中,任意一个或非门/与非门的输出端与另外一个或非门/与非门的其中一个输入端连接;并且,两个或非门/与非门的另外一个输入端分别设置为异步置0端和异步置1端。利用上述发明能够产生稳定且高质量的物理不可克隆函数。

技术研发人员:鹿益铭

受保护的技术使用者:昕原半导体(上海)有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!