图像传感器、降低等效电容方法和存储介质与流程

本申请涉及图像传感器,具体涉及一种图像传感器、像素输出位线的降低等效电容方法和存储介质。

背景技术:

1、在图像传感器(cis)中像素阵列(pixel)输出的像素位线(bitline)走线,从像素阵列到模数转换器(coladc)都需要保护。一般通过将输出位线接地走线进行保护,但是接地保护会引入较大的寄生电容,从而影响像素阵列输出的像素信号的存储速度。

2、在构思及实现本申请过程中,发明人发现至少存在如下问题,如何保证在接地保护情况下的像素信号存储速度,如何降低等效寄生电容以及其对像素输出的影响。

3、前面的叙述在于提供一般的背景信息,并不一定构成现有技术。

技术实现思路

1、本申请提供一种图像传感器、像素输出位线的降低等效电容方法和存储介质,用于缓解等效寄生电容太大影响像素信号存储速度的问题。

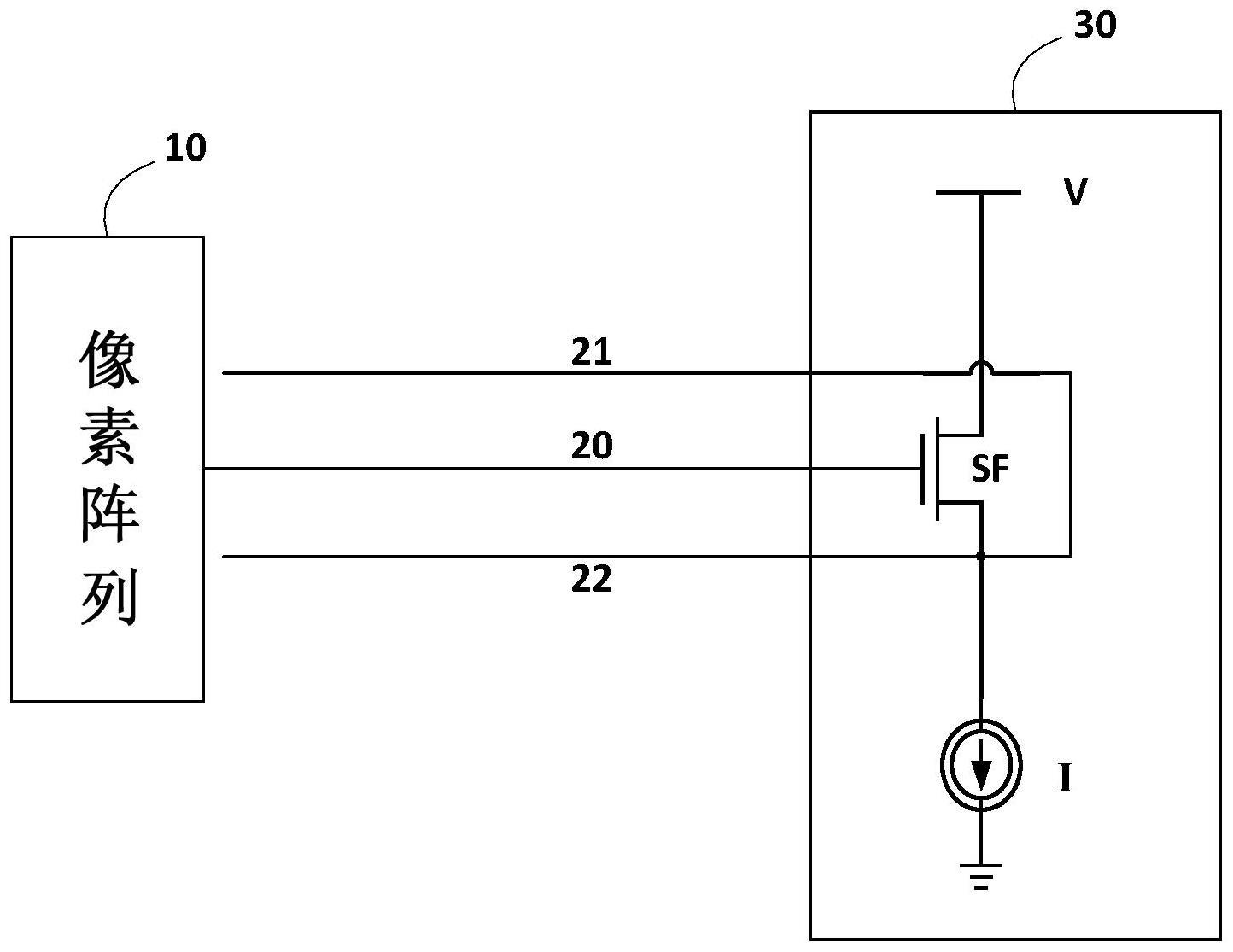

2、在一方面,本申请提供一种图像传感器,可选地,包括像素阵列、像素输出位线和模数转换模块;

3、所述像素阵列通过所述像素输出位线连接所述模数转换模块;

4、所述模数转换模块包括源极跟随晶体管,其中:

5、所述源极跟随晶体管的栅极连接所述像素输出位线,所述源极跟随晶体管的漏极连接预设电压,所述源极跟随晶体管的源极接入电流源;

6、所述源极跟随晶体管的源极还连接源极跟随信号线,且所述源极跟随信号线沿远离所述源极跟随晶体管的源极的相对方向分别包括第一源极跟随信号子线和第二源极跟随信号子线,所述第一源极跟随信号子线和所述第二源极跟随信号子线均与所述像素输出位线平行设置,且所述第一源极跟随信号子线和所述第二源极跟随信号子线分别位于所述像素输出位线的两侧。

7、可选地,所述图像传感器中的所述第一源极跟随信号子线和所述像素输出位线具有第一寄生电容,所述第二源极跟随信号子线和所述像素输出位线具有第二寄生电容,所述第一寄生电容的电容值和所述第二寄生电容的电容值相等。

8、可选地,所述图像传感器中设所述源极跟随晶体管的增益为a,所述第一源极跟随信号子线和所述第二源极跟随信号子线之间的寄生电容为c,则第一寄生电容的电容值和所述第二寄生电容的电容值均为(1-a)*c。

9、可选地,所述图像传感器中的所述源极跟随晶体管的增益介于0到1之间。

10、可选地,所述图像传感器中的所述第一源极跟随信号子线与所述像素输出位线之间的距离与所述第二源极跟随信号子线与所述像素输出位线之间的距离相等。

11、可选地,所述图像传感器中的所述电流源连接在所述源极跟随晶体管和接地信号之间,用于为所述源极跟随晶体管提供恒定的电流。

12、可选地,所述图像传感器中的所述像素阵列包括源级跟随器,所述源级跟随器的源极连接所述像素输出位线。

13、另一方面,本申请提供一种图像传感器中像素输出位线的降低等效电容方法,应用于如上所述的图像传感器,可选地,包括:

14、像素阵列输出像素电压信号;

15、模数转换模块通过像素输出位线获取所述像素电压信号;

16、通过设置于所述模数转换模块中的源极跟随晶体管跟随所述像素电压信号生成源极跟随电压信号;

17、通过设置于所述第一源极跟随信号子线和第二源极跟随信号子线接收所述源极跟随晶体管生成的所述源极跟随电压信号。

18、可选地,所述图像传感器中像素输出位线的降低等效电容方法中设所述源极跟随晶体管的增益为a,所述第一源极跟随信号子线和所述第二源极跟随信号子线之间的寄生电容为c,则第一寄生电容的电容值和所述第二寄生电容的电容值均为(1-a)*c。

19、另一方面,本申请提供一种存储介质,可选地,所述存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现如上述像素输出位线的降低等效电容方法的步骤。

20、如上所述,本申请提供的图像传感器、像素输出位线的降低等效电容方法和存储介质,通过在模数转换模块中加入源极跟随晶体管,将其与像素输出位线两侧的源极跟随信号线连接,不仅能够保护像素输出位线,降低等效寄生电容,还加快信号存储速度。

技术特征:

1.一种图像传感器,其特征在于,包括像素阵列、像素输出位线和模数转换模块;

2.如权利要求1所述的图像传感器,其特征在于,所述第一源极跟随信号子线和所述像素输出位线具有第一寄生电容,所述第二源极跟随信号子线和所述像素输出位线具有第二寄生电容,所述第一寄生电容的电容值和所述第二寄生电容的电容值相等。

3.如权利要求2所述的图像传感器,其特征在于,设所述源极跟随晶体管的增益为a,所述第一源极跟随信号子线和所述第二源极跟随信号子线之间的寄生电容为c,则第一寄生电容的电容值和所述第二寄生电容的电容值均为(1-a)*c。

4.如权利要求3所述的图像传感器,其特征在于,所述源极跟随晶体管的增益介于0到1之间。

5.如权利要求1所述的图像传感器,其特征在于,所述第一源极跟随信号子线与所述像素输出位线之间的距离与所述第二源极跟随信号子线与所述像素输出位线之间的距离相等。

6.如权利要求1所述的图像传感器,其特征在于,所述电流源连接在所述源极跟随晶体管和接地信号之间,用于为所述源极跟随晶体管提供恒定的电流。

7.如权利要求1所述的图像传感器,其特征在于,所述像素阵列包括源级跟随器,所述源级跟随器的源极连接所述像素输出位线。

8.一种图像传感器中像素输出位线的降低等效电容方法,其特征在于,应用于如权利要求1-7任一项所述的图像传感器,包括:

9.如权利要求8所述的图像传感器中像素输出位线的降低等效电容方法,其特征在于,设所述源极跟随晶体管的增益为a,所述第一源极跟随信号子线和所述第二源极跟随信号子线之间的寄生电容为c,则第一寄生电容的电容值和所述第二寄生电容的电容值均为(1-a)*c。

10.一种存储介质,其特征在于,所述存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现如权利要求8或9所述图像传感器中像素输出位线的降低等效电容方法的步骤。

技术总结

本申请提供一种图像传感器、降低等效电容方法和存储介质,图像传感器包括像素阵列、像素输出位线和模数转换模块;所述像素阵列通过所述像素位输出线连接所述模数转换模块;所述模数转换模块包括源极跟随晶体管。本申请提供的图像传感器、降低等效电容方法和存储介质,通过在模数转换模块中加入源极跟随晶体管,将其与像素输出位线两侧的源极跟随信号线连接,不仅能够保护像素输出位线,降低等效寄生电容,还加快信号存储速度。

技术研发人员:陈鹏,李林

受保护的技术使用者:思特威(上海)电子科技股份有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!