一种窄脉冲发生器的制作方法

1.本发明涉及脉冲发生器技术领域,尤其是一种窄脉冲发生器。

背景技术:

2.现有的高精度脉冲信号生成,是通过调节信号边沿位置来实现的。此方法虽然能够实现高精度,但最短脉宽受限,无法做到窄脉冲信号输出。

技术实现要素:

3.针对现有脉冲信号发生技术无法做到窄脉冲信号输出的问题,本发明提出一种窄脉冲发生器。

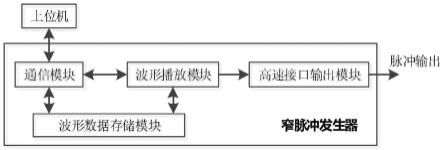

4.一种窄脉冲发生器,包括通信模块、波形数据存储模块、波形播放模块和高速输出接口模块,所述通信模块连接所述波形数据存储模块,并双向连接所述波形播放模块,所述波形数据存储模块连接所述波形播放模块,所述波形播放模块连接所述高速输出接口模块,所述窄脉冲发生器通过所述通信模块与上位机建立数据通信;

5.当所述窄脉冲发生器处于波形存储模式时,上位机对波形进行编码并根据通信协议规则将波形编码打包,通过所述通信模块输入所述波形数据存储模块,所述波形数据存储模块根据上位机发送的数据包中的地址将波形编码存储起来;

6.当所述窄脉冲发生器处于波形播放模式时,上位机通过所述通信模块向所述波形播放模块发送播放指令,所述波形播放模块根据播放指令中的播放地址从所述波形数据存储模块中读取波形编码,并按照编码规则进行对应解码,通过所述高速输出接口模块输出目标波形。

7.进一步的,所述波形数据存储模块在波形存储前,对波形编码是否合规进行检查,仅对合规的波形编码予以存储。

8.进一步的,所述波形编码规则为:每组16位数据为一组,当最高位bit[15]=0,次高位bit[14]=0,表示有连续的高电平;当最高位bit[15]=0,次高位bit[14]=1,表示有连续的低电平,连续电平时长bit[13:0]的数值决定,单位为8ns;当最高位bit[15]=1,直接输出bit[7:0]代表的数据。

[0009]

本发明通过高速输出接口模块输出窄脉冲信号,其最窄脉宽和时间精度与时钟周期无关,仅与高速输出接口模块的传输速率有关,同时为了增大动态范围,结合编码设计,输出宽脉冲信号时,节省存储空间,序列长度不受限制。

附图说明

[0010]

图1为窄脉冲发生器结构框图;

[0011]

图2为实施例1示例波形图。

具体实施方式

[0012]

下面结合附图和具体实施方式对本发明作进一步详细的说明。本发明的实施例是为了示例和描述起见而给出的,而并不是无遗漏的或者将本发明限于所公开的形式。很多修改和变化对于本领域的普通技术人员而言是显而易见的。选择和描述实施例是为了更好说明本发明的原理和实际应用,并且使本领域的普通技术人员能够理解本发明从而设计适于特定用途的带有各种修改的各种实施例。

[0013]

实施例1

[0014]

一种窄脉冲发生器,如图1所示,包括通信模块、波形数据存储模块、波形播放模块和高速输出接口模块,所述通信模块连接所述波形数据存储模块,并双向连接所述波形播放模块,所述波形数据存储模块连接所述波形播放模块,所述波形播放模块连接所述高速输出接口模块,所述窄脉冲发生器通过所述通信模块与上位机建立数据通信。

[0015]

当所述窄脉冲发生器处于波形存储模式时,上位机对波形进行编码并根据通信协议规则将波形编码打包,通过所述通信模块输入所述波形数据存储模块,所述波形数据存储模块根据上位机发送的数据包中的地址将波形编码存储起来。

[0016]

当所述窄脉冲发生器处于波形播放模式时,上位机通过所述通信模块向所述波形播放模块发送播放指令,所述波形播放模块根据播放指令中的播放地址从所述波形数据存储模块中读取波形编码,并按照编码规则进行对应解码,通过所述高速输出接口模块输出目标波形。

[0017]

所述波形数据存储模块在波形存储前,对波形编码是否合规进行检查,仅对合规的波形编码予以存储。

[0018]

波形编码规则并不唯一,本实施例给出其中一种波形编码规则:每组16位数据为一组。当最高位bit[15]=0,次高位bit[14]=0,表示有连续的高电平;当最高位bit[15]=0,次高位bit[14]=1,表示有连续的低电平,连续电平时长bit[13:0] 的数值决定,单位为8ns;当最高位bit[15]=1,直接输出bit[7:0]代表的数据。

[0019]

以图2所示波形为例,其中data是上位机发送的波形编码,signal是高速输出接口模块输出的目标波形。

[0020]

第一个完整的16位数据为0001(0000,0000,0000,0001),其最高位bit[15]=0,次高位bit[14]=0,bit[13:0]的数值为1,则输出波形为1个8ns的高电平。

[0021]

第二个完整的16位数据为8055(1000,0000,0101,0101),其最高位bit[15]=1,则直接输出bit[7:0]代表的数据01010101。

[0022]

显然,所描述的实施例仅仅是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域及相关领域的普通技术人员在没有作出创造性劳动的前提下所获得的所有其他实施例,都应属于本发明保护的范围。显然,所描述的实施例仅仅是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域及相关领域的普通技术人员在没有作出创造性劳动的前提下所获得的所有其他实施例,都应属于本发明保护的范围。

技术特征:

1.一种窄脉冲发生器,其特征在于,包括通信模块、波形数据存储模块、波形播放模块和高速输出接口模块,所述通信模块连接所述波形数据存储模块,并双向连接所述波形播放模块,所述波形数据存储模块连接所述波形播放模块,所述波形播放模块连接所述高速输出接口模块,所述窄脉冲发生器通过所述通信模块与上位机建立数据通信;当所述窄脉冲发生器处于波形存储模式时,上位机对波形进行编码并根据通信协议规则将波形编码打包,通过所述通信模块输入所述波形数据存储模块,所述波形数据存储模块根据上位机发送的数据包中的地址将波形编码存储起来;当所述窄脉冲发生器处于波形播放模式时,上位机通过所述通信模块向所述波形播放模块发送播放指令,所述波形播放模块根据播放指令中的播放地址从所述波形数据存储模块中读取波形编码,并按照编码规则进行对应解码,通过所述高速输出接口模块输出目标波形。2.根据权利要求1所述的窄脉冲发生器,其特征在于,所述波形数据存储模块在波形存储前,对波形编码是否合规进行检查,仅对合规的波形编码予以存储。3.根据权利要求1或2所述的窄脉冲发生器,其特征在于,所述波形编码规则为:每组16位数据为一组,当最高位bit[15]=0,次高位bit[14]=0,表示有连续的高电平;当最高位bit[15]=0,次高位bit[14]=1,表示有连续的低电平,连续电平时长bit[13:0]的数值决定,单位为8ns;当最高位bit[15]=1,直接输出bit[7:0]代表的数据。

技术总结

本发明提供一种窄脉冲发生器,包括通信模块、波形数据存储模块、波形播放模块和高速输出接口模块,所述通信模块连接所述波形数据存储模块,并双向连接所述波形播放模块,所述波形数据存储模块连接所述波形播放模块,所述波形播放模块连接所述高速输出接口模块,所述窄脉冲发生器通过所述通信模块与上位机建立数据通信。本发明通过高速输出接口模块输出窄脉冲信号,其最窄脉宽和时间精度与时钟周期无关,仅与高速输出接口模块的传输速率有关,同时为了增大动态范围,结合编码设计,输出宽脉冲信号时,节省存储空间,序列长度不受限制。序列长度不受限制。序列长度不受限制。

技术研发人员:黄斌 吴亚

受保护的技术使用者:国仪量子(合肥)技术有限公司

技术研发日:2022.07.01

技术公布日:2022/10/4

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1