执行并行图像内核处理的方法和系统与流程

本发明涉及执行图像处理的方法和系统,该方法和系统能够执行图像内核的并行处理,其中所述系统是包括捕获逻辑的处理电路,具有能够对块执行处理的像素处理器,由此所述块包括至少一个内核,其中所述内核是具有相同宽度和高度的像素组。

背景技术:

1、现有技术中执行图像处理的方法之一是按顺序逐个内核地执行内核处理。不可避免地,对任何一般图像或视频数据执行图像处理的持续时间(duration)比预期的要长得多。在现有技术的实施中,逐个内核地处理图像或视频数据的帧,而不经过任何形式的预处理来优化内核处理。除此之外,现有技术的图像处理仅包括一个内核处理器,其中所述内核处理器按顺序处理所述图像或视频数据。图像数据中的所有后续内核都使用相同的内核处理器。

2、因此,通过具有执行图像处理的方法和系统来减轻这些缺点将是有利的,其中该执行图像处理的方法和系统能够执行图像内核的并行处理。

技术实现思路

1、因此,本发明的主要目的是提供一种执行图像处理的方法和系统,该执行图像处理的方法和系统具有更有效的数据处理。

2、本发明的又一个目的是提供一种执行图像处理的方法和系统,执行图像处理的方法和系统使后续的图像处理块(image processing block)能够有效地处理来自本发明的系统的图像数据。

3、本发明的又一个目的是提供一种能够进行并行处理的执行图像处理的方法和系统。

4、通过理解本发明的以下详细描述或在实际实践中使用本发明,本发明的其他目的将变得显而易见。

5、根据本发明的优选实施例,提供以下内容:

6、一种图像或视频处理电路(101),包括:

7、能够从至少一个图像或视频源(105)接收图像或视频数据的至少一个捕获逻辑(103);所述捕获逻辑(103)包括至少一个像素处理器(107);

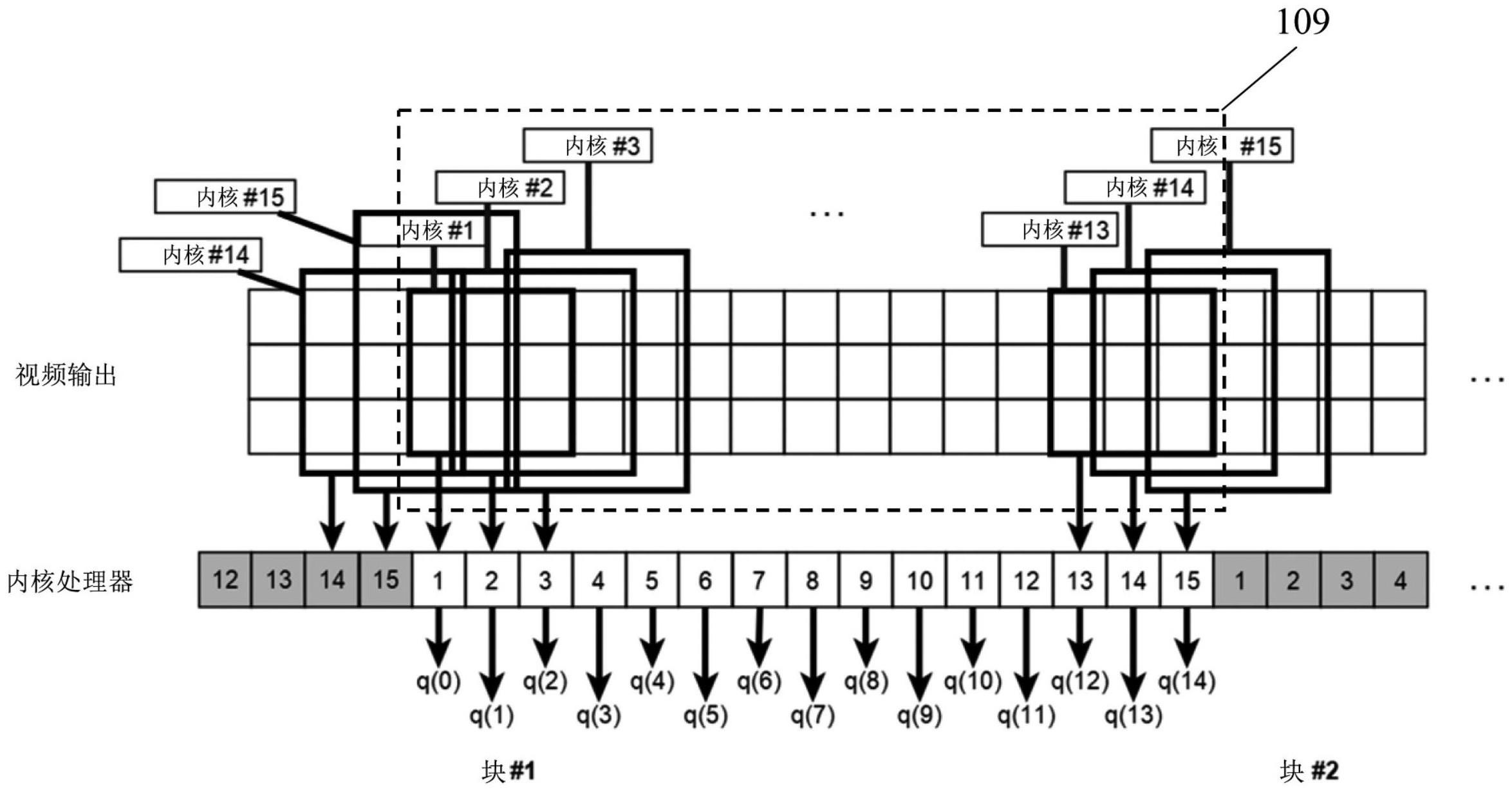

8、其特征在于,

9、其中,所述像素处理器(107)能够对块(109)执行处理;其中,所述块(109)包括至少一个内核(111);其中,所述内核(111)是具有相同宽度和高度的像素组。

10、在本发明的另一个实施例中,提供:

11、一种执行图像或视频处理的方法,包括以下步骤:

12、i.至少一个捕获逻辑(103)从至少一个图像或视频源(105)接收像素图像或视频数据;

13、ii.至少一个像素处理器(107)接收所述图像或视频数据并将像素列存储到至少一个块缓冲区(chunk buffer)中;其中,重复所述接收和存储直到像素块(a chunk ofpixel)(109)被存储在所述块缓冲区中;其中,所述块(109)包括至少一个内核(111);其中,所述内核(111)是具有相同宽度和高度的像素组;

14、iii.在将一个像素块(109)填充到所述块缓冲区中时,所述像素处理器(107)同时将所述像素内核(111)传输到它们各自的内核处理器(113);由此内核处理器(113)的数量与所述块缓冲区中的内核(111)的数量相同;

15、iv.所述内核处理器(113)对所述像素内核(111)执行任何合适的数据处理;

16、其中步骤(i)和(ii)随着步骤(iii)和(iv)的进行而继续,直到预定数量的像素内核(111)被传输和处理。

技术特征:

1.一种图像或视频处理电路(101),包括:

2.如权利要求1所述的图像或视频处理电路(101),其特征在于,所述图像或视频处理电路(101)还包括至少一个内核处理器(113);所述内核处理器(113)能够接收包含在所述像素处理器(107)的所述块(109)中的像素内核(111)并能够处理所述内核(111)。

3.如权利要求1所述的图像或视频处理电路(101),其中,所述捕获逻辑(103)还包括至少一个具有行缓冲区(115)的存储器控制器,该行缓冲区(115)能够执行像素缓冲,在所述捕获逻辑(103)从所述图像或视频源(105)接收所述图像或视频数据之后,所述行缓冲区(115)从所述捕获逻辑(103)接收所述图像或视频数据。

4.如权利要求2所述的图像或视频处理电路(101),其中,内核处理器(113)的数量等于所述块(109)的宽度。

5.如权利要求1所述的图像或视频处理电路(101),其中,所述内核(111)的尺寸为任何合适的奇数高度和宽度的像素或任何合适的偶数高度和宽度的像素,并且所述块(109)的尺寸是8x2像素、20x4像素、15x3像素、15x5像素、35x7像素或任何合适的多个内核(111)的尺寸。

6.一种执行图像或视频处理的方法,包括以下步骤:

7.如权利要求6所述的执行图像处理的方法,在步骤(i)和(ii)之间还包括以下步骤:所述捕获逻辑(103)将像素图像或视频数据的多行存储到具有行缓冲区(115)的至少一个存储器控制器中,逐个像素地填充后续的行,直到在所述行缓冲区(115)中存储预定数量的行。

8.如权利要求7所述的图像处理方法,其中,步骤(ii)包括以下子步骤:

9.如权利要求7所述的执行图像处理的方法,其中,所述行缓冲区包括至少一个存储器阵列。

10.如权利要求7所述的执行图像处理的方法,其中,捕获逻辑(103)将像素图像或视频数据存储到具有行缓冲区(115)的所述存储器控制器中的所述步骤包括以下子步骤:

11.如权利要求7所述的执行图像处理的方法,其中,所述行缓冲区(115)中的所述预定数量的行至少为3行。

12.如权利要求6所述的执行图像处理的方法,其中,像素图像或视频数据从图像或视频源(105)逐个像素地或以像素块传输。

13.如权利要求6所述的执行图像处理的方法,其中,所述内核(111)具有相等的像素宽度和像素高度;所述内核(111)具有与所述块(109)相同的像素高度。

14.如权利要求6所述的执行图像处理的方法,其中,将所述内核处理器(113)的输出传输到另一个内核处理器(113)以用于进一步的数据处理。

15.如权利要求6所述的执行图像处理的方法,其中,所述内核处理器(113)的数据处理是通过基于所述像素内核(111)中的所有像素的值进行计算来完成的。

技术总结

本发明涉及执行图像处理的方法和系统,该执行图像处理的方法和系统能够执行图像内核的并行处理,其中所述系统是包括捕获逻辑(103)的处理电路(101),具有能够对块(109)执行处理的像素处理器(107),其中所述块(109)包括至少一个内核(111),其中所述内核(111)是具有相等宽度和高度的像素组。

技术研发人员:雷质建

受保护的技术使用者:雷质建

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!