有源像素传感器、显示面板、显示装置和平板探测装置的制作方法

1.本技术涉及传感技术领域,尤其涉及一种有源像素传感器、显示面板、显示装置和平板探测装置。

背景技术:

2.目前,有源像素传感器(active pixel sensor,aps)的应用越来越普遍。有源像素传感器的像素驱动电路通常设置于像素区,像素驱动电路通常包括三个半导体晶体管和一个储存电容。然而,这种像素驱动电路会受到像素大小的限制,且该像素驱动电路无法兼容光电导探测器。

技术实现要素:

3.本技术实施例提供一种有源像素传感器、显示面板、显示装置和平板探测装置,以解决或缓解现有技术中的一项或更多项技术问题。

4.作为本技术实施例的第一方面,本技术实施例提供一种有源像素传感器,包括:阵列排布的多个像素电路,各像素电路均包括第一晶体管和用于生成像素信号的像素感测单元,像素感测单元连接于第一晶体管的第一极,其中,第一晶体管的栅极用于连接栅极控制电压;多个共用电路,与多列像素电路一一对应,每列像素电路中的第一晶体管的第二极均连接于该列像素电路所对应的共用电路,共用电路还具有读取控制电压端,读取控制电压端用于连接读取控制电压;其中,在栅极控制电压和读取控制电压满足第一预设条件的情况下,对当前帧像素信号进行第一次采样和第二次采样。

5.在一种实施方式中,像素感测单元在第一次采样和第二次采样之间的复位次数为零。

6.在一种实施方式中,共用电路包括:第二晶体管,第二晶体管的栅极连接于第一晶体管的第二极,第二晶体管的第一极用于连接有源像素传感器的电源电压;第三晶体管,第三晶体管的栅极用于连接读取控制电压,第三晶体管的第一极连接于第二晶体管的第二极,第三晶体管的第二极用于连接读出当前帧像素信号的读出电路;第一电阻,第一电阻的一端用于连接电源电压,第一电阻的另一端连接于第二晶体管的栅极。

7.在一种实施方式中,电源电压包括第一电源电压和第二电源电压,第一电阻连接于第一电源电压,第二晶体管的第一极连接于第二电源电压,其中,第一电源电压小于等于第二电源电压。

8.在一种实施方式中,共用电路还包括:第二电阻,第二电阻的一端用于连接偏置电压,第二电阻的另一端连接于第二晶体管的栅极,其中,第二电阻的阻值与像素感测单元处于未感光状态下的阻值相等。

9.在一种实施方式中,在栅极控制电压为低电平且读取控制电压为高电平的情况下,对当前帧像素信号进行第一次采样;在栅极控制电压为高电平且读取控制电压为高电平的情况下,对当前帧像素信号进行第二次采样。

10.在一种实施方式中,共用电路还具有重置控制电压端,重置控制电压端用于连接重置控制电压,其中,在栅极控制电压和读取控制电压满足第一预设条件,且重置控制电压满足第二预设条件的情况下,对当前帧像素信号进行第一次采样和第二次采样。

11.在一种实施方式中,共用电路包括:第四晶体管,第四晶体管的栅极连接于第一晶体管的第二极,第四晶体管的第一极用于连接电源电压;第五晶体管,第五晶体管的第一极用于连接电源电压,第五晶体管的第二极连接于第四晶体管的栅极,第五晶体管的栅极用于连接重置控制电压;第六晶体管,第六晶体管的栅极用于连接读取控制电压,第六晶体管的第一极连接于第四晶体管的第二极,第六晶体管的第二极连接于读出当前帧像素信号的读出电路;第三电阻,第三电阻的一端用于连接偏置电压,第三电阻的另一端连接于第四晶体管的栅极。

12.在一种实施方式中,在栅极控制电压为低电平、读取控制电压为高电平且重置控制电压为高电平的情况下,对当前帧像素信号进行第一次采样;在栅极控制电压为高电平、读取控制电压为高电平且重置控制电压为低电平的情况下,对当前帧像素信号进行第二次采样。

13.在一种实施方式中,共用电路包括:第七晶体管,第七晶体管的栅极连接于第一晶体管的第二极,第七晶体管的第一极用于连接于电源电压;第八晶体管,第八晶体管的第一极用于连接电源电压,第八晶体管的第二极连接于第七晶体管的栅极,第八晶体管的栅极用于连接重置控制电压;第九晶体管,第九晶体管的栅极用于连接读取控制电压,第九晶体管的第一极连接于第七晶体管的第二极,第九晶体管的第二极连接于读出当前帧像素信号的读出电路;储存电容,储存电容的一端用于连接偏置电压,储存电容的另一端连接于第七晶体管的栅极。

14.在一种实施方式中,共用电路包括:第十晶体管,第十晶体管的栅极用于连接读取控制电压,第十晶体管的第一极连接于读出当前帧像素信号的读出电路;跨阻放大器,跨阻放大器的第一输入端连接于第一晶体管的第二极,跨阻放大器的第二输入端用于连接参考电压,跨阻放大器的输出端连接于第十晶体管的第二极。

15.作为本技术实施例的第二方面,本技术实施例提供一种显示面板,包括根据本技术上述第一方面任一实施方式的有源像素传感器。

16.作为本技术实施例的第三方面,本技术实施例提供一种显示装置,包括根据本技术上述第二方面实施例的显示面板。

17.作为本技术实施例的第四方面,本技术实施例提供一种平板探测装置,包括根据本技术上述第一方面任一实施方式的有源像素传感器。

18.本技术实施例采用上述技术方案可以使共用电路设置于像素区外部,无需受到像素大小的限制,且可以兼容光电导探测器。

19.上述概述仅仅是为了说明书的目的,并不意图以任何方式进行限制。除上述描述的示意性的方面、实施方式和特征之外,通过参考附图和以下的详细描述,本技术进一步的方面、实施方式和特征将会是容易明白的。

附图说明

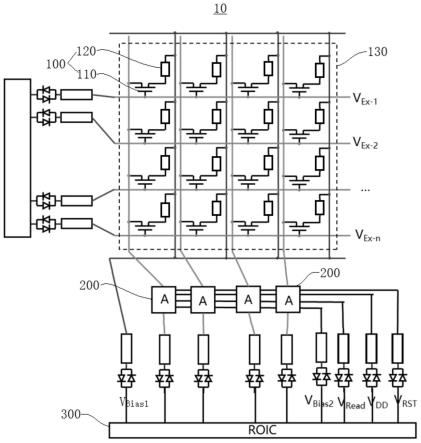

20.在附图中,除非另外规定,否则贯穿多个附图相同的附图标记表示相同或相似的

部件或元素。这些附图不一定是按照比例绘制的。应该理解,这些附图仅描绘了根据本技术公开的一些实施方式,而不应将其视为是对本技术范围的限制。

21.图1示出相关技术中有源像素传感器的电路结构示意图;

22.图2示出相关技术中有源像素传感器的控制时序图;

23.图3示出根据本技术实施例的有源像素传感器的电路结构示意图;

24.图4示出根据本技术第一个实施例的有源像素传感器的电路结构示意图;

25.图5示出根据本技术第一个实施例的有源像素传感器的控制时序图;

26.图6示出根据本技术第二个实施例的有源像素传感器的电路结构示意图;

27.图7示出根据本技术第二个实施例的有源像素传感器的控制时序图;

28.图8示出根据本技术第三个实施例的有源像素传感器的电路结构示意图;

29.图9示出根据本技术第三个实施例的有源像素传感器的控制时序图;

30.图10示出根据本技术第三个实施例的有源像素传感器的一个等效电路图;

31.图11示出根据本技术第四个实施例的有源像素传感器的电路结构示意图;

32.图12示出根据本技术第四个实施例的有源像素传感器的控制时序图;

33.图13示出根据本技术第五个实施例的有源像素传感器的电路结构示意图;

34.图14示出根据本技术第五个实施例的有源像素传感器的控制时序图;

35.图15示出根据本技术第六个实施例的有源像素传感器的电路结构示意图。

具体实施方式

36.在下文中,仅简单地描述了某些示例性实施例。正如本领域技术人员可认识到的那样,在不脱离本技术的精神或范围的情况下,可通过各种不同方式修改所描述的实施例。因此,附图和描述被认为本质上是示例性的而非限制性的。

37.图1示出相关技术中有源像素传感器的电路结构示意图。如图1所示,相关技术中,有源像素传感器的电路结构通常包括位于像素区的三个薄膜晶体管(t1、t2和t3)以及一个储存电容c

pix

。然而,这种电路结构会受像素大小的限制,并且,由于光电导探测器的响应度与其两端的电压相关,如果采用相关技术中有源像素传感器的电路结构,光电导探测器两端的电压会随着光信号的积累发生变化,从而使得光电导探测器出现光响应的非线性问题。因此,相关技术中的有源像素传感器的电路结构无法兼容光电导探测器,无法实现对光电导探测器生成的像素信号的有效读出。

38.图2示出相关技术中有源像素传感器的控制时序图。如图2所示,相关技术中的有源像素传感器的第一次采样cds1和第二次采样cds2之间具有一次复位,使得第一次采样和第二次采样之间的相关性有较大的差异。而且,在第一次采样和第二次采样之间需间隔曝光时间,在该间隔时间内需要对其他行的像素信号进行采样。

39.下面结合图3-图15描述根据本技术第一方面实施例的有源像素传感器10。

40.图3示出根据本技术实施例的有源像素传感器10的电路结构示意图。如图3所示,该有源像素传感器10包括阵列排布的多个像素电路100和多个共用电路200。在本技术的描述中,“多个”的含义是两个或两个以上。

41.各像素电路100均包括第一晶体管110和像素感测单元120,像素感测单元120用于生成像素信号,且像素感测单元120连接于第一晶体管110的第一极,其中,第一晶体管110

的栅极用于连接栅极控制电压v

ex

。

42.例如,在图3的示例中,像素区130包括呈4行4列阵列排布的16个像素电路100。各行像素电路100的第一晶体管110的栅极分别连接于对应的栅极控制电压v

ex

。具体地,第1行的4个像素电路100的第一晶体管110的栅极均连接于v

ex-1

;第2行的4个像素电路100的第一晶体管110的栅极均连接于v

ex-2

;第3行的4个像素电路100的第一晶体管110的栅极均连接于v

ex-3

;第4行的4个像素电路100的第一晶体管110的栅极均连接于v

ex-4

。在各像素电路100中,像素感测单元120的一端可以连接于第一晶体管110的第一极,像素感测单元120的另一端可以用于连接第一偏置电压v

bias1

。

43.可选地,像素感测单元120可以为光电导探测器例如电阻。相较于相关技术中包括三个薄膜晶体管和一个储存电容的有源像素传感器的电路结构,像素感测单元120两端的电压不会由于光信号的积累发生变化,可以避免像素感测单元120例如光电导探测器出现光响应的非线性问题。

44.多个共用电路200与多列像素电路100一一对应,每列像素电路100中的第一晶体管110的第二极均连接于该列像素电路100所对应的共用电路200,共用电路200还具有读取控制电压端,读取控制电压端用于连接读取控制电压v

read

。由此,共用电路200可以设置于像素区130外部,可以无需受到像素大小的限制。

45.例如,在图3的示例中示出了4个共用电路200,4个共用电路200与4列像素电路100一一对应,且4个共用电路200均位于像素区130外部。其中,第1列的4个像素电路100中的第一晶体管110的第二极均连接于第1个共用电路200;第2列的4个像素电路100中的第一晶体管110的第二极均连接于第2个共用电路200;第3列的4个像素电路100中的第一晶体管110的第二极均连接于第3个共用电路200;第4列的4个像素电路100中的第一晶体管110的第二极均连接于第4个共用电路200。其中,第一极和第二极中的其中一个为源极,且第一极和第二极中的另一个为漏极。

46.图3中显示了16个像素电路100和4个共用电路200用于示例说明的目的,但是普通技术人员在阅读了本技术的技术方案之后,显然可以理解将该方案应用到其它数量的像素电路100和共用电路200的技术方案中,这也落入本技术的保护范围之内。

47.在栅极控制电压v

ex

和读取控制电压v

read

满足第一预设条件的情况下,对当前帧像素信号进行第一次采样和第二次采样。

48.示例性地,第一次采样和第二次采样可以为相关双采样(correlated double sample,cds)中的两次采样。第一次采样可以对当前帧像素信号的复位电平进行采样,第二次采样可以对当前帧像素信号的信号电平进行采样,使得第一次采样和第二次采样的噪声电压基本相等,将第二次采样值与第一次采样值相减,可以基本消除复位噪声的干扰,得到信号电平的实际有效幅值,从而有效读出当前帧像素信号。

49.其中,第一次采样对应的第一预设条件和第二次采样对应的第一预设条件可以不同。例如,可以在栅极控制电压v

ex

为低电平且读取控制电压v

read

为高电平的情况下,对当前帧像素信号进行第一次采样,此时第一次采样对应的第一预设条件为:栅极控制电压v

ex

为低电平且读取控制电压v

read

为高电平。在栅极控制电压v

ex

为高电平且读取控制电压v

read

为高电平的情况下,对当前帧像素信号进行第二次采样,此时第二次采样对应的第一预设条件为:栅极控制电压v

ex

为高电平且读取控制电压v

read

为高电平。

50.在一种实施方式中,参照图3、图5、图7和图9,像素感测单元120在第一次采样和第二次采样之间的复位次数为零。如此设置,可以有效减小第一次采样和第二次采样之间的相关性差异,实现真正的相关性采样,从而有效降低读出噪声。而且,第一次采样和第二次采样之间可以无需间隔曝光时间,可以有效减小第一次采样和第二次采样的时间间隔,极大地压缩了每一帧所需时间,可以实现超高的帧频,使有源像素传感器10可以应用于高速探测领域。

51.在一种实施方式中,如图4和图5所示,共用电路200包括第二晶体管210、第三晶体管220和第一电阻230。其中,第二晶体管210的栅极连接于第一晶体管110的第二极,第二晶体管210的第一极用于连接有源像素传感器10的电源电压v

dd

。第三晶体管220的栅极用于连接读取控制电压v

read

,第三晶体管220的第一极连接于第二晶体管210的第二极,第三晶体管220的第二极用于连接读出当前帧像素信号的读出电路(read out integrated circuit,roic)300。第一电阻230的一端(例如,图4中的上端)用于连接电源电压v

dd

,第一电阻230的另一端(例如,图4中的下端)连接于第二晶体管210的栅极。

52.示例性地,第二晶体管210和第一电阻230可以组成放大电路。第二晶体管210的栅极和第一晶体管110的第二极可以通过连接支路连接。第一电阻230与连接支路的连接点为g点,g点电位即为第二晶体管210的栅极电位。像素感测单元120例如光电导探测器的一端可以连接于第一晶体管110的第一极,光电导探测器的另一端可以用于连接第一偏置电压v

bias1

。

53.具体的工作过程可以为:首先栅极控制电压v

ex

开启低电平,使第一晶体管110断开,此时可以隔断像素感测单元120例如光电导探测器和共用电路200,g点电位被复位至初始电位v

dd

,即vg=v

dd

。在g点电位复位的过程中,读取控制电压v

read

开启高电平,对当前帧像素信号进行第一次采样cds1作为参比信号。在g点电位完成复位后,栅极控制电压v

ex

开启高电平,使第一晶体管110打开,对当前帧像素信号进行第二次采样cds2作为像素感测的信号。此时g点电位v

g-signal

取决于光电导探测器处于感光状态下的阻值r、第一晶体管110的开态阻值r

t1-on

、第一电阻230的阻值rc以及第一偏置电压v

bias1

与电源电压v

dd

的电势差,

54.其中,为保证光电导探测器的漏流小于1pa(10-12

a),光电导探测器的阻值r大于10

12

ω。第一晶体管110的开态电阻r

t1-on

大于等于106ω小于107ω。而且,第一电阻230的阻值rc远小于光电导探测器的阻值r。因此,rc与r

t1-on

之和远小于r,上述g点电位其中,为光电导探测器在固定电压下的光电流i

p

,即其中a为光电导探测器的电流响应系数,q为光信号量。因此,第一次采样与第二次采样的信号差δvg=a

·q·

rc。重复上述过程,可以读取后续行的像素信息。

55.其中,读出电路300可以包括电容反馈跨阻放大器、低通滤波器(low pass filter,lpf)、相关双采样(correlated double sample,cds)芯片、模拟数字转换器(analog-to-digital converter,adc)、数据转化器(data processing)和低电压差分信号

(low voltage differential signaling,lvds)接口。其中,电容反馈跨阻放大器可以包括电容c

fb

和放大器amp,c

fb

积累电荷,输出电压信号vout。lpf用于滤掉高频噪声。cds芯片用于进行第一次采样和第二次采样,并计算出第一次采样与第二次采样的信号差δvg。adc用于将模拟电压信号转化为数字电压信号。data processing用于将并行数据转化为串行数据。lvds用于将信号输出。

56.本实施例中,通过设置上述的第二晶体管210、第三晶体管220和第一电阻230,可以实现对像素感测单元120例如光电导探测器生成的像素信号的有效读取,解决了光电导探测器的非线性问题。

57.在上述示例中,以电源电压v

dd

信号为一个为例进行说明。当然,本技术不限于此,在另一种实施方式中,参照图6和图7并结合图3,电源电压v

dd

可以包括第一电源电压v

dr

和第二电源电压v

ds

,第一电阻230连接于第一电源电压v

dr

,第二晶体管210的第一极连接于第二电源电压v

ds

,其中,第一电源电压v

dr

小于等于第二电源电压v

ds

。由此,可以将电源电压v

dd

信号拆分为第一电源电压v

dr

信号和第二电源电压v

ds

信号,此时同样可以实现对像素感测单元120例如光电导探测器生成的像素信号的有效读取,解决了光电导探测器的非线性问题。

58.在一种实施方式中,参照图8和图9,共用电路200还包括第二电阻240,第二电阻240的一端(例如,图8中的下端)用于连接偏置电压,第二电阻240的另一端(例如,图8中的上端)连接于第二晶体管210的栅极,其中,第二电阻240的阻值r

c2

与像素感测单元120处于未感光状态下的阻值r

dark

相等。

59.例如,在图8和图9的示例中,光电导探测器的一端可以连接于第一晶体管110的第一极,光电导探测器的另一端可以用于连接第一偏置电压v

bias1

。第二电阻240的一端用于连接第二偏置电压v

bias2

,第二电阻240的另一端连接于g点。此时工作过程可以为:首先栅极控制电压v

ex

开启低电平,使第一晶体管110断开,此时可以隔断像素感测单元120例如光电导探测器和共用电路200,g点电位被复位至初始电位v

g-dark

,v

g-dark

=v

dr-i

dark

rc。在g点电位复位的过程中,读取控制电压v

read

开启高电平,对当前帧像素信号进行第一次采样cds1作为参比信号,参比信号包括光电导探测器的漏电流信号。与上述实施例相类似,rc与r

t1-on

之和远小于r。此时为光电导探测器在固定电压下的光电流,即i

dark

为光电导探测器的暗电流,即光电导探测器处于未感光状态下的电流。

60.在g点电位完成复位后,栅极控制电压v

ex

开启高电平,使第一晶体管110打开,对当前帧像素信号进行第二次采样cds2作为像素感测的信号。此时等效电路如图10所示,g点电位v

g-signal

=v

dr-(i

p

+i

dark

)rc=v

dr-(a

·

q+2i

dark

)rc。在相关双采样中引入倍增因子2,第一次采样与第二次采样的信号差δvg=v

g-signal-2v

g-dark

=a

·q·

rc。重复上述过程,可以读取后续行的像素信息。

61.本实施例中,通过设置上述的第二电阻240,可以充分考虑像素感测单元120例如光电导探测器的暗电流的影响,同时减小第一电阻230对光电导探测器的影响,保证第一次

采样的参比信号可以为光电导探测器的初始信号,从而有效降低读出噪声。

62.在一种实施方式中,结合图3、图11和图12,共用电路200还可以具有重置控制电压端,重置控制电压端用于连接重置控制电压v

rst

,其中,在栅极控制电压v

ex

和读取控制电压v

read

满足第一预设条件,且重置控制电压v

rst

满足第二预设条件的情况下,对当前帧像素信号进行第一次采样和第二次采样。

63.示例性地,第一次采样对应的第一预设条件和第二次采样对应的第一预设条件可以不同,且第一次采样对应的第二预设条件和第二次采样对应的第二预设条件可以不同。例如,可以在栅极控制电压v

ex

为低电平、读取控制电压v

read

为高电平且重置控制电压v

rst

为高电平的情况下,对当前帧像素信号进行第一次采样。此时第一次采样对应的第一预设条件为:栅极控制电压v

ex

为低电平且读取控制电压v

read

为高电平;第一次采样对应的第二预设条件为:重置控制电压v

rst

为高电平。

64.在栅极控制电压v

ex

为高电平、读取控制电压v

read

为高电平且重置控制电压v

rst

为低电平的情况下,对当前帧像素信号进行第二次采样。此时第二次采样对应的第一预设条件为:栅极控制电压v

ex

为高电平且读取控制电压v

read

为高电平;第二次采样对应的第二预设条件为:重置控制电压v

rst

为低电平。

65.由此,可以通过控制栅极控制电压v

ex

、读取控制电压v

read

和重置控制电压v

rst

对当前帧像素信号进行相关双采样,从而可以得到信号电平的实际有效幅值,有效读出当前帧像素信号。

66.在一种实施方式中,如图11和图12所示,共用电路200包括第四晶体管250、第五晶体管260、第六晶体管270和第三电阻280。具体而言,第四晶体管250的栅极连接于第一晶体管110的第二极,第四晶体管250的第一极用于连接电源电压v

dd

。第五晶体管260的第一极用于连接电源电压v

dd

,第五晶体管260的第二极连接于第四晶体管250的栅极,第五晶体管260的栅极用于连接重置控制电压v

rst

。第六晶体管270的栅极用于连接读取控制电压v

read

,第六晶体管270的第一极连接于第四晶体管250的第二极,第六晶体管270的第二极连接于读出当前帧像素信号的读出电路300。第三电阻280的一端(例如,图11中的下端)用于连接偏置电压例如第二偏置电压v

bias2

,第三电阻280的另一端(例如,图11中的上端)连接于第四晶体管250的栅极。

67.示例性地,第四晶体管250和第五晶体管260可以组成源随电路。第四晶体管250的栅极和第五晶体管260的第二极可以通过连接支路相连。第三电阻280与连接支路的连接点为g点,g点电位即为第四晶体管250的栅极电位。光电导探测器的一端可以连接于第一晶体管110的第一极,光电导探测器的另一端可以用于连接第一偏置电压v

bias1

。

68.具体的工作过程可以为:首先栅极控制电压v

ex

开启低电平,使第一晶体管110断开,此时可以隔断像素感测单元120例如光电导探测器和共用电路200,重置控制电压v

rst

开启高电平,使第五晶体管260打开,g点电位被复位至初始电位vg。vg取决于第五晶体管260的开态阻值r

t2-on

、第三电阻280的阻值rc以及电源电压v

dd

与第二偏置电压v

bias2

的电势差,的电势差,其中,v

bias2

≤v

dd

。为简化计算,以v

bias2

=v

dd

为例进行说明。此时vg=v

bias2

=v

dd

。在g点电位复位过程中,读取控制电压v

read

开启高电平,对当前帧像素信号进行第一次采样cds1作为参比信号。

69.在g点电位完成复位后,重置控制电压v

rst

开启低电平,使第五晶体管260断开,栅极控制电压v

ex

开启高电平,第一晶体管110打开,随后对当前帧像素信号进行第二次采样cds2作为像素感测的信号。此时g点电位v

g-signal

取决于光电导探测器感光后的阻值r、第一晶体管110的开态阻值r

t1-on

、第三电阻280的阻值rc以及第一偏置电压v

bias1

与第二偏置电压v

bias2

的电势差,类似地,由于rc与r

t1-on

之和远小于r,则其中,为光电导探测器在固定电压下的光电流i

p

,即因此,第一次采样与第二次采样的信号差δvg=a

·q·

rc。重复上述过程,可以读取后续行的像素信息。

70.本实施例中,通过设置上述的第四晶体管250、第五晶体管260、第六晶体管270和第三电阻280,同样可以实现对像素感测单元120例如光电导探测器生成的像素信号的有效读取,解决了光电导探测器的非线性问题。

71.在一种实施方式中,如图13和图14所示,共用电路200包括第七晶体管20a、第八晶体管20b、第九晶体管20c和储存电容20d。具体地,第七晶体管20a的栅极连接于第一晶体管110的第二极,第七晶体管20a的第一极用于连接于电源电压v

dd

。第八晶体管20b的第一极用于连接电源电压v

dd

,第八晶体管20b的第二极连接于第七晶体管20a的栅极,第八晶体管20b的栅极用于连接重置控制电压v

rst

。第九晶体管20c的栅极用于连接读取控制电压v

read

,第九晶体管20c的第一极连接于第七晶体管20a的第二极,第九晶体管20c的第二极连接于读出当前帧像素信号的读出电路300。储存电容20d的一端(例如,图13中的下端)用于连接偏置电压例如第二偏置电压v

bias2

,储存电容20d的另一端(例如,图13中的上端)连接于第七晶体管20a的栅极。

72.例如,在图13和图14的示例中,首先栅极控制电压v

ex

开启低电平,使第一晶体管110断开,此时可以隔断像素感测单元120例如光电导探测器和共用电路200,重置控制电压v

rst

开启高电平,使第八晶体管20b打开,g点电位被复位至初始电位。在g点电位完成复位后,读取控制电压v

read

开启高电平,对当前帧像素信号进行第一次采样cds1作为参比信号。随后,栅极控制电压v

ex

开启高电平,使第一晶体管110打开,维持预设时间(即曝光时间t

ex

)。然后栅极控制电压v

ex

开启低电平,使第一晶体管110断开,对当前帧像素信号进行第二次采样cds2作为像素感测的信号。重复上述过程,可以读取后续行的像素信息。

73.本实施例中,通过设置上述的第七晶体管20a、第八晶体管20b、第九晶体管20c和储存电容20d,由于储存电容20d位于像素单元外部,从而可以具有较大的空间用于放置足够大的储存电容20d,储存电容20d大小不再受像素大小限制,从而可以更好配合平板探测装置读出的大电荷量,降低平板探测装置读出信号的信噪比,进而可以提高成像质量。

74.在一种实施方式中,如图15所示,共用电路200包括第十晶体管20e和跨阻放大器20f(trans-impedance amplifier,tia)。其中,第十晶体管20e的栅极用于连接读取控制电压v

read

,第十晶体管20e的第一极连接于读出当前帧像素信号的读出电路300。跨阻放大器20f的第一输入端连接于第一晶体管110的第二极,跨阻放大器20f的第二输入端用于连接参考电压vref1,跨阻放大器20f的输出端连接于第十晶体管20e的第二极。例如,跨阻放大器20f可以为电容反馈跨阻放大器(ctia)20f。跨阻放大器20f可以包括电容c

fd

和放大器

amp,电容c

fd

用于积累并储存电荷数据。第十晶体管20e可以控制共用电路200与读出电路300的连通与隔断,从而控制像素信号的读出。

75.由此,通过设置上述的第十晶体管20e和跨阻放大器20f,同样可以实现对像素感测单元120例如光电导探测器生成的像素信号的有效读取。

76.根据本技术第二方面实施例的显示面板,包括根据本技术上述第一方面任一实施方式的有源像素传感器10。

77.根据本技术第三方面实施例的显示装置,包括根据本技术上述第二方面实施例的显示面板。

78.根据本技术第四方面实施例的平板探测装置,包括根据本技术上述第一方面任一实施方式的有源像素传感器10。

79.上述实施例的显示面板、显示装置和平板探测装置的其他构成可以采用于本领域普通技术人员现在和未来知悉的各种技术方案,这里不再详细描述。

80.在本说明书的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”、“顺时针”、“逆时针”、“轴向”、“径向”、“周向”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。

81.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者多个该特征。

82.在本技术中,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”、“固定”等术语应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,也可以是电连接,还可以是通信;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本技术中的具体含义。

83.在本技术中,除非另有明确的规定和限定,第一特征在第二特征之“上”或之“下”可以包括第一和第二特征直接接触,也可以包括第一和第二特征不是直接接触而是通过它们之间的另外的特征接触。而且,第一特征在第二特征“之上”、“上方”和“上面”包括第一特征在第二特征正上方和斜上方,或仅仅表示第一特征水平高度高于第二特征。第一特征在第二特征“之下”、“下方”和“下面”包括第一特征在第二特征正上方和斜上方,或仅仅表示第一特征水平高度小于第二特征。

84.上文的公开提供了许多不同的实施方式或例子用来实现本技术的不同结构。为了简化本技术的公开,上文中对特定例子的部件和设置进行描述。当然,它们仅仅为示例,并且目的不在于限制本技术。此外,本技术可以在不同例子中重复参考数字和/或参考字母,这种重复是为了简化和清楚的目的,其本身不指示所讨论各种实施方式和/或设置之间的关系。

85.以上,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到其各种变化或替换,这些都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1