基于SIP的采样处理光传输组件的制作方法

基于sip的采样处理光传输组件

技术领域

1.本发明涉及信号传输技术领域,具体是一种基于sip的采样处理光传输组件。

背景技术:

2.目前常用的采样处理光收发系统中,数字光收发功能单元和采样处理系统单元各自采用不同的封装形式、接口互连、处理单元,使得整个系统集成化极低,从而导致产品形式体积和重量大,往往需要一个6u板卡或机箱设备才能实现。且传统的数字光收发产品和采样处理系统产品中,采样处理链路和数字光收发处理链路是独立传输,不能充分发挥各自的优势,无法满足多功能的复杂电子的应用需求。

3.采用现有技术实现的数字光产品和采样系统产品,硬件难度大、结构形式复杂、软件控制不易,大大降低了整个系统的可靠性;安装方式为焊接,拆装过程复杂且易损伤系统组件,无法满足高密度阵列使用的发展趋势。

4.目前常用的采样处理光收发系统存在的问题,主要有:

5.(1)集成化低、体积和重量大;

6.(2)功能单一,应用受限;

7.(3)可靠性差,拆装难度大。

技术实现要素:

8.为了解决现有采样处理光传输系统在传输中存在的问题,本发明提供一种基于sip的采样处理光传输组件,该组件结合了采样处理系统和数字光传输系统的各自优势,通过高密度多层基板技术、多芯片互联技术和三维立体集成技术等系统封装技术将光器件和电子器件进行无缝集成,大大缩减了设备的体积和重量,实现采样处理和光传输功能。

9.本发明具体是通过以下技术方案来实现的,依据本发明提出的一种基于sip的采样处理光传输组件,包括封装壳体、基板、毛纽扣连接器和fa光纤阵列,所述封装壳体包括下壳体和上盖板,基板安装在封装壳体中并位于上盖板内侧,基板靠近上盖板的一侧设置有电源芯片、mcu芯片、a/d转换芯片、时钟芯片、驱动芯片和vcsel芯片,基板另一侧通过毛纽扣连接器实现与光传输组件外部电气互连;光传输组件下壳体一侧引出mt连接器,mt连接器通过光纤带与fa光纤阵列互连,fa光纤阵列与vcsel芯片互连,vcsel芯片通过fa阵列光纤的直接光耦合以及mt连接器实现与光传输组件外部光信号互连。

10.本发明通过以上技术方案将采样处理系统和数字光传输系统进行混合集成,实现了多通道、高集成、数模混合的采样处理和光传输等功能,减少了接口互连、降低了系统结构和软件难度,大大提高了系统的可靠性;通过使用毛纽扣电连接器实现触点接触互连,大大降低了拆装难度,提升了系统的可维修性。

11.进一步地,所述vcsel芯片与驱动芯片互连,驱动芯片和时钟芯片均与a/d转换芯片互连,a/d转换芯片、时钟芯片、驱动芯片还均与mcu芯片互连,电源芯片与基板上的芯片均互连用于提供电源支持。通过以上技术方案将驱动芯片、vcsel芯片、a/d转换芯片、电源

芯片、时钟芯片和mcu控制单元等裸芯片通过系统级封装(sip)技术集成在一个特定封装中,构成一个三维立体结构的高密度、多功能模块化的光传输系统,使其具有接口简单,互连方便,集成度高等特性。

12.进一步地,所述光传输组件通过mcu芯片配置a/d转换芯片和时钟芯片,完成采样数据的模数转换,通过mcu芯片配置驱动芯片,利用vcsel芯片完成差分数字电信号转换为光信号,通过mcu芯片对外部低速信号接口完成组件功能控制和状态监控。

13.进一步地,所述mcu芯片、电源芯片、a/d转换芯片、时钟芯片、驱动芯片和vcsel芯片均采用裸片,裸片通过固晶、引线键合工艺实现与封装基板的电气连接。

14.进一步地,组件外部的射频模拟信号、时钟信号、低速信号和dc供电信号均通过毛纽扣连接器与基板实现互连,射频模拟信号作为采集信号经过基板上的处理电路进行滤波处理转变为差分信号,然后采用a/d转换芯片和时钟芯片在mcu的配置下转换为高速差分数字信号;高速差分数字信号经驱动芯片和vcsel芯片转换为高速数字光信号,高速数字光信号经过fa阵列光纤通过mt连接器实现与组件外部光信号互连。通过以上方案实现了采样数据的高速远距离传输,满足现有军民领域光电信息技术迅猛发展的需求。

15.进一步地,所述低速信号通过毛纽扣连接器与基板上的mcu芯片互连,完成信息交互。

16.进一步地,所述毛纽扣连接器包括第一毛纽扣、第二毛纽扣和第三毛纽扣,通过第一毛纽扣传输低速信号和电源信号,通过第二毛纽扣传输时钟信号,通过第三毛纽扣传输射频模拟信号。

17.进一步地,所述射频模拟信号采用共面波导形式,射频模拟信号阻抗为50ω,驻波比≤1.5,插入损耗≤0.3db。

18.进一步地,所述光传输组件将采样处理系统和数字光传输系统进行集成,采样处理系统的电接口由基板背部的毛纽扣电连接器组引出,数字光传输系统的光接口由下壳体一侧的mt连接器引出。

19.进一步地,所述数字光传输系统采用vcsel芯片实现电光转换,通过驱动芯片的驱动电流和消光比进行温度补偿设计,数字光中心波长850nm,传输速率≤10.3125gbps,光纤经并带合束后在基板中心处引出,其接口为mt连接器。

20.本发明与现有技术相比具有明显的优点和有益效果。借由上述技术方案,本发明一种基于sip的采样处理光传输组件可达到相当的技术进步性及实用性,并具有广泛的利用价值,其至少具有下列优点:

21.(1)本发明将驱动芯片、vcsel芯片、a/d转换芯片、电源芯片、时钟芯片和mcu控制单元等裸芯片通过系统级封装(sip:system in package)技术集成在一个特定封装中,构成一个三维立体结构的高密度、多功能模块化的光传输系统,射频模拟信号作为采集信号经毛纽扣电连接器输入,经过a/d转换和电光转换,最终通过光纤发送,实现采样数据的高速远距离传输。通过使用毛纽扣电连接器实现触点接触互连,大大降低了拆装难度,提升了系统的可维修性,充分满足阵列化使用需求。

22.(2)本发明光传输组件整体结构设计具有接口简单,互连方便,集成度高等特性,同时通过mcu芯片具备的软件健康管理模块可以对组件的温度、工作电压、发射光功率等指标进行实时上报,有效提高产品的可靠性。

23.(3)本发明首次将采样处理系统和数字光传输系统进行混合集成,实现了多通道、高集成、数模混合的采样处理和光传输等功能,减少了接口互连、降低了系统结构和软件难度,大大提高了系统的可靠性;是未来采样处理光通信领域的颠覆性技术,将广泛应用于军民各个领域,包括雷达通信、电子对抗等国防领域和数字中心、移动通信等民用领域。

附图说明

24.图1是本发明光传输组件的外形图,其中,(a)是光传输组件的前视图,(b)是(a)的俯视图,(c)是(a)的仰视图,(d)是(a)的右视图;

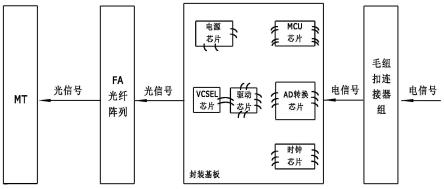

25.图2是本发明光传输组件的结构框图;

26.图3是本发明光传输组件的功能框图。

27.【元件及符号说明】:

28.1-基板;

29.2-下壳体;

30.3-上盖板;

31.4-mt连接器;

32.5-第一毛纽扣;

33.6-第二毛纽扣;

34.7-第三毛纽扣。

具体实施方式

35.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合具体实施例以及附图,对本发明的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部实施例。通常在此处附图中的描述和所示的实施例可以通过各种不同的配置来实现。因此,以下对在附图中提供的本发明的实施例的详细描述并非旨在限制要求保护的范围,而是仅仅表示本发明选定的实施例。基于本发明的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

36.本发明提供的一种基于sip的采样处理光传输组件,至少包括封装壳体、基板1、毛纽扣连接器和fa光纤阵列,封装壳体包括下壳体2和上盖板3,基板安装在封装壳体中位于上盖板内侧,基板靠近上盖板的一侧设置有mcu芯片、电源芯片、a/d转换芯片、时钟芯片、驱动芯片和vcsel芯片,vcsel芯片通过fa阵列光纤的直接光耦合以及mt连接器实现与光传输组件外部的光信号连接。所述的mcu芯片、电源芯片、a/d转换芯片、时钟芯片、驱动芯片和vcsel芯片均采用裸片,裸片通过固晶、引线键合工艺,实现功能芯片与封装基板的电气连接。封装基板通过其另一侧的毛纽扣连接器实现与光传输组件外部电气互连。

37.具体地,所述光传输组件下壳体一侧引出mt连接器4,mt连接器通过光纤带与fa光纤阵列互连,fa光纤阵列与vcsel芯片互连,vcsel芯片与驱动芯片互连。mcu芯片与a/d转换芯片、时钟芯片、驱动芯片均互连,a/d转换芯片还与驱动芯片和时钟芯片互连。电源芯片与基板上的芯片均互连用于提供电源支持。

38.光传输组件通过mcu芯片配置a/d转换芯片和时钟芯片,完成采样数据的模数转

换,通过mcu芯片配置驱动芯片,并利用vcsel芯片完成差分数字电信号转换为光信号,光传输组件通过mcu芯片对外部低速信号接口完成组件功能控制和状态监控。

39.基于系统封装(sip)技术的采样处理光传输组件可以实现采样处理系统和数字光传输系统的集成。采样处理系统的电接口由底部毛纽扣电连接器组引出,数字光传输系统的光接口由下壳体一侧的mt连接器引出。

40.所述采样处理系统将射频单端模拟信号进行滤波处理后转变为差分信号,后采用专用a/d转换芯片(输出符合jesd204b协议)和时钟芯片,在mcu的配置下将模拟信号转换为高速差分数字信号。射频模拟信号用共面波导形式(即毛纽扣连接器到电路处理这一段),数字信号走差分线,经ads计算和hfss仿真,射频模拟信号阻抗为50ω,驻波比≤1.5,插入损耗≤0.3db。

41.所述数字光传输系统采用多模的vcsel芯片实现电光转换,通过驱动芯片的驱动电流和消光比进行温度补偿设计,保证全温范围内光功率的稳定输出。数字光中心波长850nm,传输速率≤10.3125gbps。光纤经并带合束后在基板中心处引出,其接口为mt连接器,保证通道间一致性。

42.下面结合图3对本发明进行详细说明:

43.外部射频模拟信号、时钟信号、低速信号和dc供电信号均通过毛纽扣连接器与基板实现互连,射频模拟信号作为采集信号经过基板上的处理电路进行滤波处理等转变为差分信号,然后采用a/d转换芯片(输出符合jesd204b协议)和时钟芯片在mcu的配置下转换为高速差分数字信号(时钟信号是完成a/d转换功能必须有的一组信号,因此时钟芯片与a/d转换芯片也互连)。高速差分数字信号经驱动芯片和vcsel芯片转换为高速数字光信号。高速数字光信号经过fa阵列光纤通过mt连接器实现与组件外部光信号互连。

44.低速信号通过毛纽扣连接器与基板上的mcu芯片互连,完成信息交互。mcu通过数据接口配置a/d转换芯片和时钟芯片使其正常工作。dc供电信号通过毛纽扣连接器与基板连接,为基板及各芯片提供电源支持。

45.在图1所示的实施例中,毛纽扣连接器包括第一毛纽扣5、第二毛纽扣6和第三毛纽扣7,在一种实施例中,可以通过第一毛纽扣传输低速信号和电源信号,通过第二毛纽扣传输时钟信号,通过第三毛纽扣传输射频模拟信号。

46.本发明利用sip封装技术将驱动芯片、vcsel芯片、a/d转换芯片、时钟芯片、mcu芯片和电源芯片等裸芯片集成封装在一个多层基板上。集成封装时需要通过固晶技术、引线键合技术、光耦合技术、光纤并带技术、射频电路技术和高速数字电路技术等关键技术进行指标优化。高密度多层基板安装在封装壳体内,基板背部通过毛纽扣连接器实现与外部电信号互连,并完成射频模拟信号的采集,通过基板上的时钟芯片和a/d转换芯片将射频模拟信号转换为高速差分数字信号,再经过驱动芯片和vcsel芯片将高速差分数字信号转换为高速数字光信号,通过fa阵列光纤和mt连接器实现光信号输出。

47.本发明具有采样处理系统和数字光传输系统混合集成、超小型化、高集成度、智能化、高可靠性等特点,满足现有军民领域光电信息技术迅猛发展的需求,尤其为防务领域的机载对抗、雷达通信系统中信息光电子技术深入应用提供保障。

48.以上所述仅是本发明的实施例,并非对本发明作任何形式上的限制,本发明还可以根据以上结构和功能具有其它形式的实施例,不再一一列举。因此,任何熟悉本专业的技

术人员,在不脱离本发明技术方案范围内,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化与修饰,均仍属于本发明技术方案的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1