指令发送方法及装置与流程

本申请涉及半导体测试,特别涉及一种指令发送方法及装置、指令接收方法及装置、计算设备、计算机可读存储介质及计算机程序产品。

背景技术:

1、目前ate测试系统中的pcie卡和数据接收端的接口板之间是光纤通信,pcie卡和接口板均采用amd公司的fpga作为核心芯片,通信协议是aurora协议。aurora协议的特点是简单,对于短指令来说,效率很高。但是其缺点是通用性较差,不支持与其他公司的fpga设备通信。因此,当数据接收端的接口板采用其他公司(比如intel公司的arria10型号)的fpga时,pcie卡和接口板无法使用aurora协议通信,此时可以使用通用协议ethernet实现两者通信。

2、当ate测试系统中的数据发送端(即pc)发送大量指令(测试机的所有指令均可以,下面以写指令为例)至数据接收端时(具体的指令发送过程为pc执行pcie软件代码,经过pcie驱动、pcieip传输至pcie的fpga的fifo中缓存,再通过以太网发送至数据接收端),由于pc每次发送的写指令数量都不同,写指令之间的耗时也不相同,发送频次也不一样,pc执行同一段pcie软件代码,在不同时刻发送指令,fpga收到的指令之间的间隔也是不同的,最少10多个周期,最长也有80多个周期。ethernet协议发送最小帧是64字节,若采用ethernet协议一帧数据只包含一个指令的发送情况下,对于指令间隔较短(10多个周期)时,会出现发送不及时,fifo溢出现象,并且以太网发送也会出现数据溢出问题,导致数据丢包,且发送一个指令的耗时比aurora协议更多。这样情况约束了pc发送指令的数量和频次,只有在ethernet协议一帧数据中包含多个写指令才能让ethernet协议通信效率提高,甚至接近于aurora协议的通信效率。

3、在此背景下,如何确定一帧ethernet协议数据中具体包含多少个写指令,才能使pc发送指令的数量、频次不受约束,才能把一帧ethernet协议数据快速发送,提高通信效率,是有待解决的技术问题。

技术实现思路

1、鉴于现有技术的以上问题,本申请提供一种指令发送方法及装置、指令接收方法及装置、计算设备、计算机可读存储介质及计算机程序产品,以使pc发送指令的数量、频次不受约束,通过ethernet协议能提高通信效率。

2、为达到上述目的,本申请第一方面提供了一种指令发送方法,包括:

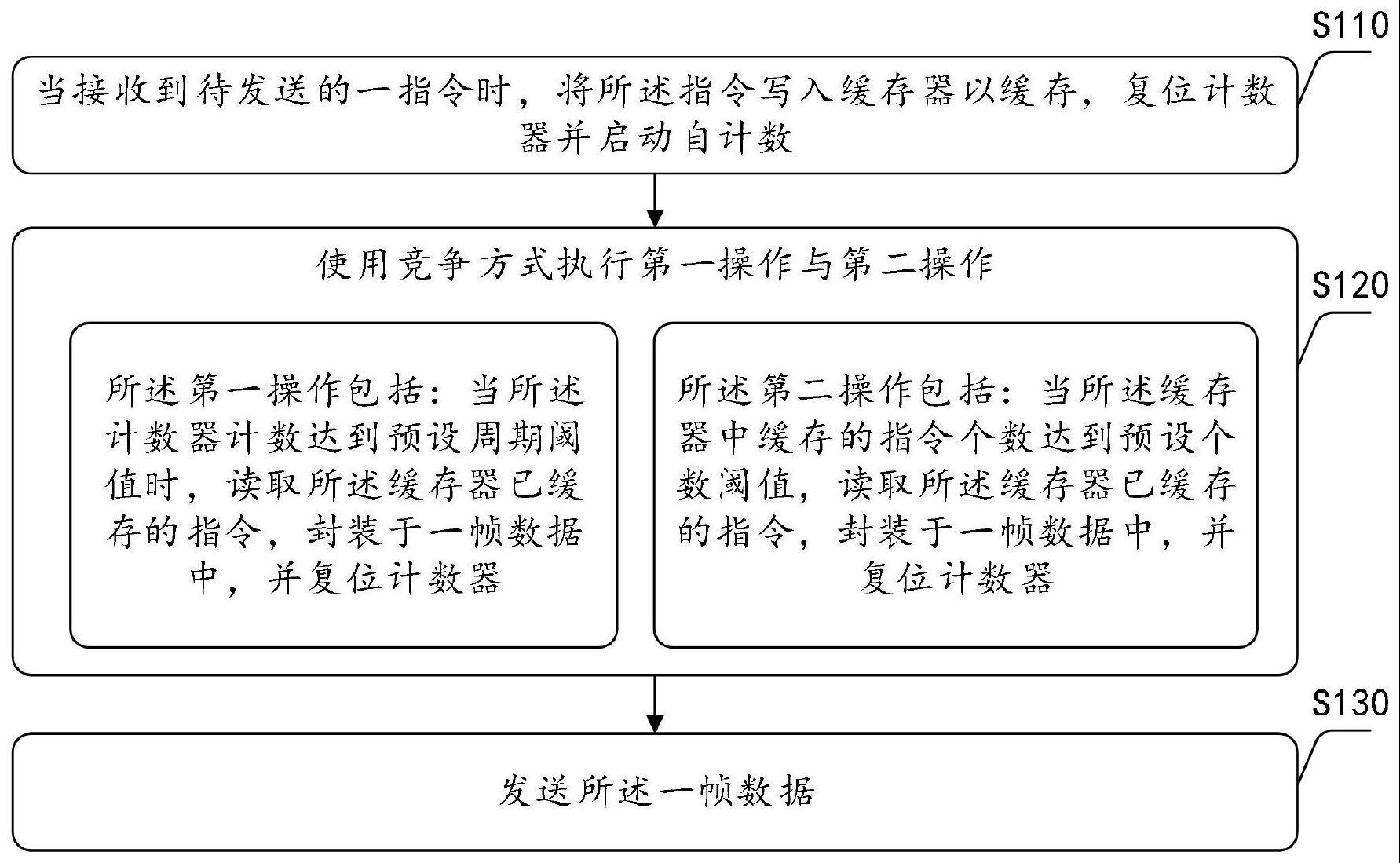

3、当接收到待发送的一指令时,将所述指令写入缓存器以缓存,复位计数器并启动自计数;

4、使用竞争方式执行第一操作与第二操作:

5、所述第一操作包括:当所述计数器计数达到预设周期阈值时,读取所述缓存器已缓存的指令,封装于一帧数据中,并复位计数器;

6、所述第二操作包括:当所述缓存器中缓存的指令个数达到预设个数阈值,读取所述缓存器已缓存的指令,封装于一帧数据中,并复位计数器;

7、发送所述一帧数据。

8、本申请使用自适应机制,使得ethernet协议一帧数据不只是包含一个指令的发送,不论指令之间的间隔周期是多少,都可以高效率发送,使pc发送指令的数量、频次不受约束。

9、本申请第二方面提供了一种指令接收方法,包括:

10、接收通过ethernet协议发送的一帧数据;所述一帧数据包括目标mac地址字段、源mac地址字段、长度字段、指令字段和停止指令字段;

11、对所述目标mac地址字段、源mac地址字段、长度字段进行解析;

12、对所述指令字段和停止指令字段进行解析,判断解析到的为所述停止指令,则停止解析,缓存所述指令,等待下一帧数据;若解析到所述指令,缓存所述指令,继续对所述指令字段和停止指令字段进行解析,直到解析到所述停止指令为止。

13、为达到上述目的,本申请第三方面提供了一种指令发送装置,包括:

14、第一执行单元,用于当接收到待发送的一指令时,将所述指令写入缓存器以缓存,复位计数器并启动自计数;

15、第二执行单元,用于使用竞争方式执行第一操作与第二操作:

16、所述第一操作包括:当所述计数器计数达到预设周期阈值时,读取所述缓存器已缓存的指令,封装于一帧数据中,并复位计数器;

17、所述第二操作包括:当所述缓存器中缓存的指令个数达到预设个数阈值,读取所述缓存器已缓存的指令,封装于一帧数据中,并复位计数器;

18、第三执行单元,用于发送所述一帧数据。

19、为达到上述目的,本申请第四方面提供了一种指令发送装置,包括:

20、缓存模块,包括缓存器,所述缓存器用于缓存待发送的指令;

21、检测模块,用于当写入所述缓存器待发送的指令时使计数器复位并启动自计数,以及当所述缓存器缓存的指令被读取时使计数器复位,以及用于判断计数器计数达到预设周期阈值时或所述缓存器中缓存的指令个数达到预设个数阈值时生成发送信号;

22、发送模块,用于根据所述发送信号读取所述缓存器缓存的指令并封装于一帧数据中发送。

23、本申请使用自适应机制,使得ethernet协议一帧数据不只是包含一个指令的发送,不论指令之间的间隔周期是多少,都可以高效率发送,使pc发送指令的数量、频次不受约束。

24、本申请第五方面提供了一种指令接收装置,包括:

25、数据接收模块,用于接收通过ethernet协议发送的一帧数据;所述一帧数据包括目标mac地址字段、源mac地址字段、长度字段、指令字段和停止指令字段;

26、解析模块,用于对所述目标mac地址字段、源mac地址字段、长度字段进行解析;对所述指令字段和停止指令字段进行解析,判断解析到的为所述停止指令,则停止解析,缓存所述指令,等待下一帧数据;若解析到所述指令,缓存所述指令,继续对所述指令字段和停止指令字段进行解析,直到解析到所述停止指令为止。

27、本申请第六方面提供了一种计算设备,包括:通信接口,以及至少一个处理器;其中,所述至少一个处理器用于执行程序指令,所述程序指令当被所述至少一个处理器执行时使得所述计算设备执行上述第一方面的任一所述的指令发送方法,或者,所述程序指令当被所述至少一个处理器执行时使得所述计算设备实现上述第二方面所述的方法。

28、本申请第七方面提供了一种计算机可读存储介质,其上存储有程序指令,所述程序指令当被计算机执行时使得所述计算机执行上述第一方面的任一所述的指令发送方法,或者,所述程序指令当被所述计算机执行时使得所述计算机实现上述第二方面所述的方法。

29、本申请第八方面提供了一种计算机程序产品,其包括有程序指令,所述程序指令当被计算机执行时使得所述计算机执行上述第一方面的任一所述的指令发送方法,或者,所述程序指令当被所述计算机执行时使得所述计算机实现上述第二方面所述的方法。

技术特征:

1.一种指令发送方法,其特征在于,包括:

2.如权利要求1所述的方法,其特征在于,所述将所述指令写入缓存器以缓存,复位计数器并启动自计数,包括:

3.如权利要求1所述的方法,其特征在于,所述将所述指令写入缓存器以缓存,复位计数器并启动自计数,包括:

4.如权利要求1所述的方法,其特征在于,所述读取所述缓存器已缓存的指令,及所述并复位计数器,包括:

5.如权利要求1所述的方法,其特征在于,所述读取所述缓存器已缓存的指令,及所述并复位计数器,包括:

6.如权利要求1所述的方法,其特征在于,所述一帧数据的总长度为预设的固定长度,所述一帧数据中包括目标mac地址字段、源mac地址字段、长度字段、指令字段和停止指令字段;

7.如权利要求1至6任一项所述的方法,其特征在于,

8.一种指令发送装置,其特征在于,包括:

9.一种指令发送装置,其特征在于,包括:

10.一种计算设备,其特征在于,包括:

技术总结

本申请涉及一种指令发送方法及装置,包括:当接收到待发送的一指令时,将所述指令写入缓存器以缓存,复位计数器并启动自计数;使用竞争方式执行第一操作与第二操作:所述第一操作包括:当所述计数器计数达到预设周期阈值时,读取所述缓存器已缓存的指令,封装于一帧数据中,并复位计数器;所述第二操作包括:当所述缓存器中缓存的指令个数达到预设个数阈值,读取所述缓存器已缓存的指令,封装于一帧数据中,并复位计数器;发送所述一帧数据。本申请可以提高指令的发送效率。

技术研发人员:全斌,张军强

受保护的技术使用者:北京华峰装备技术有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!