一种校正方法与校正装置与流程

本申请涉及信号处理,尤其涉及一种校正方法与校正装置。

背景技术:

1、为了处理高速率通信信号,一些信号处理系统往往使用数字下转换(digitaldown converter,ddc)技术对高速信号进行变频、抽取等操作,使其转换为低速iq(in-phase quadrature,同相正交)信号。这些系统的前端器件,例如功率放大器和模数转换器等器件不可避免地会将非线性杂散引入到接收信号中,造成接收信号的非线性失真,非线性失真分量的存在将会显著影响通信设备的性能。

2、如图1所示,假设非线性系统的输入信号为双音信号,经过射频前端和模数转换器之后,将引入二阶、三阶等非线性失真分量,经过数字下转换器处理之后,截取的带内信号将残留部分非线性失真分量,严重影响非线性系统的整体动态范围等指标。

3、目前,对非线性信号进行分析处理的方法主要针对实信号,即未经过数字下转换器处理的信号。然而,相比于iq信号,实信号的速率高,进行相同的运算所需的计算资源消耗大,不利于在fpga(field programmable gate array,现场可编程逻辑门阵列)等资源有限的嵌入式计算系统中应用。此外,大部分高速模数转换器件内置数字下转换器,为了充分利用芯片本身的计算资源,急需一种针对iq信号的非线性失真的校正方法。

技术实现思路

1、基于现有技术中存在的上述问题,本申请实施例提供了一种校正方法与校正装置,以有效去除带数字下转换器的非线性系统所产生的信号失真。

2、本申请实施例采用下述技术方案:

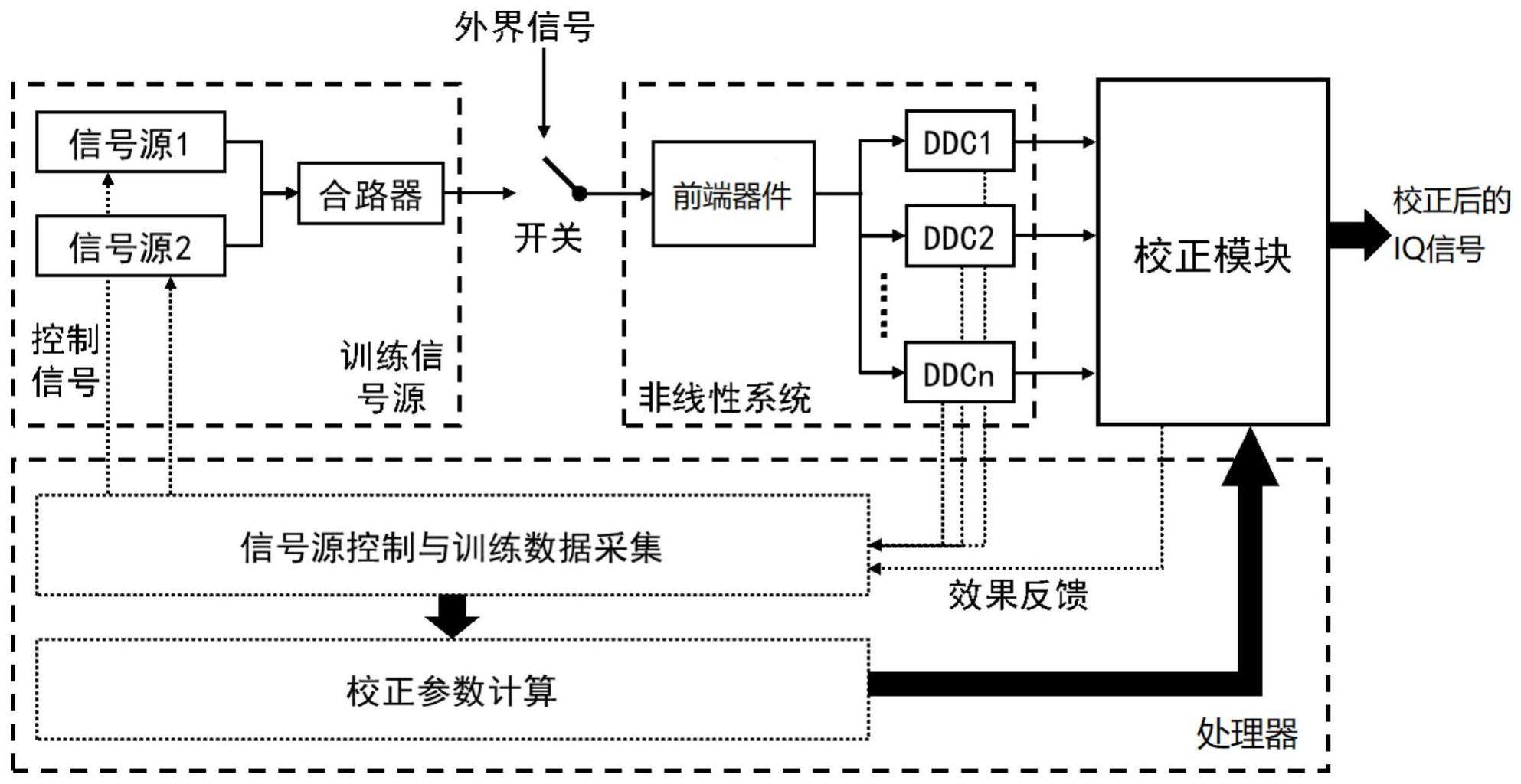

3、第一方面,本申请实施例提供一种校正装置,用于对非线性系统中iq信号的非线性失真分量进行校正,所述非线性系统包括前端器件与数字下转换器,所述校正装置包括:训练信号源、开关、处理器和校正模块;

4、所述训练信号源与外界信号的接收链路通过所述开关与所述非线性系统的前端器件选通连接,所述数字下转换器与所述校正模块连接,所述处理器分别与所述训练信号源、开关、数字下转换器和校正模块连接;

5、所述处理器通过控制所述开关,使所述非线性系统处于训练模式或校正模式,当所述非线性系统处于训练模式时,所述处理器计算所述校正模块的校正参数,并将所述校正参数加载到所述校正模块中;当所述非线性系统处于校正模式时,所述校正模块对所述数字下转换器的输出信号进行非线性校正,得到校正后的iq信号。

6、第二方面,本申请实施例还提供一种校正方法,用于对非线性系统中iq信号的非线性失真分量进行校正,所述非线性系统包括前端器件与数字下转换器,所述校正方法由校正装置的处理器执行,所述校正方法包括:

7、控制所述非线性系统进入训练模式,并控制训练信号源输出训练信号至所述非线性系统;

8、获取所述训练信号与所述非线性系统输出的带有非线性失真的iq训练信号;

9、根据所述训练信号与所述iq训练信号获取校正模块的校正参数,并将所述校正参数加载到所述校正模块中;

10、控制所述非线性系统进入校正模式,利用所述校正模块对所述非线性系统的输出信号进行非线性校正,获取校正后的iq信号。

11、第三方面,本申请实施例还提供一种电子设备,包括:

12、处理器;以及

13、被安排成存储计算机可执行指令的存储器,所述可执行指令在被执行时使所述处理器执行校正方法。

14、第四方面,本申请实施例还提供一种计算机可读存储介质,所述计算机可读存储介质存储一个或多个程序,所述一个或多个程序当被包括多个应用程序的电子设备执行时,使得所述电子设备执行校正方法。

15、本申请实施例采用的上述至少一个技术方案能够达到以下有益效果:本申请实施例为带有数字下转换器的非线性系统设计专用的校正装置,通过校正装置的开关控制非线性系统的前端器件接收训练信号源的训练信号或者接收外界信号,以控制非线性系统进入训练模式或校正模式,当非线性系统进入训练模式时,由校正装置的处理器计算出校正模块的校正参数,由于非线性系统中产生的非线性失真分量是与非线性系统的硬件性能相关,因此,在非线性系统硬件确定的情况下,基于训练信号计算出的校正参数能够校正非线性系统接收外界信号所产生的非线性失真,能够有效去除非线性系统产生的非线性失真信号,整个信号校正过程具有计算复杂度低的优势,能够适用于计算资源紧张的嵌入式环境。

技术特征:

1.一种校正装置,用于对非线性系统中iq信号的非线性失真分量进行校正,所述非线性系统包括前端器件与数字下转换器,其特征在于,所述校正装置包括:训练信号源、开关、处理器和校正模块;

2.如权利要求1所述的校正装置,其特征在于,所述校正模块包括顺次连接的第一数字震荡器、非线性组合校正模块与第二数字振荡器,其中,所述第一数字振荡器的输入端与所述校正模块对应的数字下转换器的输出端连接,所述第二数字振荡器的输出端为所述校正模块的输出端。

3.如权利要求2所述的校正装置,其特征在于,所述非线性组合校正模块包括合路模块、一阶非线性校正模块至n阶非线性校正模块,n为大于1的正整数;

4.如权利要求1所述的校正装置,其特征在于,当所述非线性系统包括一个数字下转换器时,

5.如权利要求1所述的校正装置,其特征在于,当所述非线性系统包括多个数字下转换器时,

6.如权利要求1所述的校正装置,其特征在于,当所述非线性系统包括多个数字下转换器时,所述多个数字下转换器包括第一类数字下转换器和第二类数字下转换器,所述第一类数字下转换器为输出信号受到其他数字下转换器的基频分量影响,所述第二类数字下转换器为输出信号的基频分量影响其他数字下转换器的输出信号;

7.一种校正方法,用于对非线性系统中iq信号的非线性失真分量进行校正,所述非线性系统包括前端器件与数字下转换器,所述校正方法由如权利要求1~6任一项所述的校正装置的处理器执行,所述校正方法包括:

8.如权利要求7所述的校正方法,其特征在于,所述根据所述训练信号与所述iq训练信号获取校正模块的校正参数,包括:

9.如权利要求7所述的校正方法,其特征在于,所述控制训练信号源输出训练信号至所述非线性系统,包括:

10.如权利要求7所述的校正方法,其特征在于,在控制所述非线性系统进入校正模式之后,所述方法还包括:

技术总结

本申请公开了一种校正方法与校正装置。校正装置用于对非线性系统中IQ信号的非线性失真分量进行校正,非线性系统包括前端器件与数字下转换器,校正装置包括训练信号源、开关、处理器和校正模块;训练信号源与外界信号的接收链路通过开关与非线性系统的前端器件选通连接,数字下转换器与校正模块连接,处理器分别与训练信号源、开关、数字下转换器和校正模块连接;处理器通过控制开关使非线性系统处于训练模式或校正模式,当非线性系统处于训练模式时,处理器计算校正参数并加载到校正模块中;当非线性系统处于校正模式时,校正模块对数字下转换器的输出信号进行非线性校正,得到无失真的IQ信号。本申请能够有效去除非线性系统所产生的信号失真。

技术研发人员:陈加锐,陈顺阳

受保护的技术使用者:中国电子科技集团公司第三十六研究所

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!