时间同步授时模块的制作方法

本发明涉及电源转换电路,具体为一种时间同步授时模块。

背景技术:

1、时间同步系统功能上可分为四部分:北斗接收机、天线、电源模块、授时模块。其中,北斗接收机提供时间、定位信息。电源模块将交流输入转换为系统需要的直流输出。天线接收北斗信号放大处理后提供给接收机使用。授时模块具有b码授时、网络授时/定位功能。目前的授时模块的功耗比较高、制造成本高。

技术实现思路

1、本发明的目的在于提供一种时间同步授时模块,功耗低、授时准确、成本低。

2、为实现上述目的,本发明提供了一种技术方案:一种时间同步授时模块,包括授时模块、电源模块,所述电源模块与所述授时模块连接,用于给授时模块供电;

3、所述电源模块包括电磁滤波回路、整流电路、切换电路、整流/滤波电路、pwm控制电路、检测电路;所述电磁滤波回路的输入端接交流电,所述电磁滤波回路的输出端接整流电路的输入端,所述整流电路的输出端接切换电路输入端,所述切换电路的输出端接整流/滤波电路的输入端,所述整流/滤波电路的输出端输出直流电且接所述检测电路的输入端,所述检测电路的输出端接pwm控制电路;

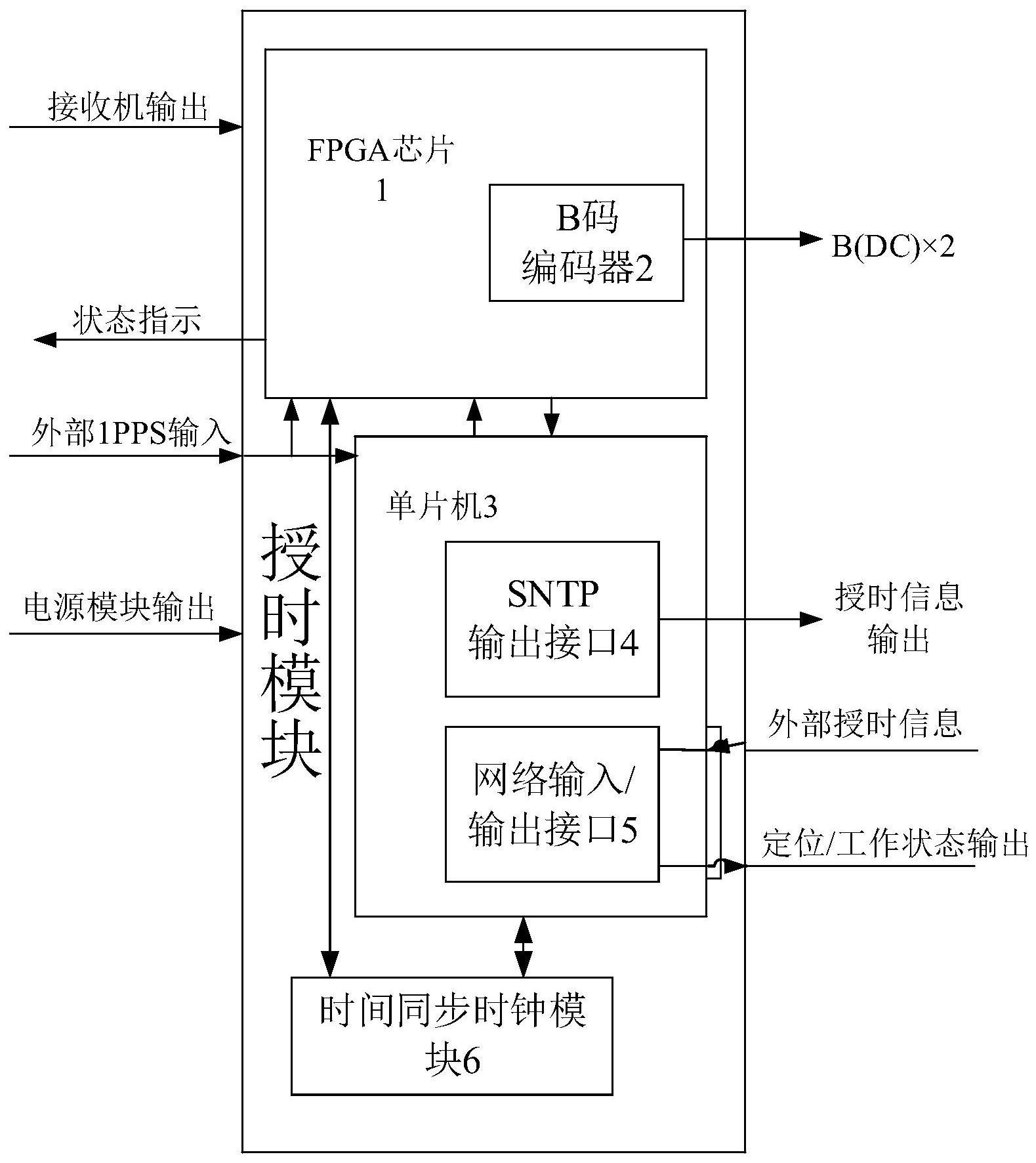

4、所述授时模块包括fpga芯片、b码编码器、单片机、时间同步时钟模块,所述fpga芯片内置b码编码器,所述fpga芯片与接收机连接,所述fpga芯片与单片机连接,所述时间同步时钟模块分别与fpga芯片、单片机连接,所述单片机通过sntp输出接口输出授时信息,所述单片机通过网络输入/输出接口输出定位/工作状态信号;

5、所述时间同步时钟模块包括时钟芯片、第一mos管、第二mos管、第一电容、第二电容、第四电阻、第五电阻、第一电感、晶振,所述第一mos管的s极与第二mos管的d极连接且都接时钟芯片的电源端,所述第一mos管的d极接第一电容的一端,所述第一电容与第四电阻并联,所述第一mos管的g极与fpga芯片连接,所述第二mos管的g极与单片机连接,所述第二mos管的s极接第五电阻的一端,所述第五电阻的另一端接地,所述时钟芯片的时钟输入端和时钟输出端与晶振的两端连接,所述时钟芯片的另一个电源端还与第二电容的一端、第一电感的一端连接。

6、优选的,所述单片机选用hwd32f429mlqfp144芯片。

7、优选的,所述fpga芯片选用hwd2v1000-4fg256芯片。

8、优选的,所述时钟芯片的输出端分别与单片机、fpga芯片连接。

9、优选的,所述电源模块与授时模块可插拔连接。

10、优选的,所述时间同步时钟模块与fpga芯片可插拔连接。

11、优选的,所述时间同步时钟模块与单片机可插拔连接。

12、优选的,还包括屏蔽型机箱,所述授时模块、电源模块放置于屏蔽型机箱内。

13、与现有技术相比,本发明的有益效果是:

14、1.本发明利用固定的时间同步时钟模块所产生的基准源与外部输入时间或者北斗卫星的授时时间进行对比,可以大大提高授时精度,避免自身时钟不稳定,授时不稳定的情况发生。

15、2、本发明采用负载保护、过电压保护、过温度保护大大提高的电源模块的使用寿命,还能避免造成元器件损坏,从而实现电路保护。

16、3.为了更好的提高授时精度,本发明还设计了时间同步时钟模块,单片机和fpga可以根据时间同步时钟模块输出的时钟信号,与外部授时信息或北斗发射机发出的北斗卫星的授时信息进行比对,然后进行授时校准,从而输出高精度的授时信息,大大提高授时准确度,其制造成本也低。

17、4、本发明的电路结构简单,成本低,安全可靠,可以大范围推广使用。

18、5、本发明的时间同步时钟模块采用mos管和滑动变阻器组合设计,通过单片机、fpga芯片、第五电阻(即滑动变阻器)联合控制时间同步时钟模块工作、不工作或休眠,能够大大降低功耗,节约能源。

19、6、本发明的电源模块与授时模块可插拔连接,这样的设计可以提高更换器件速度,从而降低维修成本。

20、7、本发明的时间同步时钟模块与fpga芯片可插拔连接,时间同步时钟模块与单片机可插拔连接,当时间同步时钟模块损坏时,可以快速更换新的时间同步时钟模块。

21、本发明附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

技术特征:

1.一种时间同步授时模块,其特征在于,包括授时模块、电源模块,所述电源模块与所述授时模块连接,用于给授时模块供电;

2.根据权利要求1所述的时间同步授时模块,其特征在于,所述单片机选用hwd32f429mlqfp144芯片。

3.根据权利要求1所述的时间同步授时模块,其特征在于,所述fpga芯片选用hwd2v1000-4fg256芯片。

4.根据权利要求1所述的时间同步授时模块,其特征在于,所述时钟芯片的输出端分别与单片机、fpga芯片连接。

5.根据权利要求1所述的时间同步授时模块,其特征在于,所述电源模块与授时模块可插拔连接。

6.根据权利要求1所述的时间同步授时模块,其特征在于,所述时间同步时钟模块与fpga芯片可插拔连接。

7.根据权利要求1所述的时间同步授时模块,其特征在于,所述时间同步时钟模块与单片机可插拔连接。

8.根据权利要求1所述的时间同步授时模块,其特征在于,还包括屏蔽型机箱,所述授时模块、电源模块放置于屏蔽型机箱内。

技术总结

本发明公开了一种时间同步授时模块,包括授时模块、电源模块,所述电源模块与所述授时模块连接,用于给授时模块供电;所述授时模块包括FPGA芯片、B码编码器、单片机、时间同步时钟模块,所述FPGA芯片内置B码编码器,所述FPGA芯片与接收机连接,所述FPGA芯片与单片机连接,所述时间同步时钟模块分别与FPGA芯片、单片机连接,所述单片机通过SNTP输出接口输出授时信息,所述单片机通过网络输入/输出接口输出定位/工作状态信号;本发明的时间同步授时模块功耗低、授时准确、成本低。

技术研发人员:韩彦龙,许英俊,李美烨,贾胜

受保护的技术使用者:天津七六四通信导航技术有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!