一种通信基带处理器

本发明涉及通信领域,具体来说涉及通信处理器领域,更具体地说,涉及一种通信基带处理器。

背景技术:

1、传统的通信处理器架构,包括数字信号处理(digital signal processing,简称dsp)核和多个协处理器,数字信号处理核是专用于数字信号处理的可编程芯片,协处理器是为协助中央处理器或dsp核完成其无法执行或执行效率、效果低下的处理工作而开发和应用的处理器,但仅dsp核和协处理器之间通过总线连接,协处理器之间没有直接连接的通道,例如:

2、ti tms320c6670 dsp架构,包含4颗c66x corepac和若干协处理器,协处理器与dsp核之间通过teranet总线连接,各个协处理器之间比较孤立,没有数据互连通道。

3、飞思卡尔的msc8157主要用于基站中,包含dsp核和协处理器,支持的标准有lte(含fdd(frequency division duplexing)、tdd(time division duplexing)),hspa+(high-speed packet access),lte-advanced、wimax(world interoperability formicrowave access),工作频率为:1ghz,其协处理器与dsp核之间通过通用总线连接,协处理器内部分为孤立的若干加速器,各加速器分别挂接在内部总线上。

4、ceva xc4500 dsp架构与上面的技术类似,采用“dsp核+多个协处理器”架构,dsp核与各协处理器之间采用总线连接,多个协处理器分立挂接在总线上。

5、从以上分析可以看出,传统的通信处理器架构有三个特点,一是都具备dsp核和协处理器;二是dsp核和协处理器之间采用公共总线进行互连;三是协处理器之间比较孤立,没有直接互连的数据通路。

6、随着通信技术发展,5g通信的数据传输速率达到gbps量级,理想情况下端到端时延1ms,典型端到端时延为5~10ms。同时,调度粒度也由时隙级演进到了符号级,这对通信处理器架构设计提出了挑战。5g通信具有高通量要求,若采用传统通信架构,dsp核与协处理器之间的总线带宽将达到200gbps以上,这对总线位宽和频率形成很大压力,也会带来布局布线拥堵问题;此外,频繁数据翻转会产生巨大功耗,数据传输延迟也会成为瓶颈;

7、5g通信引入新型帧结构、抢占、微时隙(mini-slot)、多调度请求(schedulingrequest,sr)并发等新技术,来应对通信低时延要求。调度粒度小到两个ofdm符号,使得dsp核与协处理器之间互动比较频繁,这对控制调度的实时响应又提出了要求。传统的通信处理器架构中,数据和控制共用一套总线,控制调度实时性存在风险,无法满足5g灵活、低时延要求。

技术实现思路

1、因此,本发明的目的在于克服上述现有技术的缺陷,提供一种通信基带处理器。

2、本发明的目的是通过以下技术方案实现的:

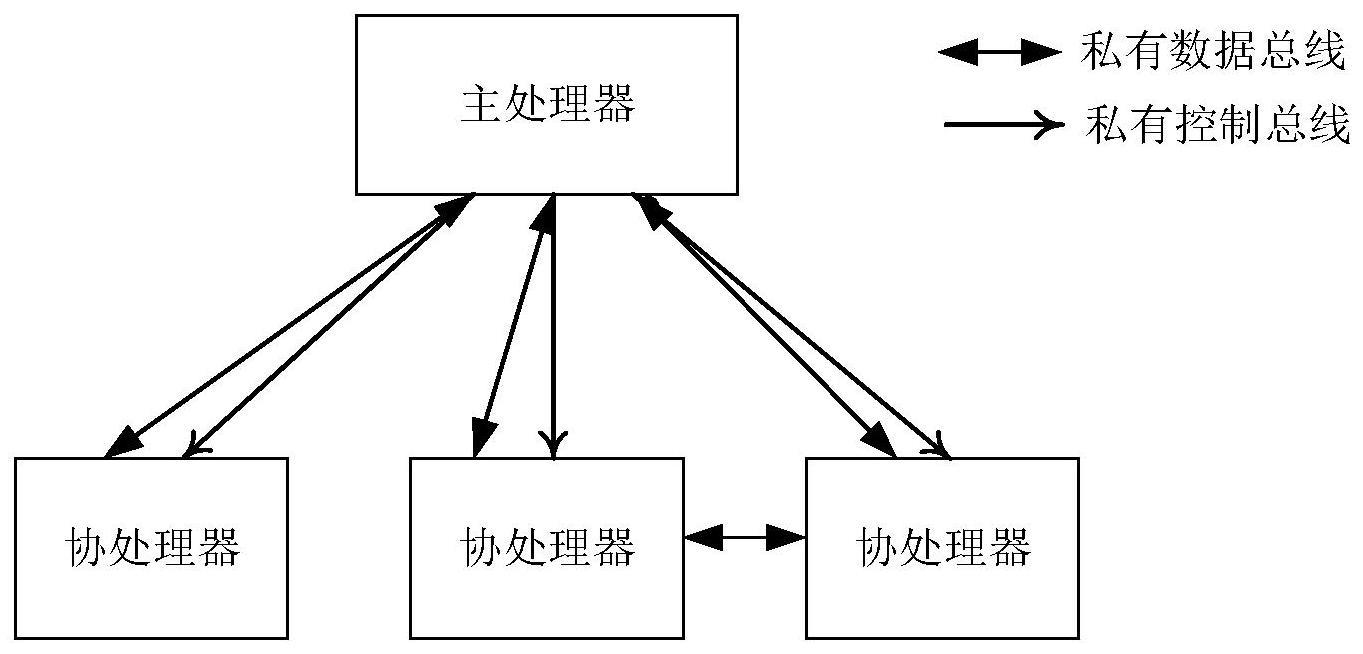

3、本发明提供一种通信基带处理器,用于5g通信场景、吞吐量和/或时延要求等于或高于5g通信的通信场景,通信基带处理器包括:主处理器和由主处理器通过私有控制总线分别连接和控制的多个协处理器,其中,主处理器,用于执行操作以实现指定的处理功能,所述处理功能包括数字信号处理;多个协处理器,用于协助主处理器完成至少部分数字信号处理,其中包括基带数字信号处理,需要数据交互的至少部分协处理器间采用私有数据总线互连。

4、可选的,主处理器为cpu、mcu或者dsp核,主处理器与多个协处理器间分别采用私有数据总线互连。

5、可选的,至少部分协处理器间设置有存储器,以在其中一方暂时不能接收另一方的数据时通过该存储器暂存数据。

6、可选的,主处理器被配置为可直接访问协处理器间设置的存储器以进行调试、写入基带数字信号处理所需的数据或者查询处理结果。

7、可选的,通信基带处理器还包括协处理器控制器以及为每个协处理器分别设置的控制信息存储器,主处理器被配置为经由双层控制架构对协处理器进行控制,其中,主处理器能通过直接配置协处理器的方式控制协处理器执行基带数字信号处理,或者主处理器能将控制配置信息预先写入控制信息存储器并由协处理器控制器读取控制信息存储器的内容完成对协处理器的寄存器配置以协助执行对应的基带数字信号处理。

8、可选的,为每个协处理器设置两个控制信息存储器,主处理器被配置为:在两个控制信息存储器中交替写入需要由该协处理器协助处理的不同处理任务对应的控制配置信息。

9、可选的,协处理器被配置为支持多种启动方式,其中包括:自主启动、软件启动和定时启动或者其组合。其中,自主启动是指协处理器控制器读取控制信息存储器的内容完成对协处理器的寄存器配置后协处理器在自主启动模式下收到需处理的数据流后协处理器自动开始数据处理的启动方式。软件启动是指主处理器直接配置协处理器的寄存器中的启动寄存器以启动协处理器开始工作的启动方式。定时启动是指主处理器或者协处理器控制器配置协处理器内部的时间戳寄存器并由预设的定时器开始计时以在时间到达时间戳寄存器中设置的数值时启动协处理器开始工作的启动方式。

10、可选的,主处理器执行的数字信号处理包括小点数fft运算、参数计算、矩阵规模小于预定规模的矩阵乘、码块大小小于预定大小的码块迭代译码和分支跳转计算或者其组合。

11、可选的,协处理器执行的数字信号处理包括大点数fft运算、矩阵规模大于等于预定规模的矩阵乘和码块大小大于等于预定大小的大码块迭代译码或者其组合。

12、可选的,协处理器间的私有数据总线基于valid&ready握手机制实现数据传输。

13、与现有技术相比,本发明的优点在于:

14、本发明的通信基带处理器将主处理器通过私有控制总线连接并分别控制多个协处理器,以让控制信息更快传递至相应的协处理器,并减少对数据传输的影响,减少数据传输的抖动,保障处理时延要求;其中,多个协处理器,用于协助主处理器完成数字信号处理中的至少部分基带数字信号处理,需要数据交互的至少部分协处理器间采用私有数据总线直接互连,由此,采用私有数据总线互连的协处理器可直接通过私有数据总线传输数据,减少对主处理器和协处理器之间的数据传输的影响,提升整体的数据吞吐量能力和处理效率,使其更好地达到5g通信场景的吞吐量、时延要求。

技术特征:

1.一种通信基带处理器,可用于5g通信场景,其特征在于,通信基带处理器包括:主处理器和由主处理器通过私有控制总线分别连接和控制的多个协处理器,其中,

2.根据权利要求1所述的通信基带处理器,其特征在于,主处理器为cpu、mcu或者dsp核,主处理器与多个协处理器间分别采用私有数据总线互连。

3.根据权利要求2所述的通信基带处理器,其特征在于,至少部分协处理器间设置有存储器,以在其中一方暂时不能接收另一方的数据时通过该存储器暂存数据。

4.根据权利要求3所述的通信基带处理器,其特征在于,主处理器被配置为能直接访问协处理器间设置的存储器以进行调试、写入基带数字信号处理所需的数据或者查询处理结果。

5.根据权利要求4所述的通信基带处理器,其特征在于,所述通信基带处理器还包括协处理器控制器以及为每个协处理器分别设置的控制信息存储器,主处理器被配置为经由双层控制架构对协处理器进行控制,其中,主处理器能通过直接配置协处理器的方式控制协处理器执行基带数字信号处理,或者主处理器能将控制配置信息预先写入控制信息存储器并由协处理器控制器读取控制信息存储器的内容完成对协处理器的寄存器配置以协助执行对应的基带数字信号处理。

6.根据权利要求5所述的通信基带处理器,其特征在于,为每个协处理器设置两个控制信息存储器,所述主处理器被配置为:在两个控制信息存储器中交替写入需要由该协处理器协助处理的不同处理任务对应的控制配置信息。

7.根据权利要求1-6任一项所述的通信基带处理器,其特征在于,所述协处理器被配置为支持多种启动方式,其中包括:自主启动、软件启动和定时启动或者其组合;

8.根据权利要求1-6任一项所述的通信基带处理器,其特征在于,所述主处理器执行的数字信号处理包括小点数fft运算、参数计算、矩阵规模小于预定规模的矩阵乘、码块大小小于预定大小的码块迭代译码和分支跳转计算或者其组合。

9.根据权利要求1-6任一项所述的通信基带处理器,其特征在于,所述协处理器执行的基带数字信号处理包括大点数fft运算、矩阵规模大于等于预定规模的矩阵乘和码块大小大于等于预定大小的大码块迭代译码或者其组合。

10.根据权利要求1-6任一项所述的通信基带处理器,其特征在于,协处理器间的私有数据总线基于valid&ready握手机制实现数据传输。

技术总结

本发明提供了通信基带处理器,可用于5G通信场景,其特征在于,通信基带处理器包括:主处理器和由主处理器通过私有控制总线分别连接和控制的多个协处理器,其中,主处理器,用于执行操作以实现指定的处理功能,所述处理功能包括数字信号处理;多个协处理器,用于协助主处理器完成至少部分数字信号处理,其中包括基带数字信号处理,需要数据交互的至少部分协处理器间采用私有数据总线互连。

技术研发人员:石晶林,赵旭莹,张小东,张丽雅,刘攀,吴立国,赵浩男,田昱

受保护的技术使用者:中国科学院计算技术研究所

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!