一种基于PYNQ的脉冲神经网络芯片数据通信方法及系统

本发明涉及神经网络芯片及芯片数据通信,尤其涉及一种基于pynq的脉冲神经网络芯片数据通信方法及系统。

背景技术:

1、脉冲神经网络(spiking neural network,snn)属于第三代人工神经网络,其模拟大脑工作模式,输入输出为稀疏离散脉冲,神经元对输入脉冲进行累积,当达到阈值时,进行脉冲发放。基于该机制,脉冲神经网络具有低功耗、低延时的优点。

2、为了更好的实现脉冲神经网络功能,通常会选择对应脉冲神经网络工作特点针对性构建专用的脉冲神经网络芯片,例如paicore芯片。在实际使用过程中,需要针对脉冲神经网络芯片与上位机之间的数据通信构建开发专用的数据通信系统,以实现上、下行数据的正常传输。

3、现有的脉冲神经网络芯片数据通信系统,例如paicore芯片的数据通信系统,通常使用通用pc或特定的模组系统(例如nvidia jetson nx)作为主控模块,将数据帧发送至bram后再从bram取出所需数据帧发送至脉冲神经网络芯片。现有的数据通信方式存在以下问题:

4、(1)使用通用pc的主控模块便携性较差,不能适用于移动场景下应用;采用特定的模组系统作为主控模块由于技术限制存在产品供应不稳定性;

5、(2)现有数据通信过程中必须占用大量的fpga bram资源,严重影响系统的可扩展性;

6、(3)数据传输过程中必须执行数据帧发送至bram和从bram取出数据帧两个分别独立的操作,降低了数据传输效率,增加了数据传输时间;

7、(4)在处理的数据帧数量较大时,需要控制数据帧分批次发送至fpga,增加了数据传输管理和维护的难度。

8、因此,现有的数据通信方法及系统不能完全适应脉冲神经网络芯片的工作要求,需要开发一种新的数据通信方法及系统。

技术实现思路

1、为解决现有技术的不足,本发明提出一种基于pynq的脉冲神经网络芯片数据通信方法及系统,使用zynq ps代替现有技术方案使用的通用pc或特定模组系统作为主控模块,能够提高系统的便携性和产品供应稳定性;使用fifo缓存器替代现有技术方案使用的bram,能够大幅节省脉冲神经网络芯片数据通信过程中的fpga bram资源占用,且能够实现数据帧在fifo缓存器中存入与取出同时进行,有效降低数据传输时间,实现较好的数据传输性能。

2、为实现以上目的,本发明所采用的技术方案包括:

3、一种基于pynq的脉冲神经网络芯片数据通信方法,其特征在于,包括:

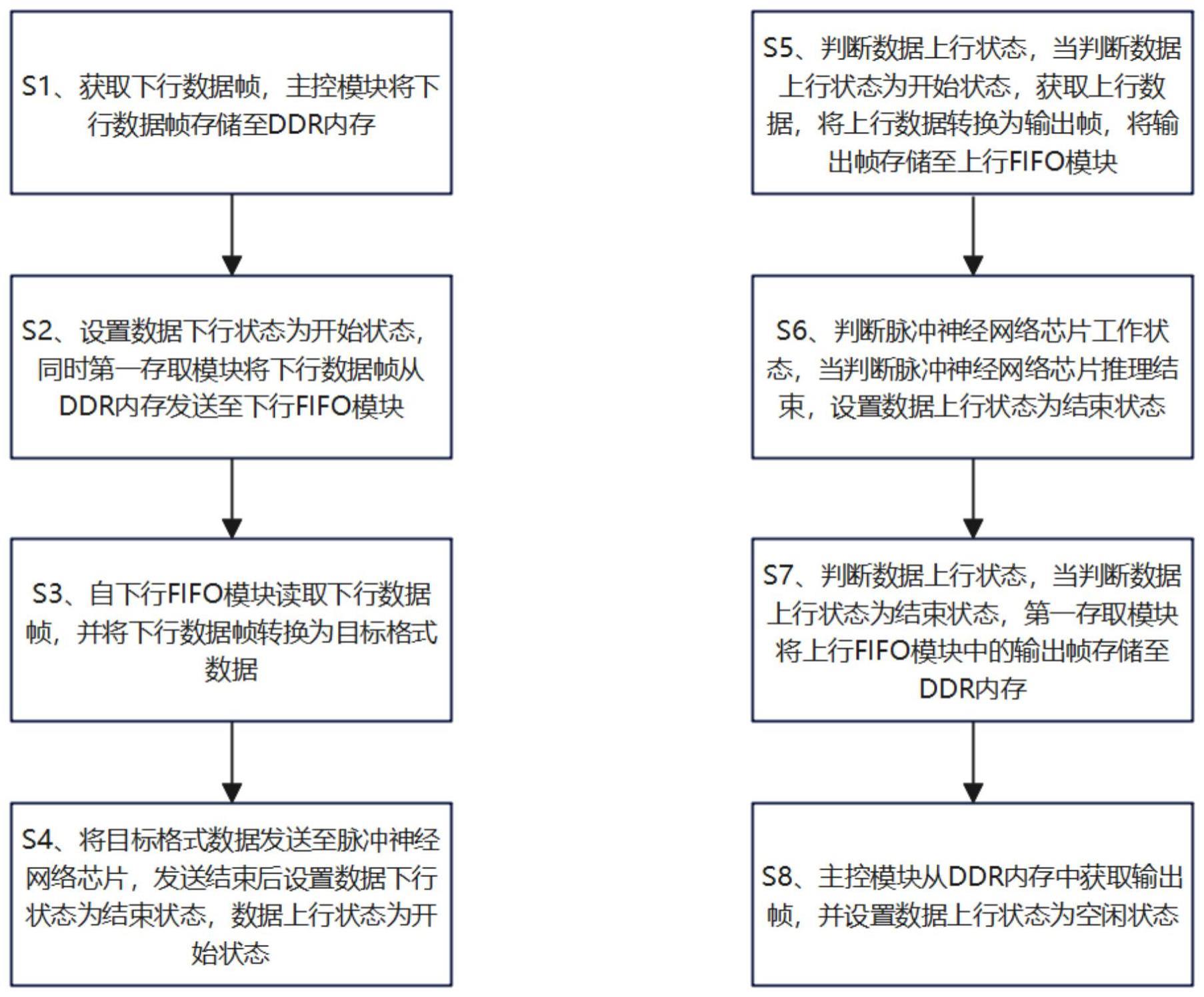

4、s1、获取下行数据帧,主控模块将下行数据帧存储至ddr内存;

5、s2、设置数据下行状态为开始状态,同时第一存取模块将下行数据帧从ddr内存发送至下行fifo模块;

6、s3、自下行fifo模块读取下行数据帧,并将下行数据帧转换为目标格式数据;

7、s4、将目标格式数据发送至脉冲神经网络芯片,发送结束后设置数据下行状态为结束状态,并设置数据上行状态为开始状态。

8、进一步地,所述方法还包括:

9、s5、判断数据上行状态,当判断数据上行状态为开始状态,获取上行数据,将上行数据转换为输出帧,将输出帧存储至上行fifo模块;

10、s6、判断脉冲神经网络芯片的工作状态是否为推理结束,当判断推理结束时,设置数据上行状态为结束状态;

11、s7、判断数据上行状态是否为结束状态,当判断数据上行状态为结束状态时,第一存取模块将上行fifo模块中的输出帧存储至ddr内存;

12、s8、主控模块从ddr内存中获取输出帧,并设置数据上行状态为空闲状态。

13、进一步地,所述主控模块包括zynq ps;

14、所述第一存取模块包括dma存取模块。

15、进一步地,所述将下行数据帧转换为目标格式数据包括:

16、将64bit的下行数据帧拆分为两个32bit数据获得目标格式数据。

17、进一步地,所述将上行数据转换为输出帧包括:

18、将脉冲神经网络芯片输出的两个32bit数据拼接为一个64bit的输出帧。

19、本发明还涉及一种基于pynq的脉冲神经网络芯片数据通信系统,其特征在于,包括:

20、主控模块,用于执行系统驱动程序,控制脉冲神经网络芯片数据通信系统中其他模块工作;

21、ddr模块,用于存储下行数据帧和输出帧;

22、第一存取模块,用于连接ddr模块和上行fifo模块、下行fifo模块之间的数据搬运;

23、下行fifo模块,用于缓存下行数据帧;

24、上行fifo模块,用于缓存输出帧;

25、异步握手模块,用于连接脉冲神经网络芯片,并将下行数据帧转换为目标格式数据,以及将上行数据转换为输出帧;

26、状态寄存模块,用于保存数据下行状态和数据上行状态;

27、状态判断模块,用于判断数据下行状态和数据上行状态,以及判断脉冲神经网络芯片工作状态。

28、进一步地,所述主控模块包括zynq ps。

29、进一步地,所述第一存取模块包括dma存取模块。

30、进一步地,所述异步握手模块与脉冲神经网络芯片之间的接口协议为单轨两相异步握手协议。

31、本发明还涉及一种计算机程序产品,包括计算机程序和/或指令,其特征在于,该计算机程序和/或指令被处理器执行时实现权利要求1至5中任一项所述方法的步骤。

32、本发明的有益效果为:

33、采用本发明所述基于pynq的脉冲神经网络芯片数据通信方法及系统,使用fifo缓存器替代现有技术方案使用的bram,能够大幅节省脉冲神经网络芯片数据通信过程中的fpga bram资源占用,且能够实现数据帧在fifo缓存器中存入与取出同时进行,有效降低数据传输时间,实现较好的数据传输性能。同时,本发明方法及系统采用zynq ps作为主要控制模块,既可以满足低功耗、便携性的需要,还可以充分利用开放的相关技术资源,避免因技术限制导致产品断供。

技术特征:

1.一种基于pynq的脉冲神经网络芯片数据通信方法,其特征在于,包括:

2.如权利要求1所述的方法,其特征在于,所述方法还包括:

3.如权利要求2所述的方法,其特征在于,所述主控模块包括zynq ps;

4.如权利要求2所述的方法,其特征在于,所述将下行数据帧转换为目标格式数据包括:

5.如权利要求2所述的方法,其特征在于,所述将上行数据转换为输出帧包括:

6.一种基于pynq的脉冲神经网络芯片数据通信系统,其特征在于,包括:

7.如权利要求6所述的系统,其特征在于,所述主控模块包括zynq ps。

8.如权利要求6所述的系统,其特征在于,所述第一存取模块包括dma存取模块。

9.如权利要求6所述的系统,其特征在于,所述异步握手模块与脉冲神经网络芯片之间的接口协议为单轨两相异步握手协议。

10.一种计算机程序产品,包括计算机程序和/或指令,其特征在于,该计算机程序和/或指令被处理器执行时实现权利要求1至5中任一项所述方法的步骤。

技术总结

本发明涉及一种基于PYNQ的脉冲神经网络芯片数据通信方法及系统,分别设置上、下行FIFO处理过程并结合运用DMA存取模块,使用ZYNQ PS替代现有技术方案使用的上位机,提高系统便携性和产品供应稳定性,使用FIFO缓存器替代现有技术方案使用的BRAM,能够大幅节省脉冲神经网络芯片数据通信过程中的FPGA BRAM资源占用,且能够实现数据帧在FIFO缓存器中存入与取出同时进行,有效降低数据传输时间,实现较好的数据传输性能。

技术研发人员:曹健,王炫,王源,钟毅,陈光

受保护的技术使用者:北京大学

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!