基于FPGA语言的阴影校正算法、装置及控制系统的制作方法

本公开涉及图像处理,尤其涉及一种基于fpga语言的阴影校正算法、装置及控制系统。

背景技术:

1、由于镜头与感光元器件的组合装配问题,会导致图像四周会出现暗角阴影;以及由于镜头对于光学折射不均匀导致的镜头周围出现阴影的情况。从而产生了阴影校正算法,镜头阴影校正是为了解决镜头的光学特性。

2、阴影校正算法,需要分块统计整张图上每个块的平均亮度,并计算中心亮度通过特定公式求出每个块的提升增益值,再根据双线性插值法进行每个点的亮度提升或压制。

3、该算法使用fpga语言实现需要消耗大量ram资源和逻辑资源,才可以实现。但是针对低成本小资源相机来说就无法实现该算法,这里急需一种可以节省资源的算法,从而可以实现该功能。

技术实现思路

1、为了解决上述问题,本申请提出一种基于fpga语言的阴影校正算法、装置及控制系统。

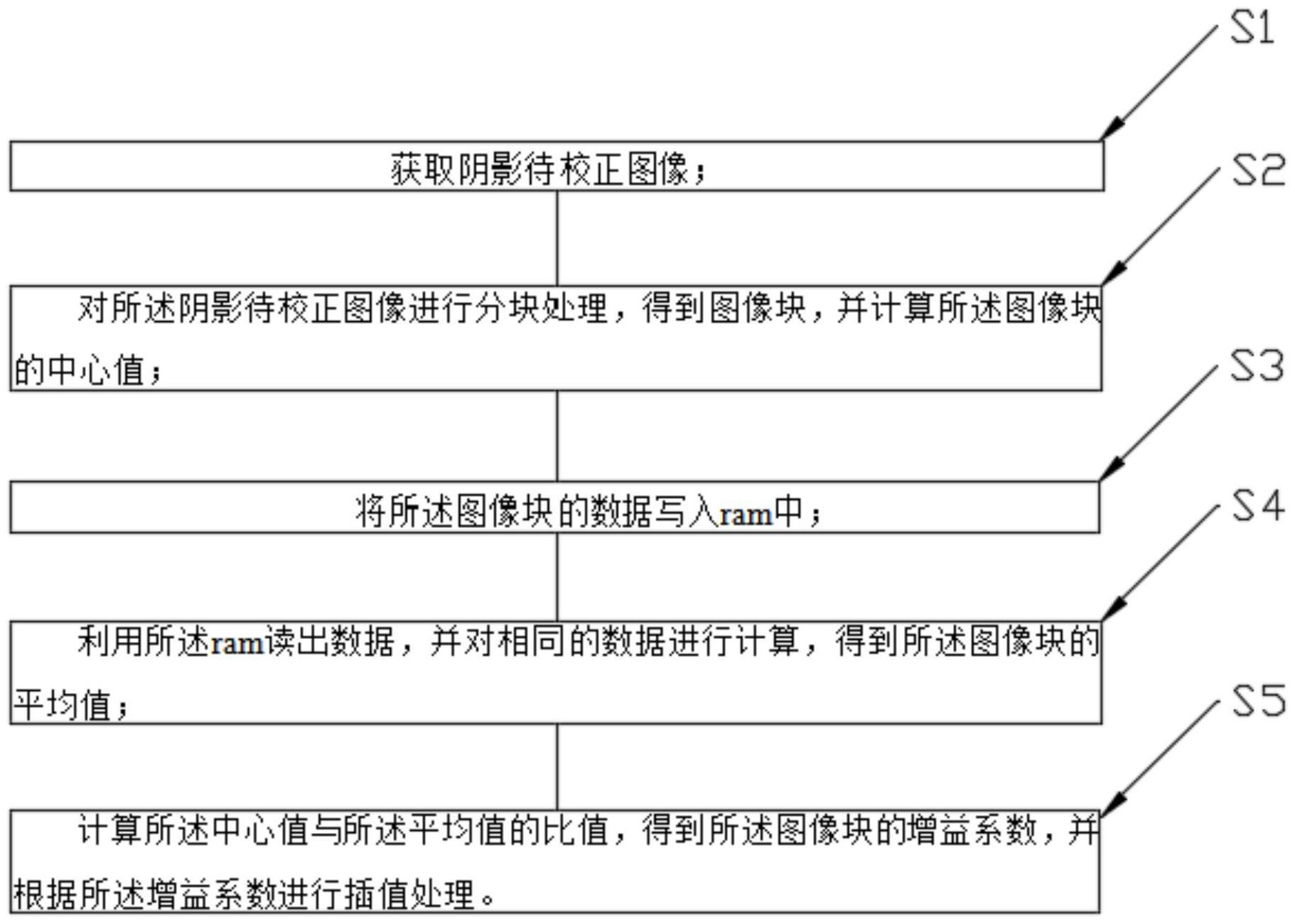

2、本申请一方面,提出基于fpga语言的阴影校正算法,包括如下步骤:

3、获取阴影待校正图像;

4、对所述阴影待校正图像进行分块处理,得到图像块,并计算所述图像块的中心值;

5、将所述图像块的数据写入ram中;

6、利用所述ram读出数据,并对相同的数据进行计算,得到所述图像块的平均值;

7、计算所述中心值与所述平均值的比值,得到所述图像块的增益系数,并根据所述增益系数进行插值处理。

8、作为本申请的一可选实施方案,可选地,对所述阴影待校正图像进行分块处理,得到图像块,并计算所述图像块的中心值,包括:

9、预设图像块划分条件;

10、按照所述图像块划分条件,将所述阴影待校正图像划分为横向和纵向皆为n的图像块n×n;

11、计算所述图像块中每个所述图像块的中心值并保存在ram中。

12、作为本申请的一可选实施方案,可选地,将所述图像块的数据写入ram中,包括:

13、在横向的数据写入上,控制每行间隔m个像素点写入一次,同时写入第一个数据和最后一个数据,共n+1个数据到ram中;

14、在纵向的数据写入上,控制每行间隔m个像素点写入一次,同时写入第一个数据和最后一个数据,共n+1个数据到ram中;

15、得到(n+1)×(n+1)个数据并写入到ram中。

16、作为本申请的一可选实施方案,可选地,利用所述ram读出数据,并对相同的数据进行计算,得到所述图像块的平均值,包括:

17、预设读写顺序;

18、按照读写顺序读写(n+1)个数据,两两之间进行累加,等得到n个数据,并写入所述ram中;

19、采用计算器,对n个数据中的相同数据进行累加:第一从0开始,第二个从n开始,得到n×n个累加数据;

20、利用所选定的累加数据除所选定图像块的数量,得到所述图像块的平均值。

21、作为本申请的一可选实施方案,可选地,计算所述中心值与所述平均值的比值,得到所述图像块的增益系数,并根据所述增益系数进行插值处理,包括:

22、利用所述中心值乘以所述图像块的像素值,再除所述平均值,得到n×n个所述图像块的增益系数;

23、将所述图像块的增益系数保存在ram中,并将获取的n×n个数值存储到flash中。

24、作为本申请的一可选实施方案,可选地,所述插值处理方法为双线性插值处理。

25、作为本申请的一可选实施方案,可选地,所述双线性插值处理,包括:

26、启动flash;

27、从所述flash中读出数据到两个ram中,用于读取四个所述图像块的数据;

28、将相同的数据分别写入两个ram中,对n个数据中的相同数据进行累加:第一从0开始,第二个从n开始,得到n×n个累加数据;

29、将四个所述图像块的累加数据除四,得到四个所述图像块的平均值。

30、作为本申请的一可选实施方案,可选地,所述双线性插值处理,还包括:

31、利用所述中心值乘以采用双线性插值处理所得到的四个所述图像块的像素值,再除所述平均值,得到n×n个所述图像块的增益系数;

32、将所述图像块的增益系数保存在ram中,并将获取的n×n个数值存储到flash中。

33、本申请另一方面,提供一种装置,用于实现所述的基于fpga语言的阴影校正算法,包括:

34、图像获取模块,用于获取阴影待校正图像;

35、图像分块模块,用于对所述阴影待校正图像进行分块处理,得到图像块,并计算所述图像块的中心值;

36、ran模块,用于将所述图像块的数据写入ram中;

37、均值计算模块,用于利用所述ram读出数据,并对相同的数据进行计算,得到所述图像块的平均值;

38、插值处理模块,用于计算所述中心值与所述平均值的比值,得到所述图像块的增益系数,并根据所述增益系数进行插值处理。

39、本申请另一方面,还提供一种控制系统,包括:

40、处理器;

41、用于存储处理器可执行指令的存储器;

42、其中,所述处理器被配置为执行所述可执行指令时实现所述的基于fpga语言的阴影校正算法。

43、本发明的技术效果:

44、本申请通过获取阴影待校正图像;对所述阴影待校正图像进行分块处理,得到图像块,并计算所述图像块的中心值;将所述图像块的数据写入ram中;利用所述ram读出数据,并对相同的数据进行计算,得到所述图像块的平均值;计算所述中心值与所述平均值的比值,得到所述图像块的增益系数,并根据所述增益系数进行插值处理。能够减少ram资源的消耗,所有统计计算均使用同一个ram进行,并可以支持自动计算块内平均值,减少逻辑资源消耗的方法。

45、求取平均值可以利用阴影特点中间高四周低的特性,对分块区域仅取四角数据进行平均数值统计,减少统计计算,降低ram资源位宽。同时利用等分方式使用2个小ram块进行快速读取每个点所需上下左右的四块增益求取值、双线性插值的结果。该方法特点是可以使用很小的资源实现多个块的数据统计和读取,便于算法优化和逻辑资源的节省。

46、根据下面参考附图对示例性实施例的详细说明,本公开的其它特征及方面将变得清楚。

技术特征:

1.基于fpga语言的阴影校正算法,其特征在于,包括如下步骤:

2.根据权利要求1所述的基于fpga语言的阴影校正算法,其特征在于,对所述阴影待校正图像进行分块处理,得到图像块,并计算所述图像块的中心值,包括:

3.根据权利要求2所述的基于fpga语言的阴影校正算法,其特征在于,将所述图像块的数据写入ram中,包括:

4.根据权利要求1所述的基于fpga语言的阴影校正算法,其特征在于,利用所述ram读出数据,并对相同的数据进行计算,得到所述图像块的平均值,包括:

5.根据权利要求4所述的基于fpga语言的阴影校正算法,其特征在于,计算所述中心值与所述平均值的比值,得到所述图像块的增益系数,并根据所述增益系数进行插值处理,包括:

6.根据权利要求1所述的基于fpga语言的阴影校正算法,其特征在于,所述插值处理方法为双线性插值处理。

7.根据权利要求6所述的基于fpga语言的阴影校正算法,其特征在于,所述双线性插值处理,包括:

8.根据权利要求7所述的基于fpga语言的阴影校正算法,其特征在于,所述双线性插值处理,还包括:

9.装置,用于实现权利要求1-8中任一项所述的基于fpga语言的阴影校正算法,其特征在于,包括:

10.控制系统,其特征在于,包括:

技术总结

本申请涉及基于一种FPGA语言的阴影校正算法、装置及控制系统,通过获取阴影待校正图像;对所述阴影待校正图像进行分块处理,得到图像块,并计算所述图像块的中心值;将所述图像块的数据写入ram中;利用所述ram读出数据,并对相同的数据进行计算,得到所述图像块的平均值;计算所述中心值与所述平均值的比值,得到所述图像块的增益系数,并根据所述增益系数进行插值处理。能够减少ram资源的消耗,所有统计计算均使用同一个ram进行,并可以支持自动计算块内平均值,减少逻辑资源消耗的方法。求取平均值可以利用阴影特点中间高四周低的特性,对分块区域仅取四角数据进行平均数值统计,减少统计计算,降低ram资源位宽。

技术研发人员:李希,栾国晨

受保护的技术使用者:北京睿智奥恒视觉科技有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!