一种基于多路电流分段延时与合并输出架构的驱动电路

本发明属于模拟与射频放大器,更具体地,涉及一种基于多路电流分段延时与合并输出架构的驱动电路。

背景技术:

1、随着5g通信、虚拟现实、边缘计算等高流量业务的迅速发展,光纤通信作为目前有线通信骨干网的主要力量,行业标准从200gbe、400gbe、800gbe到1.6tbe不断发展,核心网络的传输速率与数据吞吐能力不断更新迭代。驱动电路作为光纤通信链路中发射端的最后一级电路,与光调制器直接相连需要工作在全速率模式下,其工作速度直接决定了发射机的通信速度上限;同时由于驱动电路需要提供足够的信号输出功率,其自身的能效性能也是影响发射机整体功耗性能的关键因素。因此超宽带高能效驱动电路具有重要的研究意义。

2、目前宽带驱动电路的主要架构包括集总式开漏级输出架构以及分布式架构。如图1所示,集总式开漏级输出架构主要由单个提供电压电流转换的跨导晶体管构成,由于输出节点只有一条支路,由晶体管产生的信号电流只能向输出节点流动,因此这种架构的驱动的能效理论可以达到100%。但受到大尺寸晶体管带来的寄生电容cgs,cgd,cds的影响,主极点频率较低,带宽很难达到100ghz以上;分布式驱动架构如图2所示,主要包括输入网络、输入匹配负载、跨导单元、输出网络、输出匹配负载。分布式架构由于不受输入输出极点频率的影响已有达到170ghz工作带宽的研究,具有高带宽的优势。由于分布式架构的输出节点与开漏极相比额外增加了输出匹配负载,因此晶体管产生的信号电流一部分会流向该输出匹配负载,剩下的电流从输出端口流出,在完全匹配的情况下,一半的电流会流向该负载,从而分布式驱动的能效约50%。综上所述,目前已有的驱动电路的两种架构存在着高效率与高带宽相矛盾的问题。

技术实现思路

1、针对现有技术的缺陷,本发明的目的在于提供一种基于多路电流分段延时与合并输出架构的驱动电路,可有效折衷驱动电路的整体带宽与能效两方面性能。

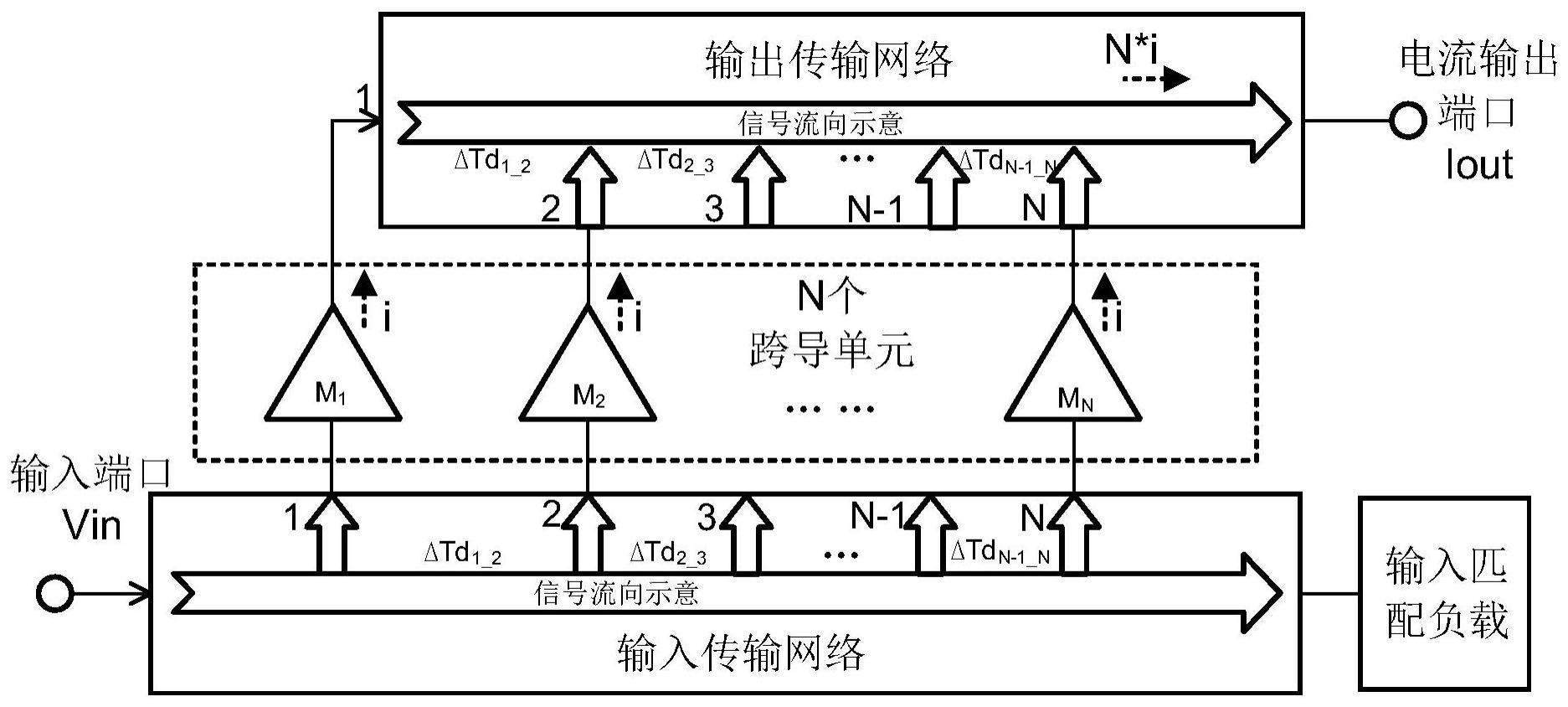

2、为实现上述目的,本发明提供了一种基于多路电流分段延时与合并输出架构的驱动电路,用于光纤通信链路中发射端,包括输入传输网络、放大单元、输出传输网络和输入匹配负载,所述放大单元包括n个跨导单元m1~m n;

3、所述输入传输网络,包括n+1个依次串联的电感lg1~lgn+1,电感lg1~lgn+1中相邻两电感的连接点依次构成输入传输网络的1~n个端口,所述输入传输网络用于接收并将发射端中光调制器输出的信号按照预设延时时间,对应通过该1~n个端口对应分配到跨导单元m1~m n进行放大及电压电流转换处理;

4、所述输入匹配负载,用于吸收向光调制器反射的信号;

5、所述输出传输网络,包括n个依次串联的电感ld1~ldn,电感ld1~ldn的第一端依次构成输出传输网络的1~n个端口,所述输出传输网络用于按照预设延迟时间分别叠加来自各跨导单元输出的放大电流信号并合并输出;其中,所述输入传输网络中的第i个端口和第i+1个端口之间的延时时间δtgi_i+1与输出传输网络中的第i个端口和第i+1个端口之间的延迟时间δtdi_i+1相等,或两者相差第i个跨导单元所处理的信号周期的整数倍,i∈(1,2,…,n-1)。

6、本发明提供的基于多路电流分段延时与合并输出架构的驱动电路,使用多路跨导单元合并形成大的放大单元,由于每个跨导单元都是小尺寸电路,引入的寄生电容更小,与输入传输网络中的感性元件形成串联谐振,可极大的扩展电路带宽;且本发明提供的驱动电路的输出端口采用开漏设计,可有效提高放大器的驱动能效,达到有效折衷驱动电路的整体带宽与能效两方面性能的目的。

7、在其中一个实施例中,当所述光调制器输出的信号为频谱信号时,所述输入传输网络中的第i个端口和第i+1个端口之间的延时时间与输出传输网络中的第i个端口和第i+1个端口之间的延迟时间相等;当所述光调制器输出的信号输出的信号为单频率或周期信号时,所述输入传输网络中的第i个端口和第i+1个端口之间的延时时间与输出传输网络中的第i个端口和第i+1个端口之间的延迟时间两者相差第i个跨导单元所处理的信号周期的整数倍。

8、在其中一个实施例中,所述输入传输网络中的各电感感值lg相等,所述输出传输网络中的各电感感值ld相等;所述延时时间δtgi_i+1与延迟时间δtdi_i+1的差值,根据跨导单元mi的输入寄生电容和输出寄生电容,通过调整感值lg和感值ld实现。

9、在其中一个实施例中,电感lg1的第一端与所述发射端中的光调制器的输出端相连,电感lgn+1的第二端通过输入匹配负载接地,电感lg1~lgn+1中相邻两电感的连接点对应与跨导单元m1~m n的输入端相连;电感ld1~ldn的第一端对应与跨导单元m1~mn的输出端相连,电感ldn的第二端与外部负载相连。

10、在其中一个实施例中,所述输入匹配负载包括电阻r1,所述输入匹配负载的阻抗与所述输入传输网络的特征阻抗相等。

11、在其中一个实施例中,所述跨导单元采用若干级堆叠放大电路,每级堆叠放大电路均包括双极性晶体管或场效应晶体管。

12、在其中一个实施例中,所述跨导单元采用吉尔伯特单元。

技术特征:

1.一种基于多路电流分段延时与合并输出架构的驱动电路,用于光纤通信链路中发射端,其特征在于,包括输入传输网络、放大单元、输出传输网络和输入匹配负载,所述放大单元包括n个跨导单元m1~m n;

2.根据权利要求1所述的基于多路电流分段延时与合并输出架构的驱动电路,其特征在于,当所述光调制器输出的信号为频谱信号时,所述输入传输网络中的第i个端口和第i+1个端口之间的延时时间与输出传输网络中的第i个端口和第i+1个端口之间的延迟时间相等;当所述光调制器输出的信号输出的信号为单频率或周期信号时,所述输入传输网络中的第i个端口和第i+1个端口之间的延时时间与输出传输网络中的第i个端口和第i+1个端口之间的延迟时间两者相差第i个跨导单元所处理的信号周期的整数倍。

3.根据权利要求1或2所述的基于多路电流分段延时与合并输出架构的驱动电路,其特征在于,所述输入传输网络中的各电感感值lg相等,所述输出传输网络中的各电感感值ld相等;所述延时时间δtgi_i+1与延迟时间δtdi_i+1的差值,根据跨导单元mi的输入寄生电容和输出寄生电容,通过调整感值lg和感值ld实现。

4.根据权利要求1所述的基于多路电流分段延时与合并输出架构的驱动电路,其特征在于,电感lg1的第一端与所述发射端中的光调制器的输出端相连,电感lgn+1的第二端通过输入匹配负载接地,电感lg1~lgn+1中相邻两电感的连接点对应与跨导单元m1~m n的输入端相连;电感ld1~ldn的第一端对应与跨导单元m1~mn的输出端相连,电感ldn的第二端与外部负载相连。

5.根据权利要求1所述的基于多路电流分段延时与合并输出架构的驱动电路,其特征在于,所述输入匹配负载包括电阻r1,所述输入匹配负载的阻抗与所述输入传输网络的特征阻抗相等。

6.根据权利要求1所述的基于多路电流分段延时与合并输出架构的驱动电路,其特征在于,所述跨导单元采用若干级堆叠放大电路,每级堆叠放大电路均包括双极性晶体管或场效应晶体管。

7.根据权利要求1所述的基于多路电流分段延时与合并输出架构的驱动电路,其特征在于,所述跨导单元采用吉尔伯特单元。

技术总结

本发明公开了一种基于多路电流分段延时与合并输出架构的驱动电路,用于光纤通信链路中发射端,包括输入传输网络、包含N个跨导单元的放大单元、输出传输网络和输入匹配负载,其中,输入传输网络用于接收并将发射端中光调制器输出的信号按照预设延时时间对应分配到各跨导单元;输入匹配负载,用于吸收向光调制器反射的信号;输出传输网络用于按照预设延迟时间分别叠加来自各跨导单元输出的放大电流信号并合并输出,其中,输入传输网络中的第i个端口和第i+1个端口之间的延时时间与输出传输网络中的第i个端口和第i+1个端口之间的延迟时间相等或两者相差信号周期的整数倍。本发明可有效折衷驱动电路的整体带宽与能效两方面性能。

技术研发人员:毕晓君,盛超帝

受保护的技术使用者:华中科技大学

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!