一种阵列接收机多路DDC同步采集输出系统及实现方法与流程

本发明涉及数据同步采集输出,尤其涉及一种阵列接收机多路ddc同步采集输出系统及实现方法。

背景技术:

1、接收机是无线电电磁频谱监测领域最常用的接收设备,它通过放大、滤波、变频、采样、信号处理等电路处理,可以将天线收到的电信号以频谱的形式表示,通过频谱监视天空中无线电信号的活动情况。

2、数字ddc是数字下变频器的英文缩写,数字接收机中频信号经过模数变换器件产生数字信号,经过ddc处理可以得到基带数字信号,可用于数字解调和各种信号参数测量,ddc处理包括正交数字混频、数字滤波、采样速率变换等过程。

3、阵列接收机是指用于本振或时钟同源,接收同一个频率信号的多个接收机组成的接收无线的信号的电子设备,具有多个接收机同步采集、幅度相位一致性的特点,可用于无线电测向和波束合成,其同步控制采用同步控制接口,一般包括同步触发脉冲和同步指令,一般由硬件硬件接口通过设备间互联的同步控制线实现。

4、为了满足目前无线电监测更多信号的需求,要求阵列接收机同时接收多个无线电信号,通常采用多路数字ddc的方法实现,随着ddc的路数增加,同步控制接口控制设计更加复杂和困难,涉及每一路ddc的采集和数据打包同步,由于每路ddc带宽不同采样率差异大,而硬件fpga提供的数据缓存空间有限,这就要求精心设计控制指令收发字长和指令传输速度,以及控制打包流程,才能保证数据不溢出、不掉包完整稳定输出。

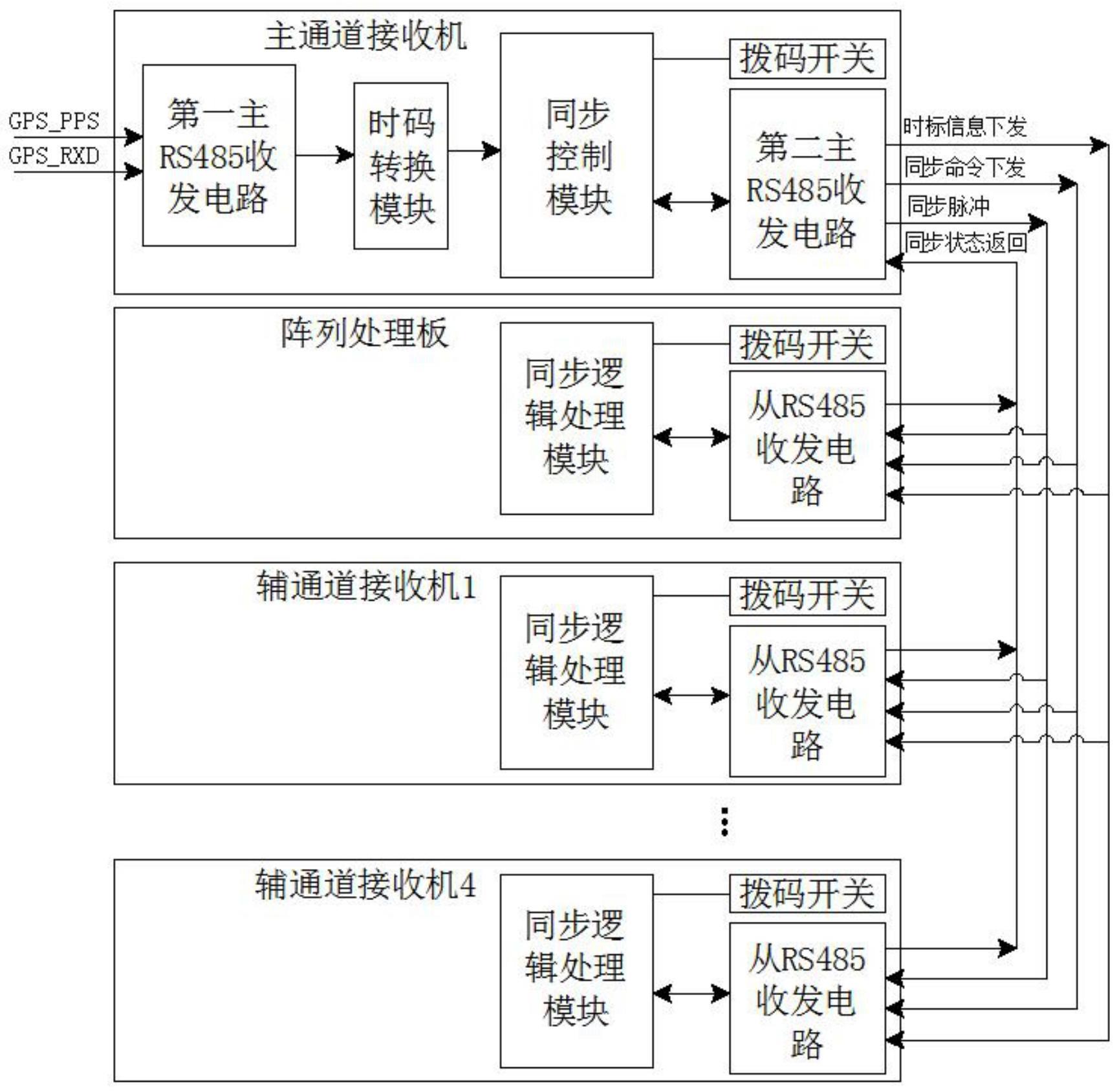

5、目前,阵列接收机由总控设备和多通道接收机组成,总控设备用于同步控制指令收发,多通道接收机用于多路天线信号的接收,通过级联方式的同步控制接口连接总控设备和多通道接收机,总控设备提供给多通道接收机时钟,所以多通道接收机保证时钟同源,同步控制接口包括同步触发脉冲、控制指令、状态返回等信号,这些信号通常采用差分对信号传输,控制指令采用同步串行指令形式传输,确保指令传输的可靠性,总控设备对阵列接收机同步控制过程如图1所示;

6、而这种同步控制方式控制接口通信协议简单,只能控制一路ddc同步输出,无法实现多路ddc同步输出,且控制流程简单,没有握手应答机制,无法实现精准控制,还缺乏数据缓存状态监测,缓存利用率低,容易溢出,同时缺乏传输优先级处理机制,容易造成数据丢失,因此,本发明提出一种阵列接收机多路ddc同步采集输出系统及实现方法用以解决现有技术中存在的问题。

技术实现思路

1、针对上述问题,本发明的目的在于提出一种阵列接收机多路ddc同步采集输出系统及实现方法,解决现有的阵列接收机同步控制方式存在控制接口通信协议简单,导致无法实现多路ddc同步输出,以及无法实现精准控制,缺乏数据缓存状态监测,导致缓存利用率低,容易溢出并造成数据丢失的问题。

2、为了实现本发明的目的,本发明通过以下技术方案实现:一种阵列接收机多路ddc同步采集输出系统,包括主通道接收机、阵列处理板和辅通道接收机,所述主通道接收机和辅通道接收机上均设有由射频和数字处理模块组成的接收通道,所述主通道接收机通过第一同步控制接口与阵列处理板以及辅通道接收机上的第二同步控制接口连接,所述主通道接收机上设有第一主rs485收发电路、第二主rs485收发电路、时码转换模块、同步控制模块和主拨码开关,所述第一同步控制接口由主通道接收机上的第二主rs485收发电路、同步控制模块和主拨码开关组成,所述阵列处理板和辅通道接收机上的第二同步控制接口连接由从rs485收发电路、从拨码开关和同步逻辑处理模块组成,所述主通道接收机和辅通道接收机通过各自的高速aurora光口将数据打包传输到阵列处理板,传输的数据包括1路宽带相位数据、4路窄带iq数据和48路话音ddc的iq数据。

3、进一步改进在于:所述第一同步控制接口上设有4对rs485差分线,且分别用于主通道接收机输出时标信息、同步控制命令和同步脉冲并输入各个辅通道按分配的时隙返回的状态信息。

4、进一步改进在于:所述1路宽带相位数据在最大带宽200mhz时的采样速率为256mp/s,每个样点的位宽为16bit,则最大流量为256x2=512mb/s=4096mb/s。

5、进一步改进在于:所述4路窄带iq数据包括9种带宽,其中最大带宽为5mhz时的iq数据采样速率为6.4mp/s,每个样点的位宽为i、q分别为16bit,则数据最大流量为6.4x4=25.6mb/s=204.8mb/s。

6、进一步改进在于:所述48路话音ddc的iq数据包括14种带宽,其中最大带宽为25khz时的iq数据采样速率为32kp/s,每个样点的位宽为i、q分别为32bit,则数据最大流量为32x8=256kb/s=2048kb/s。

7、进一步改进在于:所述第一同步控制接口利用sync_txd_code差分对传输主机通过秒脉冲、时码信号和毫秒计数器产生的时码信号,利用sync_txd差分对传输主机同步控制接口输出的命令信息,利用sync_pulse差分对传输主同步控制接口输出的命令信息后的同步脉冲信号,利用sync_rxd差分对传输各辅机上报给主机的状态信息。

8、一种阵列接收机多路ddc同步采集输出的实现方法,包括以下步骤:

9、步骤一:主通道接收机中的同步控制模块接收同步控制信号后产生各子模块的同步控制信号,并将数据打包传输,利用同步控制信号分别对各自模块进行同步控制;

10、步骤二:各自模块得到同步控制时各通道收到同步指令,各同步模块根据同步指令做同步处理,通过同步触发保证各通道的数据同时采集和传输。

11、进一步改进在于:所述步骤一中,对各自模块进行同步控制包括ad数据接收模块复位、寄存器复位、射频增益控制调整、ddr3缓存复位、宽带ddc复位、信道化ddc复位、宽带频谱计算同步复位、48路语音ddc分别同步复位、4路数字ddc分别同步复位以及组包控制模块同步复位。

12、本发明的有益效果为:本发明采用同步接口设计,利用带有同步脉冲的异步串行通信协议,实现多路ddc数据同步控制及状态返回,用很少的控制线实现,连线简单成本低,且采用阵列接收机地址编码和同步脉冲时隙的设计,很好地解决多个接收通道和多个ddc数据的状态返回和指令控制,具有握手应答的控制机制,实现精准控制,另外采用优先级仲裁机制,解决阵列接收机的多路ddc多种采样率数据传输流量控制,避免缓存溢出数据丢失问题,具有数据缓存状态监测功能,提高了缓存利用率。

技术特征:

1.一种阵列接收机多路ddc同步采集输出系统,其特征在于:包括主通道接收机、阵列处理板和辅通道接收机,所述主通道接收机和辅通道接收机上均设有由射频和数字处理模块组成的接收通道,所述主通道接收机通过第一同步控制接口与阵列处理板以及辅通道接收机上的第二同步控制接口连接,所述主通道接收机上设有第一主rs485收发电路、第二主rs485收发电路、时码转换模块、同步控制模块和主拨码开关,所述第一同步控制接口由主通道接收机上的第二主rs485收发电路、同步控制模块和主拨码开关组成,所述阵列处理板和辅通道接收机上的第二同步控制接口连接由从rs485收发电路、从拨码开关和同步逻辑处理模块组成,所述主通道接收机和辅通道接收机通过各自的高速aurora光口将数据打包传输到阵列处理板,传输的数据包括1路宽带相位数据、4路窄带iq数据和48路话音ddc的iq数据。

2.根据权利要求1所述的一种阵列接收机多路ddc同步采集输出系统,其特征在于:所述第一同步控制接口上设有4对rs485差分线,且分别用于主通道接收机输出时标信息、同步控制命令和同步脉冲并输入各个辅通道按分配的时隙返回的状态信息。

3.根据权利要求1所述的一种阵列接收机多路ddc同步采集输出系统,其特征在于:所述1路宽带相位数据在最大带宽200mhz时的采样速率为256mp/s,每个样点的位宽为16bit,则最大流量为256x2=512mb/s=4096mb/s。

4.根据权利要求1所述的一种阵列接收机多路ddc同步采集输出系统,其特征在于:所述4路窄带iq数据包括9种带宽,其中最大带宽为5mhz时的iq数据采样速率为6.4mp/s,每个样点的位宽为i、q分别为16bit,则数据最大流量为6.4x4=25.6mb/s=204.8mb/s。

5.根据权利要求1所述的一种阵列接收机多路ddc同步采集输出系统,其特征在于:所述48路话音ddc的iq数据包括14种带宽,其中最大带宽为25khz时的iq数据采样速率为32kp/s,每个样点的位宽为i、q分别为32bit,则数据最大流量为32x8=256kb/s=2048kb/s。

6.根据权利要求1所述的一种阵列接收机多路ddc同步采集输出系统,其特征在于:所述第一同步控制接口利用sync_txd_code差分对传输主机通过秒脉冲、时码信号和毫秒计数器产生的时码信号,利用sync_txd差分对传输主机同步控制接口输出的命令信息,利用sync_pulse差分对传输主同步控制接口输出的命令信息后的同步脉冲信号,利用sync_rxd差分对传输各辅机上报给主机的状态信息。

7.一种阵列接收机多路ddc同步采集输出的实现方法,其特征在于,包括以下步骤:

8.根据权利要求7所述的一种阵列接收机多路ddc同步采集输出的实现方法,其特征在于:所述步骤一中,对各自模块进行同步控制包括ad数据接收模块复位、寄存器复位、射频增益控制调整、ddr3缓存复位、宽带ddc复位、信道化ddc复位、宽带频谱计算同步复位、48路语音ddc分别同步复位、4路数字ddc分别同步复位以及组包控制模块同步复位。

技术总结

本发明公开一种阵列接收机多路DDC同步采集输出系统及实现方法,其系统包括主通道接收机、阵列处理板和辅通道接收机,主通道接收机和辅通道接收机上均设有由射频和数字处理模块组成的接收通道;本发明采用同步接口设计,利用带有同步脉冲的异步串行通信协议,实现多路DDC数据同步控制及状态返回,用很少的控制线实现,连线简单成本低,且采用阵列接收机地址编码和同步脉冲时隙的设计,很好地解决多个接收通道和多个DDC数据的状态返回和指令控制,另外采用优先级仲裁机制,解决阵列接收机的多路DDC多种采样率数据传输流量控制,避免缓存溢出数据丢失问题,具有数据缓存状态监测功能,提高了缓存利用率。

技术研发人员:郭方,陈晓辉

受保护的技术使用者:成都中安频谱科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!