一种基于源同步信号的时钟相位偏移自动补偿方法与流程

本发明涉及高速数据通信,更具体地说,特别涉及一种基于源同步信号的时钟相位偏移自动补偿方法。

背景技术:

1、为了能够准确稳定地采集输入到fpga的高速数据信号,采样时钟和数据信号的相对延迟时间,即相位,必须满足严格的建立保持时间等时序关系。在进行fpga程序设计时,通过对输入时序进行严格约束,并通过插入io delay或者其他延时单元进行调整,可以使得时钟与数据的相位关系保持在稳定采集状态。

2、然而随着板子(基于fpga的数据接收板)工作温度的变化,驱动数据的时钟相位将不可避免地发生相对偏移,当输入为低速的数据信号、且时序余量足够时,因工作温度变化引起的相移不会显著影响数据采集的正确性。但是当输入为高速数据信号,尤其当信号为高速并行信号时,因为时钟周期极大的缩短,各路数据信号延时不尽相同,因温度引起的时钟相位偏移相对时钟周期的占比不容忽视,时钟相移导致数据采集进入亚稳态的概率将直线上升。若不对温度变化引起的时钟相移进行补偿,将导致板子在高温或者低温时采集出错,进而影响板子数据采集性能。

3、同步信号与数据信号一样,是由源端时钟驱动发出,因此在时钟相移影响方面同步信号具有与数据信号相同的属性。在实际运行过程中,数据信号时刻处在变化之中,而同步信号保持不变,这个属性使得同步信号便于测量。通过对同步信号与时钟相位关系的测量,可以求出时钟相对同步信号的相位偏移,通过对时钟的相位进行动态地反向补偿,可以保持时钟相对数据和同步信号的相位不变,从而保证数据采集的稳定性,提升板子的温度适应范围,实现全温度范围准确稳定采集数据信号的目标。为此,确有必要提供一种基于源同步信号的时钟相位偏移自动补偿方法。

技术实现思路

1、本发明的目的在于提供一种基于源同步信号的时钟相位偏移自动补偿方法,以克服现有技术所存在的缺陷。

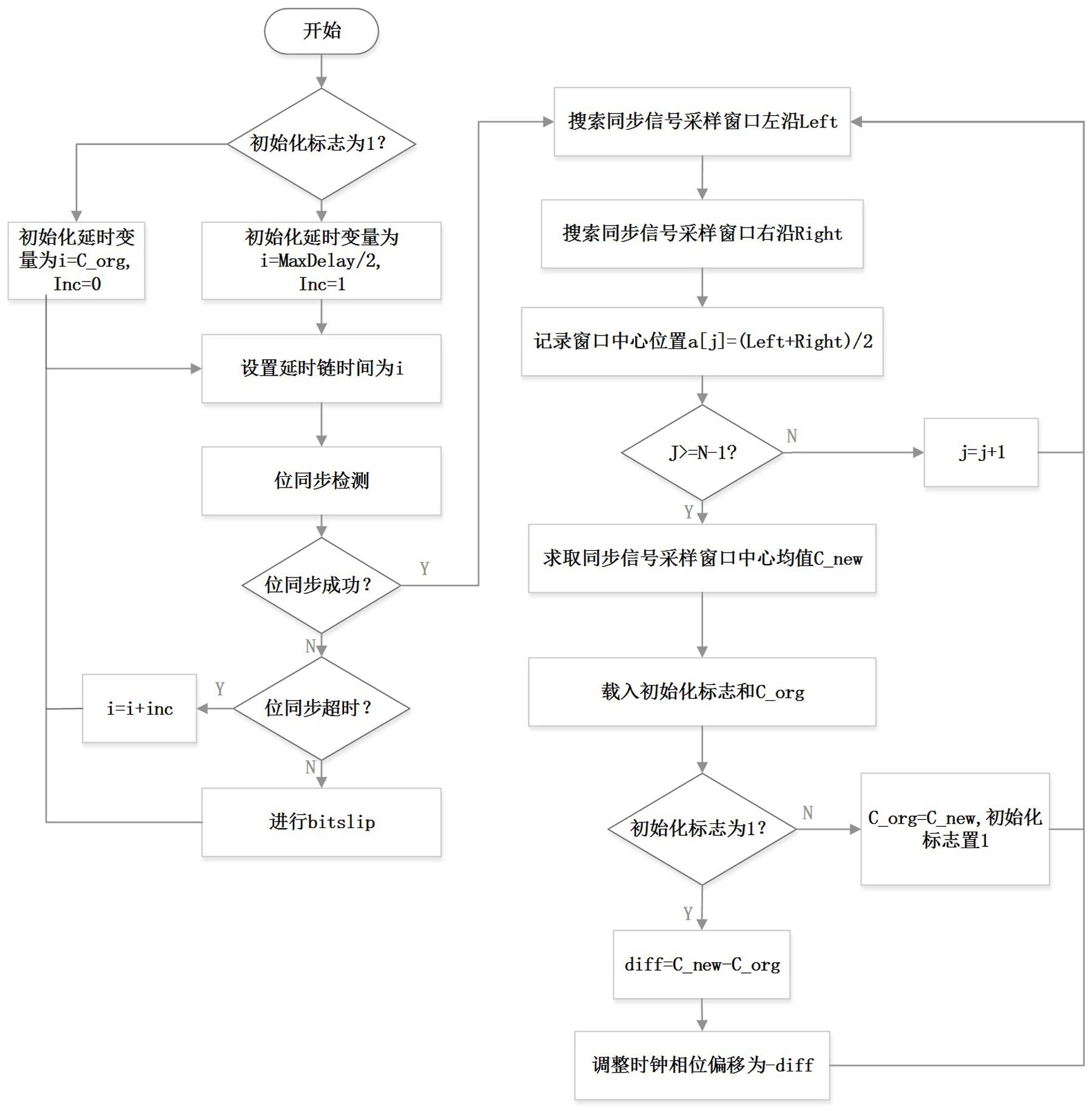

2、为了达到上述目的,本发明采用的技术方案如下:一种基于源同步信号的时钟相位偏移自动补偿方法,包括:先测量同步信号采样窗口中心位置,利用该测量结果初始化和固化延时值c_org,每次fpga数据接收板上电时,首先读取初始化延时值c_org,然后进行比特位对齐,再循环测量n次采样窗口中心位置,并求平均值c_new,根据平均值c_new和延时值c_org的偏差得出时钟相位偏移值diff=c_new-c_org,再用该偏移值补偿时钟相位偏移。

3、进一步地,该方法具体包括以下步骤:

4、s1、读取初始化标志和初始化延时值c_org,若初始化标志为0,则进入步骤s2开始进行初始化,否则进入步骤s3载入初始值;

5、s2、初始化延时链延时值为i=maxdelay/2,设置增量值为inc=1,进入步骤s4;

6、s3、初始化延时链延时值为i=c_org,设置增量值为0,进入步骤s4;

7、s4、设置延时链延时值为i,进行位同步检测,若位同步检测成功,则进入步骤s6,否则进入步骤s5;

8、s5、判断位同步检测是否超时,若超时,则调整延时链延时值i=i+inc,并返回步骤s4重新进行位同步检测,若未超时,则进行一次比特滑动,并返回步骤s4重新进行位同步检测;

9、s6、设置延时链延时值从0至i递增,并检查位同步匹配结果,当出现位同步匹配时,记录该窗口左侧边沿left,再进入步骤s7;

10、s7、设置延时链延时值从maxdelay至i递减,并检查位同步匹配结果,当出现位同步匹配时,记录该窗口右侧边沿right,再进入步骤s8;

11、s8、记录窗口中心位置a[j]=( left+right)/2,进行n次测量后,求取此次计算的窗口中心均值c_new=,再判断初始化标志,若初始化标志为0,则令c_org=c_new,初始化标志置1并固化进非易失性存储器,再返回步骤s6重新开始计算,若初始化标志为1,则进入步骤s9;

12、s9、计算同步信号采样口相位偏移量diff=c_new-c_org,并利用该偏移量反向补偿数据时钟。

13、进一步地,若测得同步信号的采样窗口中心点相位偏移值diff为正值,则将时钟管理器输出时钟clk_adj与输入时钟clk之间的延时值缩小时钟相位偏移值diff,若同步信号的采样窗口中心点相位偏移值diff为负值,则将clk_adj与clk之间的相位值扩大时钟相位偏移值diff。

14、进一步地,所述步骤s1中是从非易失存储器中读取初始化标志和初始化延时值c_org。

15、进一步地,所述步骤s2中的延时链最大延时时间maxdelay为输入信号采样率周期值的2倍或以上,若输入数据率为单沿数据率,则延时链最大延时时间maxdelay至少为输入时钟周期2倍,若输入数据为双沿数据率,则延时链最大延时时间maxdelay至少为输入时钟信号的周期值。

16、进一步地,所述步骤s5中采用串并转换模块进行一次比特滑动,该一次比特滑动为串并转换寄存器逻辑右移一位。

17、与现有技术相比,本发明的优点在于:本发明提供的一种基于源同步信号的时钟相位偏移自动补偿方法,针对能输出同步信号的源端设备如ad9653、fpga等,通过使用源时钟对同步信号采样窗口进行测量,根据窗口中心位置的偏移获取时钟相位的偏移值,利用该偏移量反向补偿时钟相位,使输入数据信号相对时钟的相位偏移保持稳定,从而实现数据的稳定传输。

技术特征:

1.一种基于源同步信号的时钟相位偏移自动补偿方法,其特征在于,包括:先测量同步信号采样窗口中心位置,利用该测量结果初始化和固化延时值c_org,每次fpga数据接收板上电时,首先读取初始化延时值c_org,然后进行比特位对齐,再循环测量n次采样窗口中心位置,并求平均值c_new,根据平均值c_new和延时值c_org的偏差得出时钟相位偏移值diff=c_new-c_org,再用该偏移值补偿时钟相位偏移。

2.根据权利要求1所述的基于源同步信号的时钟相位偏移自动补偿方法,其特征在于,具体包括以下步骤:

3.根据权利要求1所述的基于源同步信号的时钟相位偏移自动补偿方法,其特征在于,若测得同步信号的采样窗口中心点相位偏移值diff为正值,则将时钟管理器输出时钟clk_adj与输入时钟clk之间的延时值缩小时钟相位偏移值diff,若同步信号的采样窗口中心点相位偏移值diff为负值,则将clk_adj与clk之间的相位值扩大时钟相位偏移值diff。

4.根据权利要求2所述的基于源同步信号的时钟相位偏移自动补偿方法,其特征在于,所述步骤s1中是从非易失存储器中读取初始化标志和初始化延时值c_org。

5.根据权利要求2所述的基于源同步信号的时钟相位偏移自动补偿方法,其特征在于,所述步骤s2中的延时链最大延时时间maxdelay为输入信号采样率周期值的2倍或以上,若输入数据率为单沿数据率,则延时链最大延时时间maxdelay至少为输入时钟周期2倍,若输入数据为双沿数据率,则延时链最大延时时间maxdelay至少为输入时钟信号的周期值。

6.根据权利要求2所述的基于源同步信号的时钟相位偏移自动补偿方法,其特征在于,所述步骤s5中采用串并转换模块进行一次比特滑动,该一次比特滑动为串并转换寄存器逻辑右移一位。

技术总结

本发明公开了一种基于源同步信号的时钟相位偏移自动补偿方法,包括:首先测量同步信号采样窗口中心位置,利用该测量结果初始化和固化延时值C_org,每次FPGA数据接收板上电时,首先读取初始化延时值C_org,然后进行比特位对齐,再循环测量N次采样窗口中心位置,并求平均值C_new,根据平均值C_new和延时值C_org的偏差得出时钟相位偏移值diff=C_new‑C_org,再用该偏移值补偿时钟相位偏移。本发明能使输入数据信号相对时钟的相位偏移保持稳定,从而实现数据的稳定传输。

技术研发人员:尹清清,邱兆坤,李凯,成葵交,王孝辉,罗敏,刘柯呈,张国柱,袁宏成,吴礼杰

受保护的技术使用者:湖南跨线桥航天科技有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!