FPGA板卡的HDMI接口的自动化测试系统及方法与流程

本发明涉及板卡测试,具体涉及一种fpga板卡的hdmi接口的自动化测试系统及方法。

背景技术:

1、目前市面上测试fpga板卡的hdmiin和hdmiout外设方法都是通过将图像输入设备接入hdmiin外设,然后再将显示器接入到hdmiout外设。将输入的图像通过hdmiout接口显示到显示器中,然后测试人员观察显示的图像是否正常,即可判断该外设是否正常。

2、这种测试方法存在两个缺陷:

3、1、需要借助其他设备并且需要人工参与观察,不能实现自动化测试,非常不方便;

4、2、不能直观确定测试结果,只能通过测试人员的经验确定大致情形,测试不准确,而且技术难度高,适用性低。

技术实现思路

1、本发明的目的在于提供一种fpga板卡的hdmi接口的自动化测试系统及方法,其无需借助其他设备即可快速测试hdmi外设。

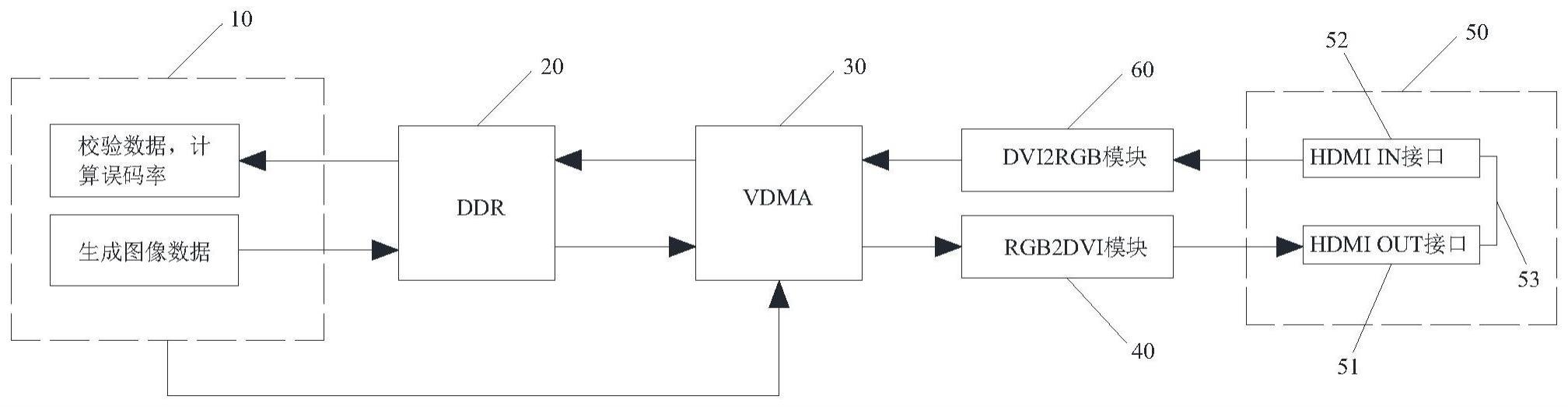

2、为实现上述目的,本发明第一方面公开了一种fpga板卡的hdmi接口的自动化测试系统,所述fpga板卡包括fpga本体以及与所述fpga本体电性连接的ddr和计时器,所述hdmi接口包括hdmi输入接口和hdmi输出接口,所述fpga板卡中还嵌入vdma,所述自动化测试系统还包括hdmi线材,所述hdmi线材连接所述hdmi输入接口和hdmi输出接口;

3、所述fpga本体用于创建第一数据,并将所述第一数据存储于ddr中;

4、所述fpga本体与所述vdma进行通讯,以使所述vdma从所述ddr中获取所述第一数据,并将所述第一数据经由hdmi输出接口输出至所述hdmi输入接口,再通过所述vdma接收,形成第二数据,所述fpga本体还驱动所述vdma将所述第二数据存储至所述ddr中;

5、所述fpga本体还根据所述第一数据和第二数据的比对结果计算得到所述hdmi接口的误码率,或/和,所述fpga本体还获取启动vdma搬运第一数据为起始点,至vdma接收到第二数据为终点的计时时间,并根据所述计时时间以及第一数据或第二数据的数据大小计算hdmi接口的传输速率,所述计时时间通过所述计时器完成。

6、作为一种可选的实施方式,在本发明第一方面中,所述第一数据为图像数据或视频数据;

7、当所述第一数据为图像数据时,所述自动化测试系统还包括图像转换模块,所述图像转换模块用于在第一数据发送至hdmi输出接口时,将所述第一数据转换为tdms信号的第一一数据,并在第一一数据经由hdmi输入接口发送至所述vdma时,将所述第一一数据转换为图像格式的第二数据。

8、作为一种可选的实施方式,在本发明第一方面中,所述图像转换模块包括rgb2dvi模块和dvi2rgb模块,其中,所述rgb2dvi模块电性连接于所述vdma的第一输出接口和hdmi输出接口之间,用于将所述第一数据转换为第一一数据,所述dvi2rgb模块电性连接于hdmi输入接口和所述vdma的第一输入接口之间,用于将所述第一一数据转换为第二数据。

9、作为一种可选的实施方式,在本发明第一方面中,通过所述fpga本体设置循环传输次数,根据所述循环传输次数通过所述hdmi接口循环传输所述第一数据和接收所述第二数据;计算所述传输速率和误码率的平均值或方差,以确定所述hdmi接口的稳定性。

10、本发明第二方面中公开了一种fpga板卡的hdmi接口的自动化测试方法,所述fpga板卡包括fpga本体以及与所述fpga本体电性连接的ddr和计时器,所述hdmi接口包括hdmi输入接口和hdmi输出接口,所述fpga板卡中还嵌入vdma,通过hdmi线材连接所述hdmi输入接口和hdmi输出接口;

11、所述自动化测试方法包括以下步骤:

12、通过所述fpga本体构造第一数据,并存储于所述ddr中;

13、通过所述fpga本体启动所述vdma从所述ddr中搬运第一数据,并启动计时器开始计时;

14、等待vdma接收第二数据,在vdma接收完成后,停止计时器计时;所述第二数据为vdma将所述第一数据经由hdmi输出接口输出至所述hdmi输入接口,再通过所述vdma接收形成的;

15、所述fpga本体读取所述第一数据和第二数据,并根据所述第一数据和第二数据的比对结果计算得到所述hdmi接口的误码率,或/和,所述fpga本体获取计时器的计时时间,并根据所述计时时间以及第一数据或第二数据的数据大小计算hdmi接口的传输速率。

16、作为一种可选的实施方式,在本发明第二方面中,所述fpga本体获取计时器的计时时间,并根据所述计时时间以及第一数据或第二数据的数据大小计算hdmi接口的传输速率,包括:

17、通过所述第一数据或第二数据的数据大小除以所述计时时间确定所述传输速率。

18、作为一种可选的实施方式,在本发明第二方面中,所述第一数据为图像数据或视频数据;

19、当所述第一数据为图像数据时,还包括通过图像转换模块在第一数据发送至hdmi输出接口时,将所述第一数据转换为tdms信号的第一一数据,并在第一一数据经由hdmi输入接口发送至所述vdma时,将所述第一一数据转换为图像格式的第二数据。

20、作为一种可选的实施方式,在本发明第二方面中,通过图像转换模块在第一数据发送至hdmi输出接口时,将所述第一数据转换为tdms信号的第一一数据,包括:使用rgb2dvi模块电性连接于所述vdma的第一输出接口和hdmi输出接口之间,将所述第一数据转换为第一一数据;

21、通过图像转换模块在第一一数据经由hdmi输入接口发送至所述vdma时,将所述第一一数据转换为图像格式的第二数据,包括:使用dvi2rgb模块电性连接于hdmi输入接口和所述vdma的第一输入接口之间,将所述第一一数据转换为第二数据。

22、作为一种可选的实施方式,在本发明第二方面中,通过所述fpga本体设置循环传输次数,根据所述循环传输次数通过所述hdmi接口循环传输所述第一数据和接收所述第二数据;计算所述传输速率和误码率的平均值或方差,以确定所述hdmi接口的稳定性。

23、相比现有技术,本发明的有益效果在于:

24、本发明实施例通过在fpga里面增加vdma的功能,用于测试fpga的hdmi接口性能和稳定性。通过hdmi线材将hdmi输入接口和hdmi输出接口短接进行回环测试,就可以测试该外设是否正常,不需要借助其他设备和人工参与观察,测试直观准确的同时,还大大提升测试效率,节约测试成本。

技术特征:

1.一种fpga板卡的hdmi接口的自动化测试系统,所述fpga板卡包括fpga本体以及与所述fpga本体电性连接的ddr和计时器,所述hdmi接口包括hdmi输入接口和hdmi输出接口,其特征在于,所述fpga板卡中还嵌入vdma,所述自动化测试系统还包括hdmi线材,所述hdmi线材连接所述hdmi输入接口和hdmi输出接口;

2.根据权利要求1所述的fpga板卡的hdmi接口的自动化测试系统,其特征在于,所述第一数据为图像数据或视频数据;

3.根据权利要求2所述的fpga板卡的hdmi接口的自动化测试系统,其特征在于,所述图像转换模块包括rgb2dvi模块和dvi2rgb模块,其中,所述rgb2dvi模块电性连接于所述vdma的第一输出接口和hdmi输出接口之间,用于将所述第一数据转换为第一一数据,所述dvi2rgb模块电性连接于hdmi输入接口和所述vdma的第一输入接口之间,用于将所述第一一数据转换为第二数据。

4.根据权利要求1-3任一项所述的fpga板卡的hdmi接口的自动化测试系统,其特征在于,通过所述fpga本体设置循环传输次数,根据所述循环传输次数通过所述hdmi接口循环传输所述第一数据和接收所述第二数据;计算所述传输速率和误码率的平均值或方差,以确定所述hdmi接口的稳定性。

5.一种fpga板卡的hdmi接口的自动化测试方法,所述fpga板卡包括fpga本体以及与所述fpga本体电性连接的ddr和计时器,所述hdmi接口包括hdmi输入接口和hdmi输出接口,其特征在于,所述fpga板卡中还嵌入vdma,通过hdmi线材连接所述hdmi输入接口和hdmi输出接口;

6.根据权利要求5所述的fpga板卡的hdmi接口的自动化测试方法,其特征在于,所述fpga本体获取计时器的计时时间,并根据所述计时时间以及第一数据或第二数据的数据大小计算hdmi接口的传输速率,包括:

7.根据权利要求5所述的fpga板卡的hdmi接口的自动化测试方法,其特征在于,所述第一数据为图像数据或视频数据;

8.根据权利要求7所述的fpga板卡的hdmi接口的自动化测试方法,其特征在于,通过图像转换模块在第一数据发送至hdmi输出接口时,将所述第一数据转换为tdms信号的第一一数据,包括:使用rgb2dvi模块电性连接于所述vdma的第一输出接口和hdmi输出接口之间,将所述第一数据转换为第一一数据;

9.根据权利要求5-8任一项所述的fpga板卡的hdmi接口的自动化测试方法,其特征在于,通过所述fpga本体设置循环传输次数,根据所述循环传输次数通过所述hdmi接口循环传输所述第一数据和接收所述第二数据;计算所述传输速率和误码率的平均值或方差,以确定所述hdmi接口的稳定性。

技术总结

本发明公开了一种FPGA板卡的HDMI接口的自动化测试系统及方法,FPGA板卡包括FPGA本体以及DDR和计时器,HDMI接口包括HDMI输入接口和HDMI输出接口,FPGA板卡中还嵌入VDMA,自动化测试系统还包括HDMI线材,HDMI线材连接HDMI输入接口和HDMI输出接口;FPGA本体用于创建第一数据并存储于DDR中;FPGA本体驱动VDMA从DDR中获取第一数据,并将第一数据经由HDMI输出接口输出至HDMI输入接口,再通过VDMA接收,形成第二数据,FPGA本体计算得到HDMI接口的误码率和/或传输速率。实施本发明实施例,无需借助其他设备即可快速测试HDMI外设。

技术研发人员:梁乐荣,梁权荣,周伯齐

受保护的技术使用者:广州创龙电子科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!