一种视频编码快速隐式选择变换方法及装置

本发明属于视频编解码,涉及有损视频编码技术,尤其涉及一种视频编码快速隐式选择变换方法和面向该方法的视频编码器变换电路。

背景技术:

1、avs3视频编码标准是一种有损视频编码方式,对于帧内预测产生残差的编码效果直接影响重构图像的质量。由于帧内预测使用的是基于一维线性模型对二维编码单元进行预测的方式,准确度相对较低,产生残差也相对较大。karhunen-loeve(k-l)变换理论上是有损视频编码的最佳的变换方法,离散余弦变换dct-ⅱ(discrete cosine transform-ⅱ)是k-l变换的最近似变换方案,可以平衡编码效率和运算复杂度的关系,在目前avs3标准硬件编码器中,采用dct-ⅱ单一固定变换核。然而,单一固定变换核对于具有高度动态图像统计量的自然图像和视频的自适应性十分有限。因此,需要引入适当的变换核以适应帧内预测产生残差的多样分布特性,并解决引入新的变换核会增加变换标识额外开销的问题。avs3中引入了更大的变换块尺寸,对应支持4*4到64*64尺寸大小的变换操作,如何在保证视频编码器硬件电路面积合理的情况下实现所有尺寸的变换操作是视频编码器硬件设计中的一大难点。

2、可见,单一固定变换核对于具有高度动态图像统计量的自然图像和视频的自适应性十分有限,引入新的变换核会增加变换标识额外开销。目前,现有技术暂无avs3编码标准的快速隐式变换方法和硬件结构。最近的相关工作中,文献(y.zhang et al.,"implicit-selected transform in video coding,"2020ieee international conference onmultimedia&expo workshops(icmew),london,uk,2020,pp.1-6,doi:10.1109/icmew46912.2020.9105962.)提出了一种隐择变换方法,在dct-ⅱ变换核的基础上增加了一种新的变换核dst-ⅶ,为了不增加额外的标志位开销,利用量化系数中非零系数个数的奇偶性来标识变换类型,但是,该方法由于引入新的变换核会导致运算量翻倍,从而导致视频编码器编码电路中的变换模块所消耗的时钟周期数和硬件资源大大增加,不利于硬件设计。文献(宋佳柔,施隆照.一种hevc高速并行的dct架构[j].中国集成电路,2021,30(11):50-55.)提出了一种二维dct变换平行结构,吞吐率高,适用于实时编码场景,但是,该结构只支持一种变换核,不适用于含有多种变换核的变换模块,难以实现多变换核的视频编解码帧内预测。

技术实现思路

1、为了克服上述现有技术的不足,本发明提供一种硬件友好的视频编码快速隐式选择变换方法和视频编码器变换电路,包括:基于帧内预测残差块空间分布特性的快速隐式选择变换算法以及基于改良rag-n(n-dimensional reduced adder graph algorithm)算法的视频编码器变换模块硬件结构设计,通过合理安排视频编码器电路各并行流水线实现电路面积和速度之间的平衡,且能减少计算时间,使得有损视频编码消耗的硬件资源和对残差块的变换过程所需要的时钟周期数都较少,且更易于实现。

2、本发明提供的技术方案是:

3、一种硬件友好的视频编码快速隐式选择变换方法,输入视频编码过程中帧内预测产生的残差块,采用两种变换核对帧内预测产生的残差块进行变换操作;基于残差块的空间分布特性和变换核的特点,可以实现两种变换核的快速选择,得到视频编码变换系数。包括如下步骤:

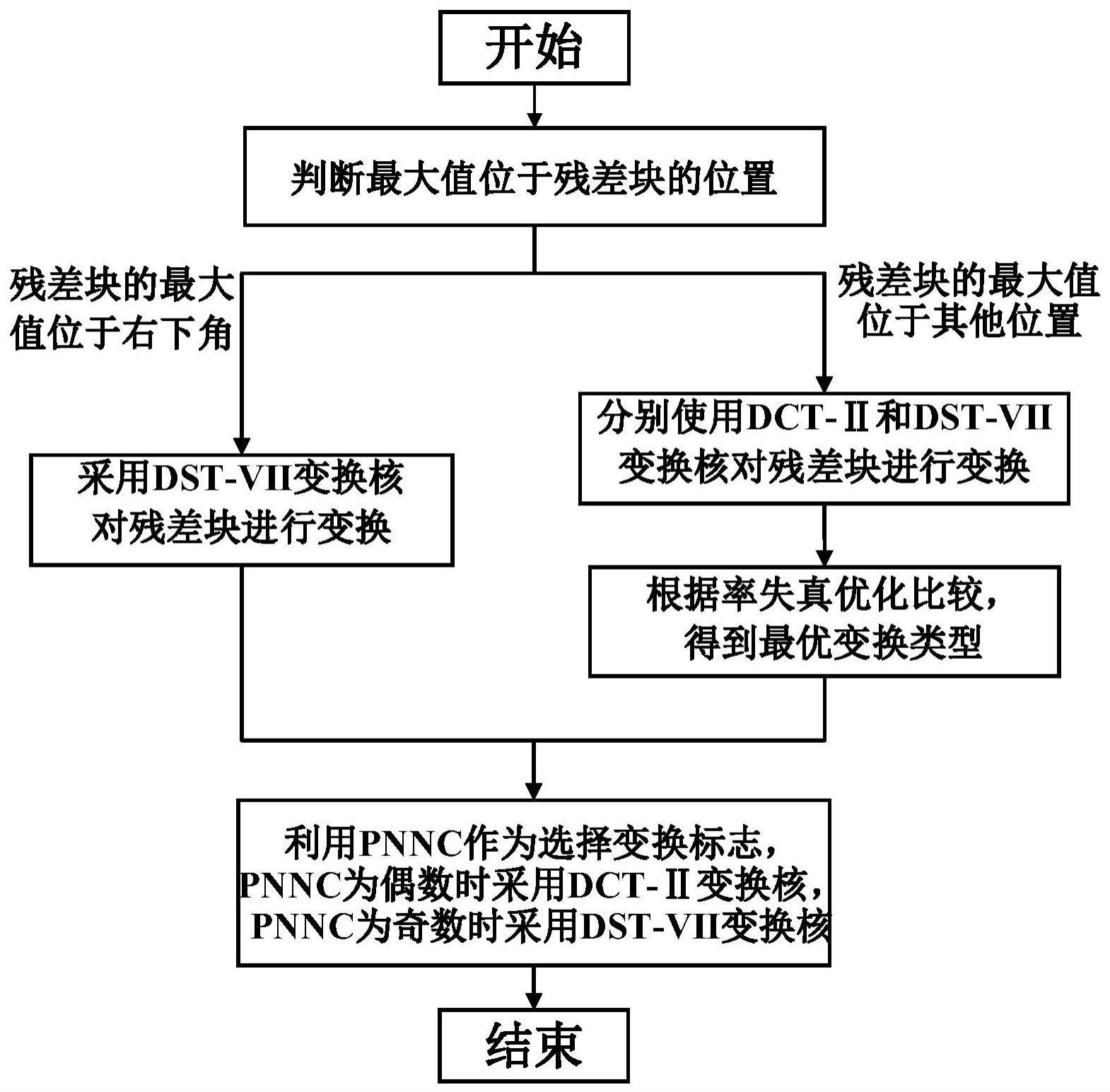

4、1)在视频编码生成帧内预测残差块时记录残差块中绝对值为最大值的残差的坐标;根据坐标,判断绝对值最大的残差位于帧内预测残差块的位置;

5、2)若绝对值最大的残差位于残差块的右下角,则采用dst-ⅶ变换核对残差块进行变换;

6、若绝对值最大的残差位于其他位置,则分别使用dct-ⅱ和dst-ⅶ变换核对残差块进行变换,并根据率失真优化进行比较,得到其中最优的变换类型;

7、3)利用视频编码量化过程中产生的非零量化系数个数的奇偶性作为选择变换标志;

8、当非零量化系数为偶数时采用dct-ⅱ变换核;当非零量化系数为奇数时采用dst-ⅶ变换核。

9、本发明具体实施时,将上述视频编码快速隐式选择变换方法应用于avs3编码中边长为4*4~32*32大小的视频编码帧内预测残差块。

10、本发明面向快速隐式选择变换方法,设计了一种avs3视频编码器的变换电路,支持4*4到64*64尺寸的所有视频编码帧内预测残差块,设计视频编码器电路的并行编码流水线,使得电路的面积和视频编码计算速度之间保持平衡;包括一维水平dst/dct变换模块、转置存储器模块、一维垂直dst/dct变换模块。dst和dct变换均为可分离变换,可以分解成两次一维变换。一维水平dst/dct变换模块用于处理第一次一维水平变换过程。对第一次水平变换的输出结果逐行保存在转置存储器中,再逐列取出,便可以实现转置功能。从转置存储器中逐列取出数据传递给一维垂直dst/dct变换模块,进行垂直变换,得到最终变换结果。

11、与现有技术相比,本发明的有益效果是:

12、本发明提供一种硬件友好的视频编码快速隐式选择变换方法和面向该方法的变换电路,设计了avs3编码标准中一种新的变换算法方案,基于帧内预测残差块空间分布特性的快速隐式变换方法,应用于边长为4*4~32*32大小的视频编码帧内预测残差块。并提出面向快速隐式选择变换方法的变换电路装置,支持4*4到64*64尺寸的所有残差块,通过合理安排视频编码器电路各并行流水线实现电路面积和速度之间的平衡。本发明添加一种新的变换核而不增加额外的比特开销,同时还能减少计算时间。本发明技术方案使得有损视频编码消耗的硬件资源和对残差块的变换过程所需要的时钟周期数都较少,且更易于实现。

技术特征:

1.一种视频编码快速隐式选择变换方法,其特征是,输入视频编码过程中帧内预测产生的残差块,采用两种变换核对帧内预测产生的残差块进行变换操作,实现两种变换核的快速选择,得到视频编码变换系数;包括如下步骤:

2.如权利要求1所述的视频编码快速隐式选择变换方法,其特征是,将所述的视频编码快速隐式选择变换方法应用于avs3编码中边长为4*4~32*32大小的视频编码帧内预测残差块。

3.一种实现权利要求1所述的视频编码快速隐式选择变换方法的装置,其特征是,所述装置包括一维水平dst/dct变换模块、转置存储器模块、一维垂直dst/dct变换模块;

4.如权利要求3所述的装置,其特征是,所述装置为针对avs3视频编码器的变换电路,支持4*4~16*16尺寸的所有视频编码帧内预测残差块,通过设计视频编码器电路的并行编码流水线,使得电路的面积和视频编码计算速度之间保持平衡。

5.如权利要求3所述的装置,其特征是,所述装置的电路内部的一维水平dst/dct变换模块和一维垂直dst/dct变换模块均采用移位加法器完成乘加运算。

6.如权利要求3所述的装置,其特征是,n点变换电路的一维水平dst/dct变换模块包括n个移位加法器。

技术总结

本发明公布了一种视频编码快速隐式选择变换方法及装置,输入视频编码过程中帧内预测产生的残差块,采用两种变换核对帧内预测产生的残差块进行变换操作,实现两种变换核的快速选择,得到视频编码变换系数;视频编码快速隐式选择变换装置包括一维水平DST/DCT变换模块、转置存储器模块、一维垂直DST/DCT变换模块;转置存储器设置在一维水平变换和一维垂直变换之间,用于数据传递。本发明技术方案可使得有损视频编码消耗的硬件资源和对残差块的变换过程所需要的时钟周期数都较少,减少计算时间,且更易于实现。

技术研发人员:严伟,佟思凯,张鹏,向国庆

受保护的技术使用者:北京大学

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!