基于LVDS串行总线的有源相控阵天线波束控制电路的制作方法

本发明涉及有源相控阵天线阵列控制领域,具体而言,涉及一种基于lvds串行总线的有源相控阵天线波束控制电路。

背景技术:

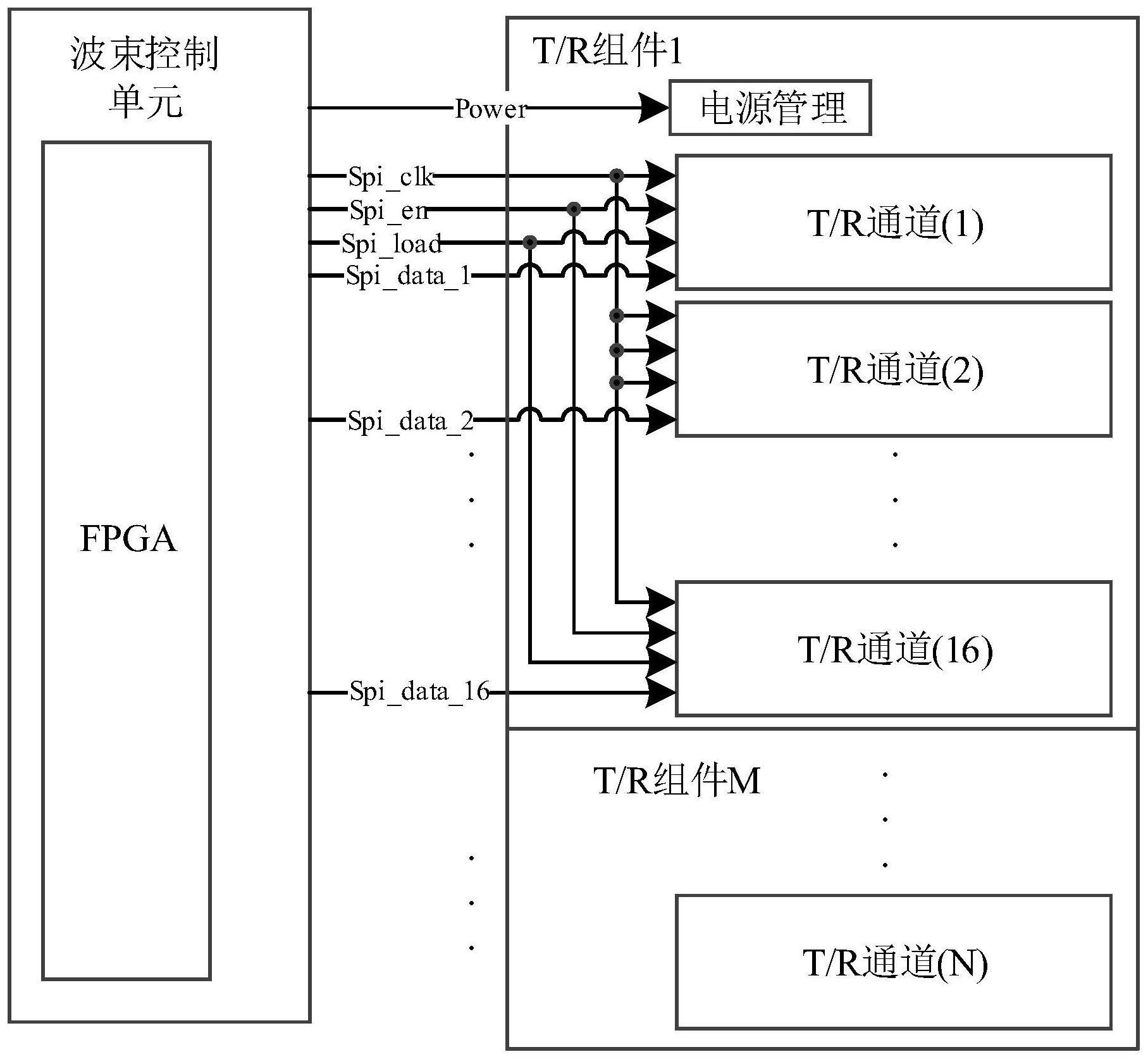

1、近10年来,随着集成电路技术的快速发展,国内外有源相控阵天线技术正处于蓬勃发展时期,该技术在雷达、卫星通信、导引头、电子战及5g通信等领域中承担着越来越重要的角色。但随着相控阵天线阵元规模的扩大,如在上千个阵列单元的大规模有源相控阵天线控制领域,波束控制单元与t/r收发组件之间的控制接口数量成倍数增加,传统的基于spi控制接口的有源相控阵天线阵列控制电路架构正面临着可靠性、成本、功耗、体积等多个维度的困难和挑战。

2、传统的有源相控阵天线工程实现中,波束控制单元与t/r组件之间通常采用多对点对点的spi控制线来实现t/r组件的移相、衰减及开关电控制等功能。通常情况下,spi控制线数量与t/r组件的通道数成倍数关系。比如一个8通道t/r组件所需的控制线数量多达10个,一个16通道的t/r组件的控制接口控制线数量则高达20个。因此,传统有源相控阵天线控制由于系统有很多的离散控制线,对于有上千个阵列单元的大规模有源相控阵天线更是如此。这就意味着大规模阵列波束控制单元的主控处理器(一般为fpga)需要数量上千的低频i/o接口、更多片的fpga器件、更复杂的接口配置电路、更多的dc/dc电源转换网络、更多的低频互联电缆、更强的电磁干扰因素。这些因素,会对有源相控阵天线阵列的可靠性、成本、功耗、体积、电磁兼容性等维度产生严峻挑战。

技术实现思路

1、本发明旨在提供一种基于lvds串行总线的有源相控阵天线波束控制电路,以解决传统有源相控阵天线控制会对有源相控阵天线阵列的可靠性、成本、功耗、体积、电磁兼容性产生不利影响的问题。

2、本发明提供的一种基于lvds串行总线的有源相控阵天线波束控制电路,包括:

3、设置在波束控制单元中的主控处理器fpga以及集成在t/r组件中的lvds串并转换电路和t/r通道控制电路;

4、所述主控处理器fpga和t/r通道控制电路均与lvds串并转换电路连接;所述t/r通道控制电路与t/r组件中的各个t/r通道连接。

5、进一步的,所述lvds串并转换电路包括lvds串行数据接收器、lvds同步时钟接收器、解串器、输出锁存单元、时序控制单元、锁相环和电源控制单元;

6、lvds串行数据接收器的输入端连接主控处理器fpga的lvds串行数据输出端;lvds串行数据接收器的输出端依次经解串器和输出锁存单元连接各个t/r通道控制电路;

7、lvds同步时钟接收器的输入端连接主控处理器fpga的lvds同步时钟输出端;lvds同步时钟接收器的输出端经锁相环连接时序控制单元;时序控制单元连接解串器、输出锁存单元以及各个t/r通道控制电路的同步时钟接收端。

8、作为优选,主控处理器fpga能够控制lvds串行数据接收器的电源控制单元,使得lvds串行数据接收器实现低功耗工作模式。

9、作为优选,主控处理器fpga对输出锁存单元的驱动能力配置为24ma、12ma、8ma或4ma。

10、作为优选,所述主控处理器fpga与lvds串并转换电路采用lvds串行总线连接。

11、进一步的,当有多个t/r组件时,采用对应数量的lvds串并转换电路,每个lvds串并转换电路连接一个t/r组件。

12、进一步的,所述基于lvds串行总线的有源相控阵天线波束控制电路的工作方法,包括:

13、主控处理器fpga将t/r通道的波束控制信息以lvds串行数据发送至lvds串并转换电路,同时发送lvds同步时钟至lvds串并转换电路;

14、lvds串并转换电路将输入的lvds串行数据按照解压比转换为多路并行的lvttl数据;同时,输入的lvds同步时钟,经锁相环锁相后,以lvttl形式同频率输出同步时钟,并始终保持与输出的多路并行的lvttl数据的同步关系;

15、t/r组件中的t/r通道控制电路根据lvds串并转换电路输出端的lvttl控制指令,完成对t/r通道的移相、衰减、电源开关等相关控制。

16、综上所述,由于采用了上述技术方案,相较于基于spi控制接口的传统的有源相控阵天线阵列控制电路架构,本发明的有益效果是:

17、1、本发明克服了通过spi控制接口进行t/r组件控制时常见的串扰、电源干扰等电磁干扰问题。相较于spi总线,采用lvds串行总线控制方式具有低串扰、低功耗、低辐射等优点。

18、2、本发明有效降低了波束控制单元与t/r组件之间控制线的数量。比如对于一个16通道的t/r组件的控制线数量,采用spi总线,所需控制线数量为20个,采用本发明所需的控制线数量为4个,即控制线的数量减少了80%。

19、3、由于采用本发明所需的控制线数量减少了80%,从而有效减少有源相控阵天线系统中控制电缆的数量。

20、4、由于采用本发明所需的控制线数量减少了80%,所以对主控处理器fpga的i/o管脚需求降低了80%。目前主流的控制类fpga,可用i/o管脚数量一般为600个左右,对于大规模的有源相控阵天线,如2000阵元的有源相控阵天线系统,采用本发明时使用一片fpga可完成系统的控制。如果采用传统的spi总线控制方式,则需要5片同规模的fpga器件。对于上万个阵列单元的相控阵天线采用本发明也仅仅需要最多5片fpga器件。fpga器件需求数量的减少,从而使阵列系统的可靠性更高,成本更优、功耗更低、体积更小,电磁兼容性更优。

21、5、本发明采用lvds串行总线的信号传输控制方式,t/r组件的接口更简单,可有效推进有源相控阵天线系统中波束控制电路、t/r组件小型化、标准化电路开发设计。

技术特征:

1.一种基于lvds串行总线的有源相控阵天线波束控制电路,其特征在于,包括:

2.根据权利要求1所述的基于lvds串行总线的有源相控阵天线波束控制电路,其特征在于,所述lvds串并转换电路包括lvds串行数据接收器、lvds同步时钟接收器、解串器、输出锁存单元、时序控制单元、锁相环和电源控制单元;

3.根据权利要求1所述的基于lvds串行总线的有源相控阵天线波束控制电路,其特征在于,主控处理器fpga能够控制lvds串行数据接收器的电源控制单元,使得lvds串行数据接收器实现低功耗工作模式。

4.根据权利要求1所述的基于lvds串行总线的有源相控阵天线波束控制电路,其特征在于,主控处理器fpga对输出锁存单元的驱动能力配置为24ma、12ma、8ma或4ma。

5.根据权利要求1所述的基于lvds串行总线的有源相控阵天线波束控制电路,其特征在于,所述主控处理器fpga与lvds串并转换电路采用lvds串行总线连接。

6.根据权利要求1所述的基于lvds串行总线的有源相控阵天线波束控制电路,其特征在于,当有多个t/r组件时,采用对应数量的lvds串并转换电路,每个lvds串并转换电路连接一个t/r组件。

7.一种如权利要求1-6任一项所述的基于lvds串行总线的有源相控阵天线波束控制电路的工作方法,其特征在于,包括:

技术总结

本发明提供一种基于LVDS串行总线的有源相控阵天线波束控制电路,包括:设置在波束控制单元中的主控处理器FPGA;以及集成在T/R组件中的LVDS串并转换电路和T/R通道控制电路;所述主控处理器FPGA和T/R通道控制电路均与LVDS串并转换电路连接;所述T/R通道控制电路与T/R组件中的各个T/R通道连接。本发明的传输方式更加稳定可靠,可有效减少离散控制线数量,从而使阵列分机的成本更优、功耗更低、体积更小、电磁兼容性更优。

技术研发人员:刘宁宁,杨鹏,张浩斌,甘洋,成章,刘长江

受保护的技术使用者:中国电子科技集团公司第二十九研究所

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!