图像传感器的制作方法

本公开的多种实施例涉及半导体设计技术,更具体地,涉及支持合并(binning)模式的传感器。

背景技术:

1、图像传感器是用于利用对光起反应的半导体的特性来捕获图像的电子设备。图像传感器可以分为电荷耦合器件(ccd)图像传感器和互补金属氧化物半导体(cmos)图像传感器。最近,cmos图像传感器被广泛使用,因为cmos图像传感器可以允许在单个集成电路(ic)上直接实现模拟控制电路和数字控制电路两者。

技术实现思路

1、本公开的多种实施例涉及一种能够在水平方向上执行模拟合并操作的图像传感器。

2、根据本公开的实施例,一种图像传感器可以包括:第一像素组,其包括布置在至少一个行中的第一单元像素电路至第四单元像素电路;第二像素组,其包括布置在至少一个其他行中的第五单元像素电路至第八单元像素电路;第三像素组,其包括布置在至少一个其他行中的第九单元像素电路至第十二单元像素电路;第四像素组,其包括布置在至少一个其他行中的第十三单元像素电路至第十六单元像素电路;第一读出线,其设置在第一列中并且连接至所述第一单元像素电路和所述第九单元像素电路;第二读出线,其设置在第二列中并且连接至所述第五单元像素电路和所述第十三单元像素电路;第三读出线,其设置在第三列中并且连接至所述第二单元像素电路和所述第十单元像素电路;第四读出线,其设置在第四列中并且连接至所述第六单元像素电路和所述第十四单元像素电路;第五读出线,其设置在第五列中并且连接至所述第三单元像素电路和所述第十一单元像素电路;第六读出线,其设置在第六列中并且连接至所述第七单元像素电路和所述第十五单元像素电路;第七读出线,其设置在第七列中并且连接至所述第四单元像素电路和所述第十二单元像素电路;第八读出线,其设置在第八列中并且连接至所述第八单元像素电路和所述第十六单元像素电路;第一读出电路至第四读出电路;以及路径选择器,其适用于:在合并模式下,在单行时间期间经由所述第一读出线至所述第八读出线将所述第一单元像素电路至所述第十六单元像素电路连接至所述第一读出电路至所述第四读出电路。

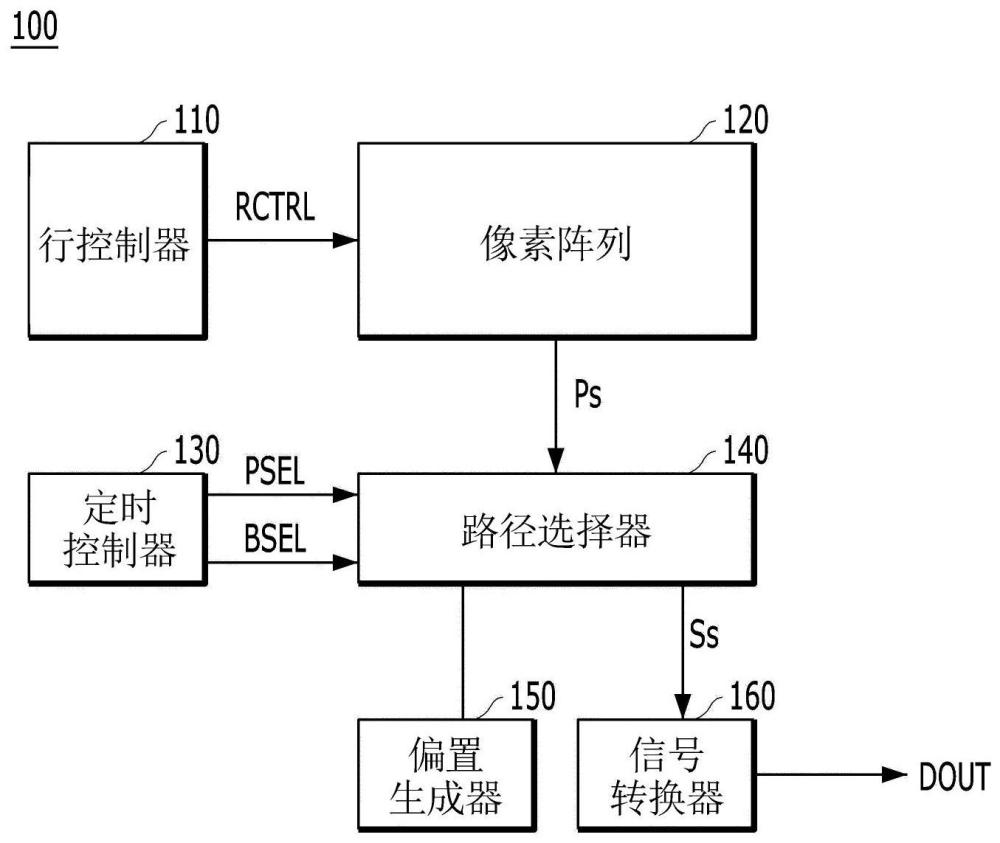

3、根据本公开的实施例,一种图像传感器可以包括:像素阵列,其包括n*m个单元像素电路,其中,n≥2和m≥n;k*n个读出线,其连接至n*m个单元像素电路,其中k≥2;信号转换器,其包括n个读出电路;以及路径选择器,其适用于:在合并模式下,在单行时间期间经由所述k*n个读出线将所述n*m个单元像素电路连接至所述n个读出电路。

4、根据本公开的实施例,一种图像传感器可以包括:像素阵列,其包括多个单元像素电路;多个读出线,其连接至所述多个单元像素电路;多个偏置电路;第一路径选择电路,其耦接在所述多个读出线与所述多个偏置电路之间,并且适用于基于多个第一控制信号将所述多个读出线选择性地连接至所述多个偏置电路;多个读出电路;以及第二路径选择电路,其耦接在所述多个读出线与所述多个读出电路之间,并且适用于基于多个第二控制信号将所述多个读出线选择性地连接至所述多个读出电路。

5、根据本公开的实施例,一种图像传感器可以包括:单元像素电路的4×4阵列;以及外围电路,其被配置为在单行时间内:对通过所述阵列的各个奇数列的奇数读出线输出的像素信号进行平均,以生成第一选择像素信号,对通过所述阵列的各个偶数列的奇数读出线输出的像素信号进行平均,以生成第二选择像素信号,对通过所述各个奇数列的偶数读出线输出的像素信号进行平均,以生成第三选择像素信号,以及对通过所述各个偶数列的偶数读出线输出的像素信号进行平均,以生成第四选择像素信号,其中,布置在所述阵列的奇数行中的所述单元像素电路被耦接至所述阵列的各个列的各个偶数读出线,以及其中,布置在所述阵列的偶数行中的所述单元像素电路被耦接至所述阵列的各个列的各个奇数读出线。

技术特征:

1.一种图像传感器,包括:

2.根据权利要求1所述的图像传感器,其中,所述路径选择器还适用于:在正常模式下,在所述单行时间期间经由所述第一读出线至所述第八读出线的一半将所述第一像素组至所述第四像素组中的一个像素组连接至所述第一读出电路至所述第四读出电路。

3.根据权利要求1所述的图像传感器,

4.根据权利要求3所述的图像传感器,其中,所述路径选择器包括:

5.根据权利要求1所述的图像传感器,

6.根据权利要求5所述的图像传感器,其中,所述路径选择器包括:

7.一种图像传感器,包括:

8.根据权利要求7所述的图像传感器,其中,所述路径选择器在所述合并模式下在所述单行时间期间通过将所述n*m个单元像素电路之中的布置在至少两个行中的至少四个单元像素电路连接至所述n个读出电路中之一,将所述n*m个单元像素电路连接至所述n个读出电路。

9.根据权利要求7所述的图像传感器,其中,所述路径选择器还适用于:在正常模式下,在所述单行时间期间经由所述k*n个读出线中的一些或全部读出线将所述n*m个单元像素电路之中的n*1个单元像素电路分别连接至所述n个读出电路。

10.根据权利要求7所述的图像传感器,

11.根据权利要求10所述的图像传感器,其中,所述路径选择器包括:

12.根据权利要求7所述的图像传感器,

13.根据权利要求12所述的图像传感器,其中,所述路径选择器包括:

14.一种图像传感器,包括:

15.根据权利要求14所述的图像传感器,其中,所述多个读出电路的数量小于所述多个读出线的数量,以及所述多个偏置电路的数量等于所述多个读出电路的数量。

16.根据权利要求14所述的图像传感器,其中,所述多个读出电路的数量小于所述多个读出线的数量,以及所述多个偏置电路的数量等于所述多个读出线的数量。

17.根据权利要求14所述的图像传感器,其中,所述第一路径选择电路在合并模式下在单行时间期间将两个或多个读出线选择性地连接至所述多个偏置电路中之一,并且在正常模式下在所述单行时间期间将一个读出线选择性地连接至一个偏置电路。

18.根据权利要求14所述的图像传感器,其中,所述第一路径选择电路在合并模式下在单行时间期间将一个读出线选择性地连接至一个偏置电路,并且在正常模式下在所述单行时间期间将所述多个偏置电路中的一些偏置电路选择性地连接至所述多个读出线中的一些读出线。

19.根据权利要求14所述的图像传感器,其中,所述第二路径选择电路在合并模式下在单行时间期间将两个或更多个读出线选择性地连接至所述多个读出电路中之一,并且在正常模式下在所述单行时间期间将一个读出线选择性地连接至一个读出电路。

20.一种图像传感器,包括:

技术总结

公开了一种图像传感器,其包括:第一至第四单元像素电路,第五至第八单元像素电路,第九至第十二单元像素电路以及第十三至第十六单元像素电路,连接至第一和第九单元像素电路的第一读出线,连接至第五和第十三单元像素电路的第二读出线,连接至第二和第十单元像素电路的第三读出线,连接至第六和第十四单元像素电路的第四读出线,连接至第三和第十一单元像素电路的第五读出线,连接至第七和第十五单元像素电路的第六读出线,连接至第四和第十二单元像素电路的第七读出线,连接至第八和第十六单元像素电路的第八读出线,第一读出电路至第四读出电路,以及经由读出线将单元像素电路连接至读出电路的路径选择器。

技术研发人员:金东柱

受保护的技术使用者:爱思开海力士有限公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!