基于FPGA的PTP时间同步方法及装置与流程

本公开涉及时间同步,尤其涉及一种基于fpga的ptp时间同步方法及装置。

背景技术:

1、目前的网络时间同步方式主要有gnss(global navigation satellite system,全球卫星导航定位系统)、ntp(network time protocol,网络时间协议)和ptp(precisiontiming protocol精密时间协议)等。需要说明的是,在网络系统中,多个设备间的协同是需要相关设备在时间上首先保证同步的。上述三种时间同步方式中,gnss根据其模块品质和价格的不同,精度从纳秒到百纳秒不等,但受限于使用条件,其卫星信号容易受到楼宇或天气等因素的影响,而接受不到卫星信号的设备是无法与其他设备实现时间同步的。ntp作为将计算机时钟同步至世界协调时utc的网络时间协议,其精度在局域网内可达0.1ms,在互联网绝大多数的地方可达1-50ms,但是缺乏对于高精度需求设备的支持。

2、ptp,即ieee15888,根据演进存在v1和v2两个版本,ieee1588v2在有线网络中能够实现5ns级的时间精度,网络中仅以1个节点作为时间源,其他节点通过ptp技术即可实现与gnss同级别的同步精度。因此,ptp兼具成本与精度的双重优势。

3、但是,由于接收ptp报文的过程中,软件对于ptp报文的处理效率较低,易在软件处理中产生一定的延时,所以提供一种能减少对ptp报文处理过程中延时的方法,进一步的提升时间同步精度,提高处理效率,是目前亟待解决的问题。

技术实现思路

1、有鉴于此,本申请提出一种基于fpga的ptp时间同步方法及装置,以解决上述问题。

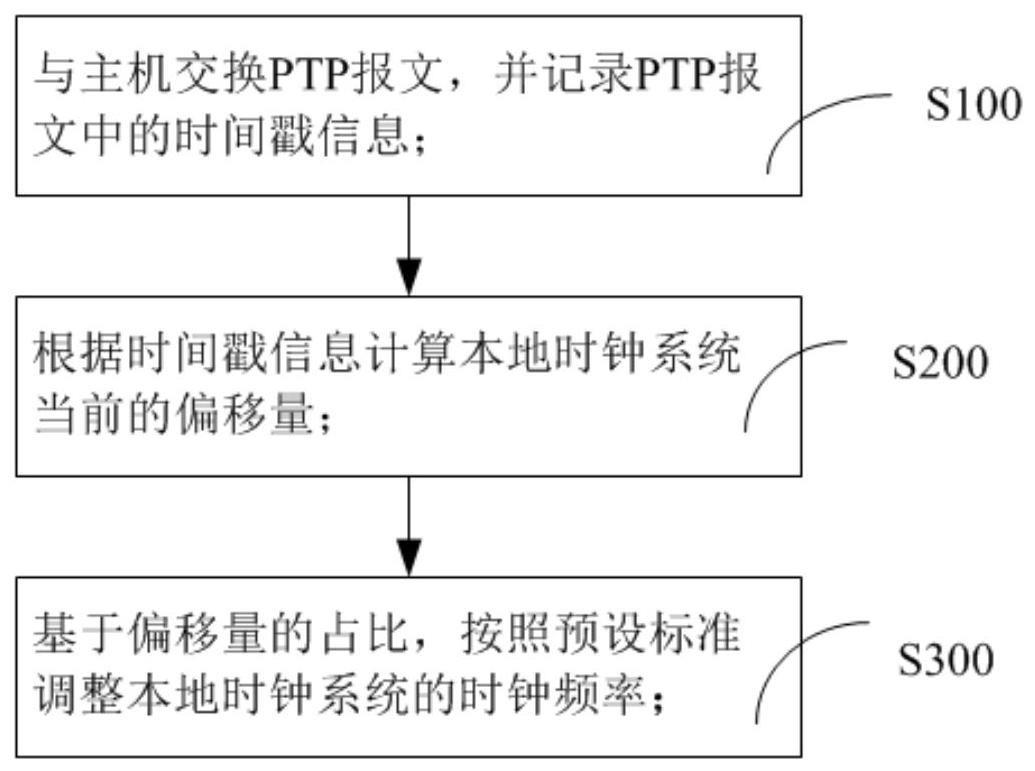

2、本申请一方面,提出一种基于fpga的ptp时间同步方法,包括如下步骤:

3、与主机交换ptp报文,并记录所述ptp报文中的时间戳信息;

4、根据所述时间戳信息计算本地时钟系统当前的偏移量;

5、基于所述偏移量的占比,按照预设标准调整所述本地时钟系统的时钟频率;

6、其中,所述与主机交换ptp报文,并记录所述ptp报文中的时间戳信息基于fpga实现。

7、作为本申请的一可选实施方案,可选地,与主机交换ptp报文,并记录所述ptp报文中的时间戳信息,包括:

8、接收主机发送的sync报文和follow_up报文,记录主机发送时间戳和本地接收时间戳;

9、向所述主机发送delay_req报文,并接收所述主机发送的delay_resp报文,记录本地发送时间戳和主机接收时间戳。

10、作为本申请的一可选实施方案,可选地,接收主机发送的sync报文和follow_up报文,记录主机发送时间戳和本地接收时间戳,包括:

11、接收主机发送的sync报文,记录接收所述sync报文时的本地接收时间戳;

12、接收主机发送的follow_up报文,记录所述follow_up中携带的所述sync报文的主机发送时间戳。

13、作为本申请的一可选实施方案,可选地,向所述主机发送delay_req报文,并接收所述主机发送的delay_resp报文,记录本地发送时间戳和主机接收时间戳,包括:

14、向所述主机发送delay_req报文,并记录发送所述delay_req报文时的本地时间戳;

15、接收所述主机发送的delay_resp报文,记录所述delay_resp报文中携带的所述主机接收所述delay_req报文的主机接收时间戳。

16、作为本申请的一可选实施方案,可选地,在根据所述时间戳信息计算本地时钟系统当前的偏移量时,基于所述主机发送时间戳、所述本地接收时间戳、所述本地发送时间戳和所述主机接收时间戳实现。

17、作为本申请的一可选实施方案,可选地,所述偏移量的计算公式为:

18、toffset=(t2+t3-t1-t4)/2;

19、式中,t1为主机发送时间戳、t2为本地接收时间戳、t3为本地发送时间戳、t4为主机接收时间戳。

20、本申请另一方面,提供一种装置,用于实现上述任一项所述的基于fpga的ptp时间同步方法,包括:

21、ptp报文交换模块,被配置为与主机交换ptp报文,并记录所述ptp报文中的时间戳信息;

22、ptp时钟偏移计算模块,被配置为根据所述时间戳信息计算本地时钟系统当前的偏移量;

23、时钟模块,基于所述偏移量的占比,按照预设标准调整所述本地时钟系统的时钟频率;

24、其中,所述与主机交换ptp报文,并记录所述ptp报文中的时间戳信息基于fpga实现。

25、作为本申请的一可选实施方案,可选地,所述ptp报文交换模块,包括:

26、以太网接收管理模块,被配置为接收主机发送的sync报文、follow_up报文以及delay_resp报文,记录主机发送时间戳、本地接收时间戳和主机接收时间戳;

27、以太网发送管理模块,被配置为向所述主机发送delay_req报文,记录本地发送时间戳。

28、本申请另一方面,提供一种电子设备,包括:处理器;

29、用于存储处理器可执行指令的存储器;

30、其中,所述处理器被配置为执行所述可执行指令时实现上述任一项所述的基于fpga的ptp时间同步方法。

31、本申请再一方面,提供一种非易失性计算机可读存储介质,其上存储有计算机程序指令,其特征在于,所述计算机程序指令被处理器执行时实现上述任意一项所述的基于fpga的ptp时间同步方法。

32、本发明的技术效果:

33、本申请通过fpga作为从机与主机交换ptp报文,并根据ptp报文中的时间戳计算出从机本地时钟偏移量,同时通过偏移量的占比,调整本地时钟系统的时钟频率,从而实现同步的目的。具体的,包括与主机交换ptp报文,并记录ptp报文中的时间戳信息;根据时间戳信息计算本地时钟系统当前的偏移量;基于偏移量的占比,按照预设标准调整本地时钟系统的时钟频率。需要说明的是,由于fpga具备更快的运算能力,能够减少软件处理过程中产生的延时,进一步的提升同步精度。也即基于fpga实现时间同步时,其能够更直接、快速的处理ptp数据帧,且系统更具扩展性,后期也更易维护与升级。

34、根据下面参考附图对示例性实施例的详细说明,本公开的其它特征及方面将变得清楚。

技术特征:

1.一种基于fpga的ptp时间同步方法,其特征在于,包括如下步骤:

2.根据权利要求1所述的基于fpga的ptp时间同步方法,其特征在于,与主机交换ptp报文,并记录所述ptp报文中的时间戳信息,包括:

3.根据权利要求2所述的基于fpga的ptp时间同步方法,其特征在于,接收主机发送的sync报文和follow_up报文,记录主机发送时间戳和本地接收时间戳,包括:

4.根据权利要求2所述的基于fpga的ptp时间同步方法,其特征在于,向所述主机发送delay_req报文,并接收所述主机发送的delay_resp报文,记录本地发送时间戳和主机接收时间戳,包括:

5.根据权利要求2所述的基于fpga的ptp时间同步方法,其特征在于,在根据所述时间戳信息计算本地时钟系统当前的偏移量时,基于所述主机发送时间戳、所述本地接收时间戳、所述本地发送时间戳和所述主机接收时间戳实现。

6.根据权利要求5所述的基于fpga的ptp时间同步方法,其特征在于,所述偏移量的计算公式为:

7.一种装置,用于实现权利要求1-6中任一项所述的基于fpga的ptp时间同步方法,其特征在于,包括:

8.根据权利要求7所述的装置,其特征在于,所述ptp报文交换模块,包括:

9.一种电子设备,其特征在于,包括:

10.一种非易失性计算机可读存储介质,其上存储有计算机程序指令,其特征在于,所述计算机程序指令被处理器执行时实现权利要求1至6中任意一项所述的基于fpga的ptp时间同步方法。

技术总结

本申请涉及一种基于FPGA的PTP时间同步方法及装置,该方法包括与主机交换PTP报文,并记录PTP报文中的时间戳信息;根据时间戳信息计算本地时钟系统当前的偏移量;基于偏移量的占比,按照预设标准调整本地时钟系统的时钟频率;其中,与主机交换PTP报文,并记录PTP报文中的时间戳信息基于FPGA实现。需要说明的是,本申请中由于FPGA具备更快的运算能力,能够减少软件处理过程中产生的延时,进一步的提升同步精度。也即基于FPGA实现时间同步时,其能够更直接、快速的处理PTP数据帧,且系统更具扩展性,后期也更易维护与升级。

技术研发人员:张岩,杨兆平,孙征宇,李丛林

受保护的技术使用者:北京实干兴邦科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!