基于三维堆叠技术的时空差分视觉传感器芯片及成像系统

本发明涉及视觉传感器,尤其涉及一种基于三维堆叠技术的时空差分视觉传感器芯片及成像系统。

背景技术:

1、视觉传感器是一种光电检测器件,这种光电检测器件将包括物体的图像和/或距离(即,深度)信息的光信号转换为电信号。已经开发了各种类型的视觉传感器,诸如aps(active pixel sensor,激活像素感受器)、dvs(dynamic vision sensor,动态视觉传感器)及davis(dynamic and active pixel vision sensor,动态有源像素视觉传感器)等,以提供物体的高质量图像信息。但是,一方面现有的视觉传感器所有电路元件均被制造在一个二维的晶圆上,增大了芯片面积。另一方面现有的视觉传感器只能输出视觉信号在焦平面上的时间变化信息,具有一定的局限性。

技术实现思路

1、本发明提供一种基于三维堆叠技术的时空差分视觉传感器芯片及成像系统,用以解决现有技术中二维视觉传感器芯片面积大且仅输出时间变化信号的缺陷,本发明采用三维堆叠技术设计时空差分视觉传感器芯片,能够有效降低芯片面积,可以同时获得视觉信号的时间和空间变化量,形成高效且鲁棒的视觉表示。

2、本发明提供一种基于三维堆叠技术的时空差分视觉传感器芯片,包括像素阵列、存储电路和时空差分与量化电路;所述像素阵列设置于顶层晶圆上,所述时空差分与量化电路设置于同一底层晶圆上,所述顶层晶圆和所述底层晶圆基于三维堆叠方式连接;所述像素阵列包括多个像素单元;所述像素阵列内设置感光电路;所述感光电路用于将获取的所述像素单元的光信号转换为像素单元的模拟电信号;所述存储电路用于存储所述像素单元的模拟电信号或数字电信号;所述时空差分与量化电路用于将所述像素单元的模拟电信号进行时空差分再量化处理,得到像素单元的数字时空差分电信号,或,所述时空差分与量化电路用于将所述像素单元的模拟电信号进行量化,得到所述像素单元的数字电信号,再将所述像素单元的数字电信号进行时空差分处理,得到像素单元的数字时空差分电信号。

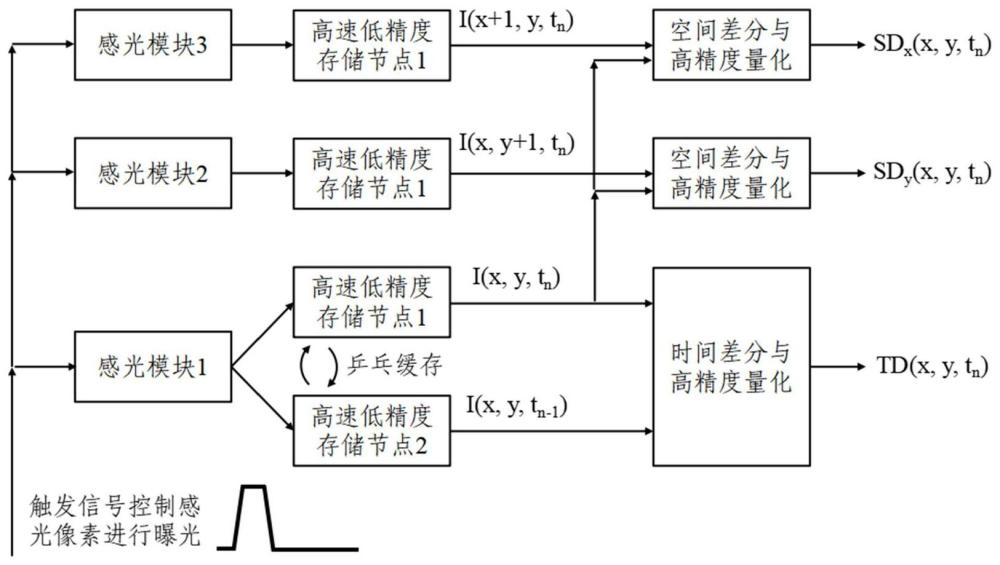

3、根据本发明提供的一种基于三维堆叠技术的时空差分视觉传感器芯片,所述存储电路包括多个存储节点,多个所述存储节点用于采用多节点可随机访问型缓存的方式存储不同位置及不同时刻的所述像素单元的模拟电信号;所述时空差分与量化电路包括时间差分与量化单元和空间差分与量化单元;所述时间差分与量化单元用于将不同时刻的所述像素单元的模拟电信号进行时间差分与量化处理,得到当前像素单元位置不同时刻的时间差分值;所述空间差分与量化单元用于将不同位置的所述像素单元的模拟电信号进行空间差分与量化处理,得到当前时刻当前像素单元位置像素与相邻像素的空间差分值。

4、根据本发明提供的一种基于三维堆叠技术的时空差分视觉传感器芯片,还包括脉冲信号发生器;所述脉冲信号发生器用于对所述感光电路的曝光进行控制。

5、根据本发明提供的一种基于三维堆叠技术的时空差分视觉传感器芯片,每个像素单元内均设置有一个所述脉冲信号发生器,各所述像素单元的数字时空差分电信号采用相同时间间隔或自适应可编程时间间隔的方式输出。

6、根据本发明提供的一种基于三维堆叠技术的时空差分视觉传感器芯片,多个所述像素单元共用一个所述脉冲信号发生器,各所述像素单元的数字时空差分电信号采用相同时间间隔的方式输出。

7、根据本发明提供的一种基于三维堆叠技术的时空差分视觉传感器芯片,所述时空差分与量化电路设置于所述像素单元外,采用列级信号读出的方式。

8、根据本发明提供的一种基于三维堆叠技术的时空差分视觉传感器芯片,所述时空差分与量化电路设置于每个所述像素单元内,采用像素级信号读出的方式。

9、根据本发明提供的一种基于三维堆叠技术的时空差分视觉传感器芯片,所述像素单元的数字电信号以多值的方式进行量化和读出。

10、根据本发明提供的一种基于三维堆叠技术的时空差分视觉传感器芯片,还包括融合电路,所述融合电路用于融合多个所述像素单元的模拟电信号,得到融合后的模拟电信号;所述时空差分与量化电路还用于将所述融合后的模拟电信号进行时空差分与量化处理,得到融合后的数字时空差分电信号。

11、本发明还提供一种成像系统,包括上述的基于三维堆叠技术的时空差分视觉传感器芯片。

12、本发明提供的一种基于三维堆叠技术的时空差分视觉传感器芯片及成像系统,芯片包括像素阵列、存储电路和时空差分与量化电路。像素阵列包括多个像素单元,像素阵列内设置感光电路。采用三维堆叠的方式将像素阵列设置于顶层晶圆上,时空差分与量化电路设置于同一底层晶圆上,大大提高了集成度,能够有效降低芯片面积,同时缓解输出带宽压力。感光电路将获取的像素单元的光信号转换为像素单元的模拟电信号;存储电路存储像素单元的模拟电信号或数字电信号;时空差分与量化电路将像素单元的模拟电信号进行时空差分与量化处理,得到像素单元的数字时空差分电信号,可以同时获得视觉信号的时间和空间变化量,形成高效且鲁棒的视觉表示。

技术特征:

1.一种基于三维堆叠技术的时空差分视觉传感器芯片,其特征在于,包括像素阵列、存储电路和时空差分与量化电路;所述像素阵列设置于顶层晶圆上,所述时空差分与量化电路设置于同一底层晶圆上,所述顶层晶圆和所述底层晶圆基于三维堆叠方式连接;

2.根据权利要求1所述的基于三维堆叠技术的时空差分视觉传感器芯片,其特征在于,所述存储电路包括多个存储节点,多个所述存储节点用于采用多节点可随机访问型缓存的方式存储不同位置及不同时刻的所述像素单元的模拟电信号;

3.根据权利要求1所述的基于三维堆叠技术的时空差分视觉传感器芯片,其特征在于,还包括脉冲信号发生器;所述脉冲信号发生器用于对所述感光电路的曝光进行控制。

4.根据权利要求3所述的基于三维堆叠技术的时空差分视觉传感器芯片,其特征在于,每个像素单元内均设置有一个所述脉冲信号发生器,各所述像素单元的数字时空差分电信号采用相同时间间隔或自适应可编程时间间隔的方式输出。

5.根据权利要求3所述的基于三维堆叠技术的时空差分视觉传感器芯片,其特征在于,多个所述像素单元共用一个所述脉冲信号发生器,各所述像素单元的数字时空差分电信号采用相同时间间隔的方式输出。

6.根据权利要求1所述的基于三维堆叠技术的时空差分视觉传感器芯片,其特征在于,所述时空差分与量化电路设置于所述像素单元外,采用列级信号读出的方式。

7.根据权利要求1所述的基于三维堆叠技术的时空差分视觉传感器芯片,其特征在于,所述时空差分与量化电路设置于每个所述像素单元内,采用像素级信号读出的方式。

8.根据权利要求1所述的基于三维堆叠技术的时空差分视觉传感器芯片,其特征在于,所述像素单元的数字电信号以多值的方式进行量化和读出。

9.根据权利要求1至8任一项所述的基于三维堆叠技术的时空差分视觉传感器芯片,其特征在于,还包括融合电路,所述融合电路用于融合多个所述像素单元的模拟电信号,得到融合后的模拟电信号;

10.一种成像系统,其特征在于,包括权利要求1至9任一项所述的基于三维堆叠技术的时空差分视觉传感器芯片。

技术总结

本发明提供一种基于三维堆叠技术的时空差分视觉传感器芯片及成像系统,芯片包括像素阵列、存储电路和时空差分与量化电路。像素阵列包括多个像素单元,像素阵列内设置感光电路。采用三维堆叠的方式将像素阵列设置于顶层晶圆上,时空差分与量化电路设置于同一底层晶圆上,大大提高了集成度,能够有效降低芯片面积,同时缓解输出带宽压力。感光电路将获取的像素单元的光信号转换为像素单元的模拟电信号;存储电路存储像素单元的模拟电信号或数字电信号;时空差分与量化电路将像素单元的模拟电信号进行时空差分与量化处理,得到像素单元的数字时空差分电信号,可以同时获得视觉信号的时间和空间变化量,形成高效且鲁棒的视觉表示。

技术研发人员:赵蓉,王韬毅,陈雨过,林逸晗,施路平

受保护的技术使用者:清华大学

技术研发日:

技术公布日:2024/3/12

- 还没有人留言评论。精彩留言会获得点赞!