数据加解密处理模块的制作方法

本技术涉及数据安全领域,尤其涉及一种数据加解密处理模块。

背景技术:

1、物联网设备安全问题已经成为新的信息安全隐患,主流的物联网安全防护集中在网络及系统层面,忽略了设备硬件自身安全性。而现有技术公开的安全模块一般集成信号发生器,通过算法对输出信号随机采样并做运算,将得到的伪随机数作为密钥,再结合加密算法对数据加密,该种方式在黑客监听获取到密钥算法后很容易破译密文。

技术实现思路

1、本实用新型提供一种数据加解密处理模块,通过将真随机的量子密钥存储在密钥存储器上,无需soc芯片内部再生成伪随机密钥,以解决现有技术中数据加密安全性不高的技术问题,同时提高加解密处理速率。

2、本实用新型采用的技术方案如下:

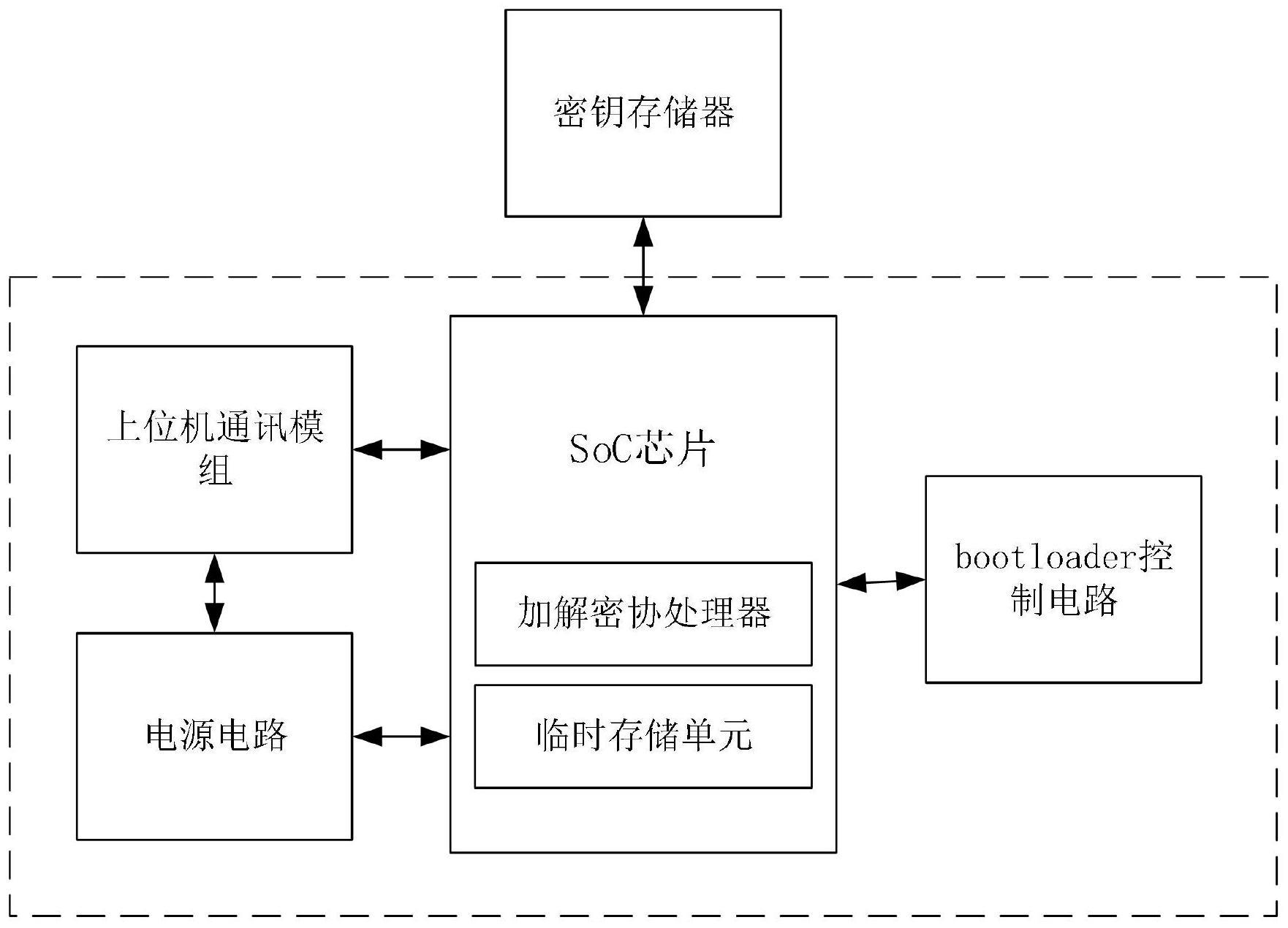

3、一种数据加解密处理模块,包括soc芯片和密钥存储器,所述soc芯片和所述密钥存储器通过pcb板电气连接,且两者基于spi接口通讯;所述密钥存储器用于存储量子密钥,所述soc芯片集成有加解密协处理器和临时存储单元,所述临时存储单元用于缓存待加密数据,所述加解密协处理器用于将所述待加密数据和所述量子密钥代入国密算法实现数据加解密。

4、进一步的,还包括第一通讯单元,所述第一通讯单元与所述soc芯片基于usb接口通讯;所述第一通讯单元具有两排定义相同的引脚。

5、进一步的,还包括第二通讯单元,所述第二通讯单元与所述第一通讯单元定义相同的引脚连接;所述第一通讯单元和所述第二通讯单元设于所述pcb板的对端,共同组成所述数据加解密处理模块的上位机通讯模组。

6、进一步的,所述pcb板设有电源电路,所述电源电路的第一通电端连接所述上位机通讯模组,并依次经串联的第一发光二极管和第一分压电阻接地;所述电源电路的第二通电端连接所述soc芯片,并经稳压管接地;所述第一通电端和所述第二通电端之间设有第二分压电阻。

7、进一步的,所述pcb板设有bootloader控制电路,所述bootloader控制电路具有电源端、接地端和控制端,分别与所述soc芯片对应功能的引脚连接;其中,所述电源端和所述控制端之间依次串联第三分压电阻和第二发光二极管,所述控制端和所述接地端之间设有端子开关,所述端子开关用于在导通状态下使所述数据加解密处理模块切换至下载代码模式。

8、进一步的,所述密钥存储器至少通过数据输入引脚、数据输出引脚、控制引脚、时钟引脚、片选引脚和电源引脚连接于所述soc芯片,且所述电源引脚经第一去耦电容接地。

9、进一步的,所述密钥存储器和所述soc芯片设于所述pcb板的相反两侧。

10、进一步的,所述pcb板设有保护电路,所述保护电路分别连接所述soc芯片的vdd33引脚和vdd引脚;其中,所述保护电路包括并联的第二去耦电容和第三去耦电容,所述第二去耦电容的容量为3.3μf,所述第三去耦电容容量为0.1μf。

11、与现有技术相比:本实用新型具有以下有益效果:

12、(1)本实用新型将用于加解密数据的量子密钥存储在密钥存储器中,无需soc芯片内部再集成信号发生器以生成伪随机密钥,能够解决现有技术中数据加密安全性不高的技术问题,同时提高加解密处理速率。

13、(2)本实用新型将密钥存储器与soc芯片分开设置,便于通过上位机通讯模组实现量子密钥充注。

14、(3)本实用新型布设密钥存储器和soc芯片位于pcb板的相反侧,上位机通讯模组与soc芯片同侧设置,充分利用pcb板空间,避免板子过大导致上位机需要留存较大的安装空间,进而导致上位机体积增大。

15、(4)本实用新型设置上位机通讯模组具有设于pcb板对端的第一通讯单元和第二通讯单元,第一通讯单元连接上位机主板和soc芯片,第二通讯单元可用于连接上位机外设,以便在第一通讯单元同时占用两排并行的上位机通讯接口时,其中一排通讯接口被与第一通讯单元电连接的第二通讯单元转移至pcb板的其他位置,从而达到能够充分利用上位机主控板通讯接口的目的。

16、(5)本实用新型soc芯片和密钥存储器的电源引脚均连接去耦电容,以使芯片和密钥存储器供电稳定,减小其他元件噪声对芯片和密钥存储器产生干扰。

技术特征:

1.一种数据加解密处理模块,其特征在于,包括soc芯片和密钥存储器,所述soc芯片和所述密钥存储器通过pcb板电气连接,且两者基于spi接口通讯;

2.如权利要求1所述的数据加解密处理模块,其特征在于,还包括第一通讯单元,所述第一通讯单元与所述soc芯片基于usb接口通讯;

3.如权利要求2所述的数据加解密处理模块,其特征在于,还包括第二通讯单元,所述第二通讯单元与所述第一通讯单元定义相同的引脚连接;

4.如权利要求3所述的数据加解密处理模块,其特征在于,所述pcb板设有电源电路,所述电源电路的第一通电端连接所述上位机通讯模组,并依次经串联的第一发光二极管和第一分压电阻接地;

5.如权利要求1所述的数据加解密处理模块,其特征在于,所述pcb板设有bootloader控制电路,所述bootloader控制电路具有电源端、接地端和控制端,分别与所述soc芯片对应功能的引脚连接;其中,

6.如权利要求1所述的数据加解密处理模块,其特征在于,所述密钥存储器至少通过数据输入引脚、数据输出引脚、控制引脚、时钟引脚、片选引脚和电源引脚连接于所述soc芯片,且所述电源引脚经第一去耦电容接地。

7.如权利要求1所述的数据加解密处理模块,其特征在于,所述密钥存储器和所述soc芯片设于所述pcb板的相反两侧。

8.如权利要求1所述的数据加解密处理模块,其特征在于,所述pcb板设有保护电路,所述保护电路分别连接所述soc芯片的vdd33引脚和vdd引脚;其中,

技术总结

本技术提供一种数据加解密处理模块,包括SOC芯片和密钥存储器,所述SOC芯片和所述密钥存储器通过PCB板实现电源和数据通信的电气连接,所述密钥存储器用于存储量子密钥,所述SOC芯片集成有加解密协处理器和临时存储单元,所述临时存储单元用于缓存待加密数据,所述加解密协处理器用于将所述待加密数据和所述量子密钥代入国密算法实现数据加解密。本技术通过将用于加解密数据的真随机的量子密钥存储在密钥存储器上,无需SOC芯片内部再集成信号发生器以生成伪随机密钥,能够解决现有技术中数据加密安全性不高的技术问题,同时提高加解密处理速率。

技术研发人员:范犇,田阳柱,徐红星

受保护的技术使用者:长江量子(武汉)科技有限公司

技术研发日:20230707

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!